MIPI介面正加速邁向高速、低功耗設計。由於行動裝置內部子系統設計日益複雜,加上各種物聯網裝置對大量感測器資料蒐集的需求,MIPI聯盟及相關IP、晶片與儀器商正積極研擬更高速的DSI、CSI介面,同時也緊鑼密鼓布局更低功耗的感測器介面I<sup>3</sup>C。

行動產業處理器介面(MIPI)將大舉擴張行動與物聯網裝置應用版圖。手機顯示器、多媒體及資料傳輸介面等子系統功能不斷演進,加上物聯網裝置開始搭載大量感測器,在在驅動MIPI DSI、CSI、I3C及BIF等介面採用需求,以強化主處理器和各個子系統的互連效能,因而引爆MIPI發射/接收器設計,以及相關產品相容性測試(CTS)商機。

行動/物聯網裝置加速採納 MIPI設計/測試商機俏

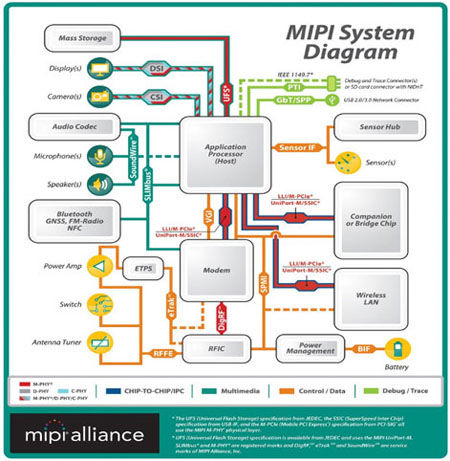

MIPI Alliance行銷總監Peter Lefkin(圖1左2)表示,手機應用處理器運算任務日益複雜,加上各部子系統功能規格持續翻升,相關晶片商和系統業者正紛紛聚焦標準化的MIPI DSI、CSI、DigRF等影像/資料傳輸介面,並加緊與MIPI Alliance合作研擬更高頻寬或支援感測器、電池等子系統的特定介面解決方案(圖2),以持續優化處理器與多個子系統的資料鏈結設計。

|

| 圖1 MIPI Alliance行銷總監Peter Lefkin(左2)認為,MIPI介面將加速進駐智慧汽車、穿戴裝置等物聯網應用。左1為Cadence設計IP行銷部門資深產品行銷經理William Chen,右3為太克MIPI產品部門經理Keyur Diwan |

事實上,手機品牌廠已開始擴大導入2K/4K顯示器、2,000萬畫素以上鏡頭,以及多軸微機電系統(MEMS)動作和環境感測器,因而加重系統大量資料傳輸及運算負擔。對此,Lefkin強調,MIPI Alliance除持續發展專攻影像資料傳輸的DSI、CSI介面,將頻寬從2.5Gbit/s推升至4.5Gbit/s外,更鎖定感測器子系統的資料匯整及傳輸需求,制定新一代I3C介面規範,正式標準可望於今年第三季底定,進而協助處理器和系統廠改善多元感測器資料的傳輸和處理效率。

Lefkin透露,瞄準穿戴式電子、智慧家電和汽車等各式物聯網裝置引進感測器的需求,嵌入式微控制器(MCU)、MEMS晶片商亦積極跟進I3C介面技術布局,未來可望相繼加入MIPI Alliance的行列,共同做大MIPI介面的市場應用版圖。

|

圖片來源:MIPI Alliance

圖2 MIPI介面系統布局示意圖 |

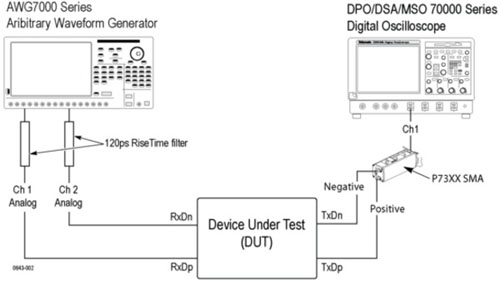

隨著各類型MIPI介面設計升溫,相關發射/接收器及產品相容性測試需求亦將水漲船高。太克科技(Tektronix)MIPI產品部門經理Keyur Diwan(圖1右3)指出,為搶占市場商機,太克已針對MIPI D-PHY、C-PHY、M-PHY等主要測試規範,分別推出一套基於高速示波器、任意波形產生器(AWG)和高精度/低雜訊探針(Probe)的測試平台,協助晶片和系統研發人員加速通過產品驗證。

Diwan強調,太克下一階段將主打可同時支援D-PHY、C-PHY、M-PHY三種通訊協定的AWG測試系統(圖3),從而大幅提高MIPI介面測試效率及儀器投資成本效益,吸引更多處理器和系統廠採納。

|

資料來源:太克科技

圖3 MIPI M-PHY收發器測試架構圖 |

事實上,手機功能快速演進,除顯著驅動各種MIPI顯示、相機、RF和感測器子系統介面導入需求外,更導致主要應用處理器須擴增上述MIPI介面支援能力,以及其他各種高速影音、資料傳輸介面的矽智財(IP)區塊,讓整個系統單晶片(SoC)設計複雜度翻漲數倍,相關IC設計業者正傷透腦筋。

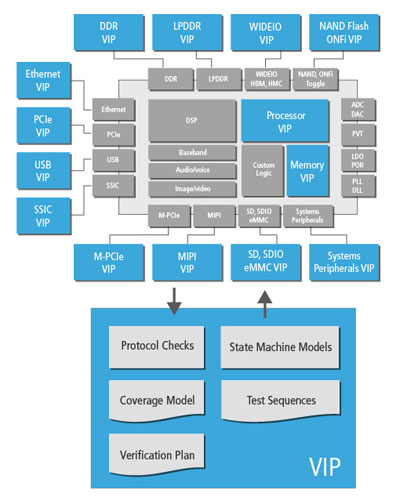

SoC複雜度翻三倍 介面設計/驗證IP需求飆漲

益華電腦(Cadence)設計IP行銷部門資深產品行銷經理William Chen(圖1左1)表示,為提高處理器性能,以及PCIe、通用序列匯流排(USB)、行動高畫質連結(MHL)、eDP(Embedded DisplayPort)介面IP整合度,晶片商正持續加快先進製程導入腳步,但相對的,晶片體積縮小、電晶體密度大增,在IP設計和驗證方面的困難度也隨之攀升,亟須導入更先進的IP解決方案(圖4)。

|

圖片來源:Cadence官方網站

圖4 SoC各個功能區塊的驗證IP需求示意圖 |

觀察SoC IP數量增加趨勢,在65奈米製程世代,SoC平均約整合四十個IP,推進到28、20奈米製程後,內建IP總數已上看一百二十個,在短短幾年間翻漲三倍之多,而其中更有一大部分屬於高速傳輸介面,足見各種介面的設計IP(Design IP)、驗證IP(Verification IP)已是足以影響SoC成敗和上市時程的決定性因素。

William強調,目前晶片商光耗費在IP設計、驗證及整合上,就占用整個SoC開發的70%時間,剩下30%才能用於功能優化,因此正殷切盼望IP供應商能提供更到位的解決方案,以縮短產品上市時程。看準介面設計及驗證IP的需求成長潛力,Cadence近來不斷投資整併傳威(TranSwitch)、PMC-Sierra等擁有資料、影音及記憶體存取介面技術的晶片商,同時也積極和MIPI Alliance、USB-IF,以及乙太網路、PCIe等傳輸介面標準推廣組織合作,因而能建立完整的IP陣容,全方位滿足市場需求。

William提到,以MIPI設計為例,該公司皆能在新介面規格問世後,搶先業界其他對手發布符合規範的設計與驗證IP,可大幅減輕IC研發人員在設計模擬(Simulation)階段,以及下一步的驗證和測試負擔。他更透露,MIPI Alliance將於今年第三季發布感測器介面--I3C標準,Cadence計畫在第一時間跟進推出相關IP;至於近來火紅的Type-C連接器、USB-PD技術,該公司亦已完成IP產品部署。

無庸置疑,高速傳輸介面已成為IP供應商、IC設計業者和系統開發商關注焦點,更是實現下世代行動裝置、物聯網設備的重要技術推手;因此,未來幾年各式高速傳輸介面的標準及規格勢將不斷加速演進,進一步牽動龐大的市場應用及相關軟硬體設計商機。