近年半導體產業興起一波摩爾定律即將失效的論點,究其原因在於無法再繼續縮小電晶體,為了突破這項論點,晶圓或封測廠商試圖從多層堆疊和先進封裝技術的方式來提高電晶體密度,延續摩爾定律穩步發展的可能性,因應此趨勢,蔡司(ZEISS)發表非破壞性3D X-ray量測方案-Xradia 620 Versa RepScan,其能藉此加速封裝開發與良率學習周期。

蔡司半導體製造技術部門(SMT)業務發展總監Thomas Gregorich(圖1)表示,現正處於封裝工程產業引頸期盼的一刻,過去半導體製造產業50年來,大多將製造的重心放在矽晶片提升與微縮,而現在逐步將焦點擺在封裝工程的優化,以提升效能表現。

圖1 圖左至右分別為蔡司SMT業務發展總監Thomas Gregorich、蔡司SMT製程控制解決方案事業群資深行銷總監Raleigh Estrada。

圖1 圖左至右分別為蔡司SMT業務發展總監Thomas Gregorich、蔡司SMT製程控制解決方案事業群資深行銷總監Raleigh Estrada。

行動與高效裝置對於微縮以及傳輸效能的需求不斷提高,使得業界在高密度多晶片架構的許多創新,而這些設計也帶動封裝技術邁入立體化,使得製程的量測技術成為是否能推出新穎且先進技術的關鍵,而這些技術的製程寬容度(Process Margin)通常較低或較難被控制。

Gregorich談到,一直以來晶片產業製造都有關鍵尺寸設定,定義最小電晶體尺寸生產目標及方式,其凸塊連接間距已逐漸從磁球方式轉為銅塊尺寸的設計方式。這也意味著凸塊相連的間距日益縮小,製程越來越難以控制,故在量測開發上需要推陳出新因應新的製程挑戰。

事實上,過去非破壞性影像量測都是手動方式,可看到從1969年都是人為用顯微鏡做顯微鏡量測,至今仍無太大改變。不過未來的記憶體與「小晶片(Chiplet)」技術預計將使封裝互連間距降至20微米或更小,使得互連密度達到每平方公厘2,500至10,000 I/O。這類封裝會需要後段製程(BEOL)般的互連密度與晶圓廠級的組裝良率,基於此就很難用這種以往的手動方式進行量測檢驗。為滿足上述量測需求,蔡司試著透過3D X-ray的方案,重建3D影像資料模擬出虛擬的橫切面,以找出製程失效所在。

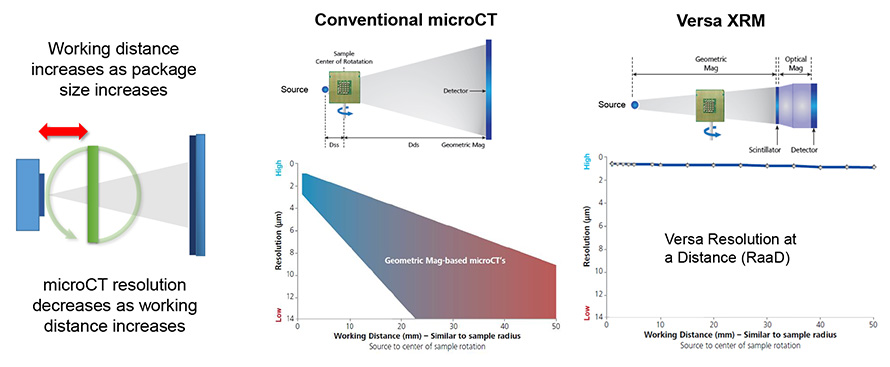

Gregorich指出,市面上有不同量測系統最常見的為microCT做法,其運作方式是將量測光源放在中間,隨著中間尺寸越大,距離光源越遠所呈現的影像也就會越模糊,因此無法呈現完整的量測。此外,物理橫切面除了無法提供3D立體資料之外,還屬於破壞性量測較為耗時,通常也只能處理少量樣本,就統計層面來說,改進製程控制的成效有限(圖2)。

圖2 傳統microCT和Versa XRM比較。

圖2 傳統microCT和Versa XRM比較。

新推出的Xradia 620 Versa RepScan內含蔡司經驗證過的Versa 3D XRM功能,能用次微米解析度以非破壞性方法成像並量測深埋在結構內的晶片,並運用重建的3D資料集擷取出關鍵的3D資訊。除了能執行各種線性及體積量測之外,亦能對矽穿孔與微凸塊、銲料體積與形狀、接合線厚度、晶粒翹曲(Warpage)、3D空隙分析與其他的量測進行各方面的分析,且僅需準備最少的樣本。

蔡司SMT製程控制解決方案事業群資深行銷總監Raleigh Estrada表示, Versa RepScan系列已行銷於全球100個以上的失效實驗室,提供高解析度、定位失效位置等效能,其本身無須進行實體切割就能獲得剖面資料的技術,可說是全球多個失效實驗室導用該方案首要原因。

台灣蔡司顯微鏡RMS & PCS事業部負責人李龍豪補充,Versa RepScan可說是一項高階檢測系統,除了失效實驗室之外,亦廣受先進封裝領域的廠商歡迎,包含美光、台積電與日月光皆有導入該設備。Versa RepScan可以用量測技術提供許多數據化資料,同時研發上亦可用半自動化的工作流程提供可重複的量測,確保不會因橫切面誤差導致成像遺失,並將手動操作導致的量測變異性降至最低。