3D IC的問世因能為摩爾定律解套,進而吸引了不少業界的目光。然而儘管其具有多項優勢而潛力十足,卻仍有諸多門檻亟待跨越,其中包括散熱與良率之議題、工作流程與開發時間之配合,以及最重要的異質領域之整合等。若能一一突破,3D IC始可實現。

摩爾定律(Moore's Law)是系統單晶片(SoC)發展的重要推動力量,沒有摩爾定律,SoC恐怕難以成功實現。但是,SoC卻早在2003年的國際固態電子電路會議(ISSCC)上被英特爾(Intel)的一位架構主管Jay Heeb宣告了「死刑」。

眾所周知,摩爾定律告訴大家電晶體的數目每18個月會增加一倍。但是,目前已有越來越多人相信,摩爾定律應該要結束了,至少目前沒有人討論2x奈米以下的製程。一般認為,2x奈米以下的製程,其股東權益報酬率(Return of Equity, ROE)將不會大於20%。所以,市場研究機構iSuppli在2009年即指出,至2014年時,製程技術會到達18~20奈米,而屆時研發費用將會非常昂貴,且極有可能是摩爾定律中止的時候。

摩爾定律從1965年由高登摩爾(Gordon Moore)提出後,保持了將近45年的有效時光,可謂半導體業的第一定律。但目前,不管是學術界或是工業界已喊出另一個口號:「超越摩爾定律(More Than Moore)」,也就是透過三維晶片(3D IC)的技術來超越摩爾定律。3D IC真的有那麼神奇嗎?產業界是否有能力達成?相關業者須要有哪些心理準備?以下將以幾個非半導體領域的定律,從「非工程師」的眼光來剖析3D IC的發展。

TSV/散熱設計為3D IC良率關鍵

「會錯的事情還是會錯(Anything that can go wrong will go wrong.)」--這是莫非定律(Murphy's Law)其中一個定律。3D IC號稱在單一面積上可以比SoC擁有更高的電晶體密度,但是,以矽穿孔(TSV)為主的3D IC良率一直是測試業界所在意的問題。從目前各個研究單位所公布的矽穿孔大小(約1~5微米),這些尺寸的確比SoC的接觸孔(Contact Hole)或貫孔(Via)大非常多,單純從大小的眼光而言,其良率似乎是值得信賴的。

回顧英特爾中央處理器(CPU)的發展歷史。英特爾CPU的功耗從1971年4004的耗能為0.2瓦到2005年Pentium D最高達130瓦,這種熱能已導致電路可靠度大幅下降,也使得散熱的效能越來越受到挑戰。

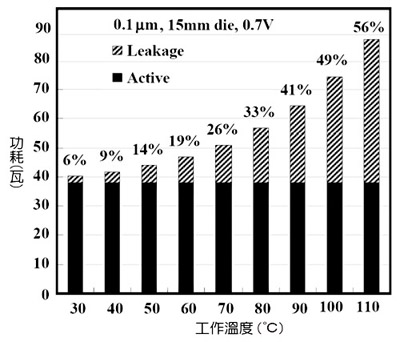

圖1為英特爾針對一個採用0.1微米製程、供應電壓為0.7伏特,尺寸為15平方毫米的裸晶所做的電流與漏電流(Leakage)相對於溫度變化的曲線圖。從圖可知,在晶片工作溫度為30℃時,漏電流的消耗功率只占全部功耗的6%,但是當工作溫度提高到110℃時,漏電流的消耗功率已占全部功耗的56%。

|

| 圖1 工作溫度與晶片功耗變化的關係圖 |

這些高檔的CPU其單位面積的消耗功率高達10~15W/cm2,早已超過氣冷式(Air-Cooling)散熱技術可以處理的極限。更糟的是,從阿累尼亞斯方程式(Arrhenius Equation)公式中可知,當溫度增加10℃,其物質反應速度增加一倍,相對的錯誤率(Failure Rate)也增加一倍。顯見,因為溫度升高而導致錯誤率提升是不會變的,也因此,若3D IC的堆疊沒有良好的散熱策略,錯誤的機率很可能比SoC高。

一般認為,3D IC製程會用矽穿孔,但是,矽穿孔的使用很可能造成系統良率損失,甚至比單一顆晶片的良率損失更嚴重。從一些研究學者發表的矽穿孔量測結果顯示,單一矽穿孔的失敗率,大約可達到十萬分之一(10ppm)的等級。

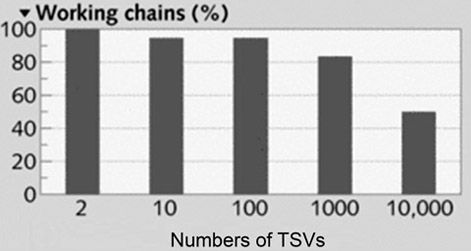

圖2是IMEC與EVG針對不同數目的矽穿孔菊鏈(Daisy Chain)的機械與電器特性做連接性測試,發現矽穿孔連接數目在一百個以下時,其良率都在九成以上,只有當高達一萬個矽穿孔相連時,良率才會低於50%。因此,就如同SoC利用雙貫孔插入(Double-via Insertion)技術來達到可製造性設計(DFM)的做法一樣,3D IC的TSV孔徑尺寸雖然很大,但仍究必須導入冗餘插入(Redundant Insertion)的技術,以便確保可提高TSV製程的良率。

|

| 圖2 TSV Daisy Chain的良率分析 |

緊密合作才能縮短開發時程

「當工作完成前還有一段時間的時候,事情通常會繼續增加(Work expands so as to fill the time available for its completion.)」--這是白京生定律(Parkinson's Law)其中一個定律。這句話的另一個意思是:「時間有多長,工作就會有多長。」如果一個人預期一天要工作16小時,他就會想辦法填滿這段時間。但是若每天只有8小時可利用,他就會設法提升效率,將要完成的工作在這8小時內做完。

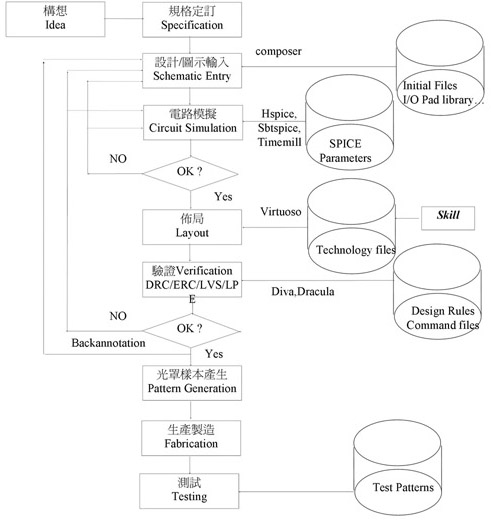

若以這個定律來看SoC設計與3D IC似乎也通。SoC設計複雜度本來就很高,就全客戶(Full Custom)設計而言,若是使用益華電腦(Cadence)的工具,其基本流程如圖3所示。不管是一開始的規格制定(Specification)、設計/圖示輸入(Schematic Entry)、電路模擬(Circuit Simulation),到最後的實體驗證(Physical Verification),每一個階段都需要相當清楚的介面。當每一個階段面臨通過的困難時,須盡力以電子設計自動化(EDA)軟體找出問題,若仍無法克服,就須回到更上一層的階段尋求更好的輸入規格,這種來回往返的流程經常成為許多設計者的夢魘。因此,所有工程師或主管都同意,清楚的規格、溝通與EDA介面扮演極其重要的關鍵。

|

| 圖3 一般Full Custom的設計流程 |

這道理看似簡單,但實際上大部分公司認為,若要盡早完成工作,應該要投入更多的時間。其實,我們並不是每天有那麼多的事情要做,而是有很多的「事「與「人」要在上班的期間溝通,所以只剩下下班時間可以專心做點真正的事情。另一方面,主管也不希望看到部屬下班時間一到就準時下班,主管認為那些經常自願留下來加班的人都是比較有責任感,對公司的忠誠度較高。

若是依照此種工作習慣,要設計複雜度比SoC更高的3D IC恐怕有難度。因為其具有異質整合的特性。當電子產品走向輕、薄、短、小之際,異質整合系統便成為未來半導體產業發展重要方向,不管是微機電系統(MEMS)或系統級封裝(SiP)都能將傳統的感測器(Sensor)、致動器(Actuator)等整合成微米尺度的微小單元,再將這些機電感測器結構與類比、數位訊號和射頻系統處理功能整合到單一晶片中,從而在晶片上創造出一個包含感測、致動、訊號處理、控制等多項功能的完整微型系統。

此時,IC設計的重心似乎不只是電子電路的設計,還需要封裝的專業人士投入,這些人需要機構、熱傳、材料、應力等背景。在這種時代,IC設計人士似乎少了一點舞台,畢竟,封裝的技術涵蓋了真正系統的觀念,對於專長於電子電機的IC設計工程師,每一顆IC頂多也只是SiP中的一個元件罷了。

到了3D IC,則更需要大家一起合作,因為3D IC必須由電子電路的工程師與封裝設計的工程師一起共同工作,彼此聆聽對方的需求與限制,並利用更強大的EDA工具。所以,除了投入大量時間,還得有十八般武藝,其中一項就是可以快速聽取不同領域的專業知識,然後找出大家的共同點。

突破制式思考框架 開創異質整合契機

|

| 圖4 3D IC的太空應用示意圖 |

「在一個層級制度中,每一個人總趨向晉升到他所不能勝任的職位(Every employee tends to rise to his level of incompetence)」--這是彼得原理(The Peter Principle)中的一個定律。這個定律並非探討技術問題,而是著眼於組織管理。按照常態,平時有工作成績的人將被提升到比目前高一級的職位,若是他們可以繼續勝任,就會進一步被拔擢,直到他們所「不能勝任的位置」。所以,組織的悲劇經常在於:每一個職位最終將被不勝任的人所占有;而組織的大部分工作,多半是由「尚未達到不勝任」職位的人們所完成。

拿這個定律來討論,並不是要增加這篇文章的篇幅,而是想討論一個問題:複雜的3D IC系統架構,究竟需要怎樣的系統設計工程師(System Architecture Engineer)?3D IC是異質整合,所以系統工程師不一定是會電子電機背景的工程師,可能是生物工程師、太空工程師、環境工程師或語言學家。

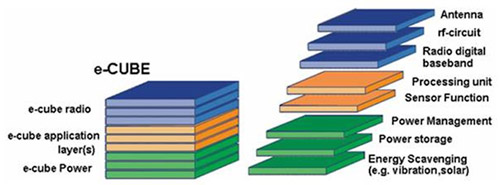

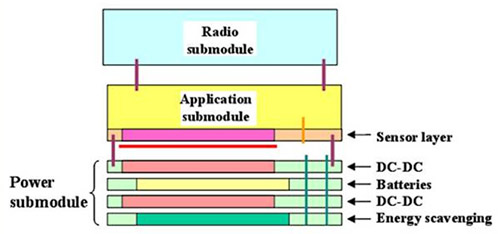

圖4為eCubes網站上3D IC在太空應用的示意圖。圖中在類似火星登陸車子上方的圓點即是由登陸車所噴出的「灰塵」,也就是一顆由3D IC構成的eCubes元件,每一個eCubes元件被放到空氣中去偵測外界的各種參數,如溫度、壓力、氣體等,透過這些無線感測器(Wireless Sensor),形成一個無線感測網路(Wireless Sensor Network, WSN)。這些高度整合的小型化智慧感測器都必須包含感測器本身、讀出電路、無線通訊與電力轉換(Power Scavenging)。而這些感測器都是由MEMS所設計而成。從圖5、6可看出整個模組包含了三個部分,每個部分各有不同的功能層。

|

| 圖5 eCube的各個功能層 |

|

| 圖6 eCube各層的功能 |

很清楚的,到了3D IC設計時代,設計人員若仍一直習慣於在自己的領域思考,沒有所謂的批判性思考或者是另類思考,甚至是借助他人智慧如矽智財,在3D IC異質整合的過程中將難以成功。

(本文作者張嘉華為南台科技大學科技管理研究所助理教授、唐經洲為工研院資通所專案副組長)

| 參考資料 |

[1]. David Lammers , SoCs are 'dead,' Intel manager declares, EE Times, Available At: http://www.eetimes.com/conf/isscc/showArticle.jhtml?articleID=10800893&kc=3681, Dec. 2, 2003

[2]. Arrhenius equation, Wikipedia, Available at: http://en.wikipedia.org/wiki/Arrhenius_equation, 2009

[3]. Kirtimaya Varma,在第三維中設計,EDN Taiwan, Available At: http://www.edntaiwan.com/article-5238-%A6b%B2%C4%A4T%BA%FB%A4%A4%B3%ADp-Asia.html, Oct. 1, 2006 年

[4]. A. Jourdain, B. Swinnen, E. Beyne, and S. Pargrieder, Collective Hybrid Bonding for 3D IC Stacks, Advanced Packaging, Available at: http://ap.pennnet.com/display\_article/346331/36/ARTCL/none/none/1/Collective-Hybrid-Bonding-for-3D-IC-Stacks/, Nov, 2008

[5]. X. Zhang and X.H. Jiang, Redundant Vias Insertion for Performance Enhancement in 3D ICs, IEICE Trans. on electronic, No. 4, Vol. E91-C, Apr., 2008, pp509-519

[6]. P. Ramm and A. Klumpp, Through-Silicon Via Technologies for Extreme Miniaturized 3D Integrated Wireless Sensor Systems (e-CUBES), 2008 International Interconnect Technology Conference (IITC 2008)}, 2008, Jun., pp. 7-9

[7]. D.M. Koen and D.M Piet and S.T. Deniz and B.K. Beyne and E.M. Robert and V.H. Christiaan, 3D interconnect technology for space applications, ESA Round Table on Micro/Nano Technologies for Space location, ESTEC, Leuven Belgium, Oct. 2005 |