隨著邁入資訊連接時代的第三個階段,無線技術的使用方式將會發生翻天覆地變化。第一個階段透過有線電話和基於撥號數據機的早期網際網路來連接家庭和企業。過去幾十年來,通訊網路的發展已經被無線行動技術所取代,地點間的互連也被人與人之間的互連所取代。目前,全球有超過70億台行動設備將38億人聯繫在一起。從地點之間的連接到人與人之間連接轉變的一個典型例子是桌面電話的消失。

由於行動設備和網際網路視訊如Skype等連接技術的出現,桌面電話已經成為歷史遺跡。而下一個趨勢將是物物互連。可以肯定的是,未來10年內預計互連的「物」的數量將至少是人口數量的十倍。

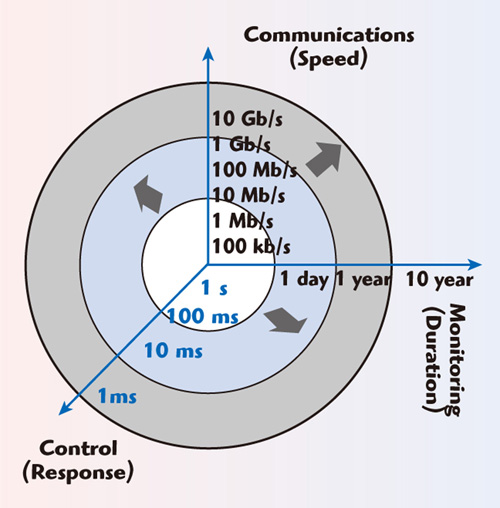

這個嶄新的時代將會催生各種新無線技術來支援定義正處在早期概念階段的第五代(5G)行動通訊標準所需的物聯網(IoT)和底層基礎設施。更高資訊頻寬、更快回應時間(低延遲)且更低功耗的即時無線控制,都是非常有吸引力的系統目標(圖1)。

|

| 圖1 支援IoT無線控制的5G通訊速度和回應時間(延遲)目標 |

圖片來源:德累斯頓理工大學Gerhard Fettweis博士

這些目標給正在開發半導體技術和基礎設施來定義未來5G網路實體層(PHY)媒介、媒體存取控制(MAC)和路由層的設計團隊帶來顯著的挑戰。雖然實現5G和IoT商業化所需的技術要求非常嚴苛,但其經濟潛力和商機非常巨大,因此數10億美元正投入到工業和學術研究中。

四方向分進合擊 解決5G挑戰

5G網路很可能會基於現有的蜂巢式基地台,採用多址無線電接入技術(Multi-RAT)來確保大覆蓋面積、高移動性以及分散的小型單元來提高容量和室內服務品質。這些未來的網路將採用小型蜂巢+巨集蜂巢式基地台組合以及蜂巢資料+Wi-Fi組合,並對Wi-Fi技術投入大量的研究來實現蜂巢資料流程量轉移。雖然目前關於哪項技術將會解決5G挑戰這一問題還沒有完全達成一致,但研究人員正往四個方向研究:

第一個是大規模多重輸入多重輸出(MIMO)旨在大幅增加基地台採用的天線數量,以增大行動設備的覆蓋範圍以及實現高速回程鏈路。

第二是網路緻密化,包括空間(例如密集部署小型蜂巢,透過使用更多節點來實現更大的覆蓋範圍)以及頻譜(利用不同的頻段的更多無線電頻譜)。

第三個研究為針對5G波形旨在透過對訊號和調製技術進行結構性的改進,以提高頻寬利用效率。

而第四個研究方向是,毫米波(Millimeter Wave)頻率將利用新的頻譜(3G∼300GHz),此一頻率範圍曾經一度被認為無法用於商業用途,但現在卻有望提供非常高的頻寬來實現數Gbit/s的資料速率,同時還有望實現極為密集的空間複用來增加容量。每個無線電元件,無論是功率放大器(PA)、濾波器,還是天線,對實現5G/IoT連接都發揮出關鍵的作用。系統性能將要求這些電氣元件作為微型系統運行,並提供前所未有的高水準整合和功能密度。

設計團隊緊密合作 5G開發如火如荼

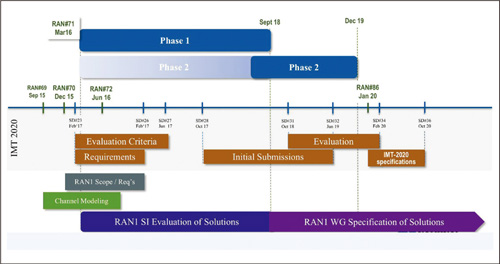

圖2是5G標準規範制定的第三代合作夥伴計畫(3GPP)和國際電信聯盟(ITU)時間表。第一階段希望在低於40GHz的頻段下實現超過100MHz頻寬。第二階段則納入對100GHz以內頻段的研究。如果研究人員要成功完成第二階段的目標,並提交滿足國際行動電信系統(IMT)2020規範的成果,必須從現在開始進行研究。

|

| 圖2 5G標準規範的3GPP和ITU時間表 |

幸運的是,微波和訊號處理技術的進步,比如氮化鎵(GaN)電晶體、新型單晶微波積體電路(MMIC)/Extreme MMIC元件、「新摩爾定律」的異構整合、前端模組/封裝的降低、新型毫米波矽積體電路和先進的天線整合/電子束控制技術等,將有助於實現802.11ax、WiGig等新無線技術標準以及5G相關的遠大目標。積體電路和系統設計的挑戰包括功率放大器的非線性失真、相位雜訊、IQ失衡和高度定向天線設計等。

用於5G/IoT應用的電子元件將納入新的材料和半導體元件,同時基於現有的平台以及模組和子系統等不斷變化的平台實現創新的互連和電路架構。開發和整合這些新技術說起來容易,做起來難。

這一層次的技術整合需要大量的設計團隊和工程學科的緊密合作才能實現。協調設計團隊/學科之間的設計活動需要一種自上而下/自下而上的實用方法,能夠了解整個系統的性能,同時詳細理解物理設計中傳輸高頻/高速訊號的結構之間的電氣交互。高頻元件整合此一設計趨勢正在迫使工程師採用與以往不同的電子設計方法。

統一設計平台做整合 模擬管理設計專案

對於產品開發團隊,5G/IoT機遇帶來的挑戰是如何透過適當的前期規畫、制定切實可行的無線電模組性能參數指標、列出詳細的電路要求、基於電磁(以及可能的多物理場)模擬和早期原型測試的驗證,以及將結果關聯到系統模擬來縮短設計週期和減少故障。對於任何規模的組織,自上而下/自下而上的方法都需要設計工具整合,包括基於代表各個元件(從各種模擬、測量源等)的資料對整體性能有著系統級的理解。

透過系統模擬管理設計專案,有助於指導早期的開發過程,並幫助整合商建立鏈路預算(考慮到沿訊號鏈的損耗和增益)、定義元件規範以及監測整體性能。當電路/電磁(EM)模擬和測量設計細節制定出來後,還須要將其添加進去。可對電路/EM模擬結果及基於測量的結果進行系統級資料管理的設計平台,應該能夠透過工具的交互操作直接瀏覽這些資料。

對於上述過程,研發團隊將使用針對其工藝技術(如代工廠和供應商)的特定資料流程來管理整體開發專案,該流程應整合式軟體/測量所有階段的模擬(如優化、良率分析)、物理設計(如布局、PDK、設計規則)和驗證(如電磁測試)。

電氣設計階段最好採用一個統一的設計平台,能夠將實體層設計(如布局和進程堆疊)和以下功能整合在一起:1. 高頻電路線性、穩態非線性(基於頻率的諧波平衡)和瞬態(非穩態時域);2. 通訊系統行為元件模型、波形源、數位調製;3. EM分析:使用高頻訊號激發類比二維(2D)和三維(3D)結構的電氣特性。當無線電模組緊密整合到一個小巧的結構,就無法通過遠距離和遮罩來防止電磁耦合導致的性能削弱行為,這時無線電模組之間就會普遍存在電氣交互作用;4. 透過良率和容差分析等製造分析,了解製造允許誤差的影響;5. 物理設計工具(例如布局)之間的互通性、製造商/IC晶圓元件建模、測量資料和多物理場驗證。

射頻/微波設計與量測 合而為一加速開發

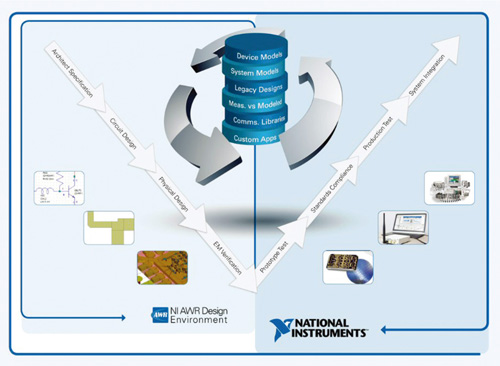

現有儀器商如國家儀器(NI)透過其射頻/微波設計軟體和硬體/軟體測量解決方案提供這種互通性。其AWR Design Environment平台整合了該公司Visual System Simulator(VSS)、Microwave Office電路模擬軟體、Axiem平面EM模擬和Analyst三維有限元素法(FEM)電磁模擬,並可連接Sonnet和ANSYS等公司的協力廠商電磁模擬設備以及Cadence、Mentor Graphics和Zuken等公司的電腦輔助設計(CAD)工具。該平台還還能夠與LabVIEW此一可支援測試儀器控制、資料擷取和工業自動化的系統設計平台與開發環境進行交互操作,從而提供從模擬到原型測試的完整鏈路(圖3)。

|

| 圖3 使用AWR Design Environment和LabVIEW設計平台實現的共用資料模型和設計自動化可加速高頻產品的開發流程。 |

這兩個平台提供的模擬技術整合、系統原型工具和自動化測試設備解決了開發新5G無線技術的複雜難題。設計團隊必須依賴於模擬和原型測試才能保證設計的可靠性。雖然模擬對於設計測試台或原型非常重要,但是在製造之前也常常須要透過測量來驗證假設,並使他人信服設計的可行性。

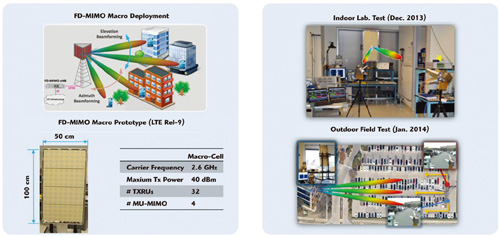

例如,三星(Samsong)研發部主任Gary Xu在2015年德州奧斯丁舉行的NI Week上首次公開展示了一個5G MIMO基地台的全方位(Full Dimensional, FD)原型。該演示由一個小型基地台組成,其中包含FD-MIMO天線陣列和用於類比四個5G終端的四台NI通用軟體無線電周邊(USRP)可重配置I/O(RIO)軟體接收器。展示的核心焦點是三星新推出的3D波束成形演算法技術。

該原型表明,三維波束成形可實現更高的輸送量並且可支援更多的用戶。在演示中,系統採用三維波束成形技術,將速率從一個使用者2Mbit/s提高到四個用戶25Mbit/s。Gary Xu展示了無線電原型工具對於驗證特定系統設計的可行性,具有相當重要的意義(圖4)。

|

| 圖4 基於四個國家儀器USRP RIO軟體接收器實現的三星FD 3D MIMO波束成形原型系統。 |

在模擬端,AWR Design Environment可說明工程師在製造之前開發功率放大器、濾波器、天線、頻率源(即壓控振盪器)、控制電路(即混頻器、轉換器和開關)和互連技術等無線電元件。例如,5G將非常依賴於先進的天線技術。由於毫米波頻率具有高頻寬、低功率要求以及較高的通道損耗,因而須要天線設計採用多個定向波束以及極化分集和控制(如以上例子所示)。相控陣列(Phased Array)是滿足這些要求的主要候選技術之一。相對地,這須要電路模擬和系統環境來支援相控陣列的模擬。

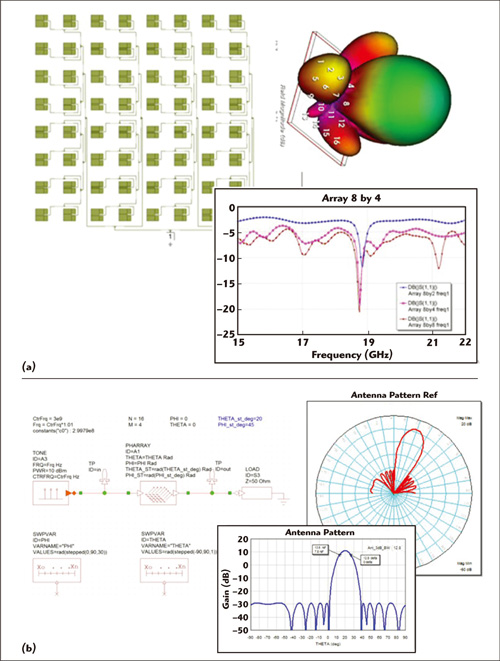

過去,相控陣列先在EM模擬器中進行模擬,然後將所得到的S參數檔嵌入到電路模擬器中來完成設計。積體電路和EM模擬器可讓設計人員了解天線和電路是如何進行交互作用的。特別是陣列埠的阻抗會隨著光束掃描角的變化而變化。而由功率放大器驅動的天線性能會受到埠阻抗的顯著影響。設計人員必須經常在天線模擬和類比電路之間來回穿梭才能精確地模擬這個行為。Microwave Office現在可以自動將這兩種模擬結合在一起。功率放大器會感應埠阻抗的不斷變化,當輸入埠的輸入功率和相位發生變化時,天線會開始掃描波束。除了節省時間和避免錯誤外,設計人員現在還能夠優化電路/天線系統並進行良率分析。EM協同模擬仍對高頻電子產品的開發和互連特性分析發揮了重要的作用(圖5)。

|

| 圖5 貼片天線陣列設計,使用Axiem實現平面EM模擬(a)和系統級相控陣模擬(b)。 |

成功設計實例紛出籠 整合解決方案功不可沒

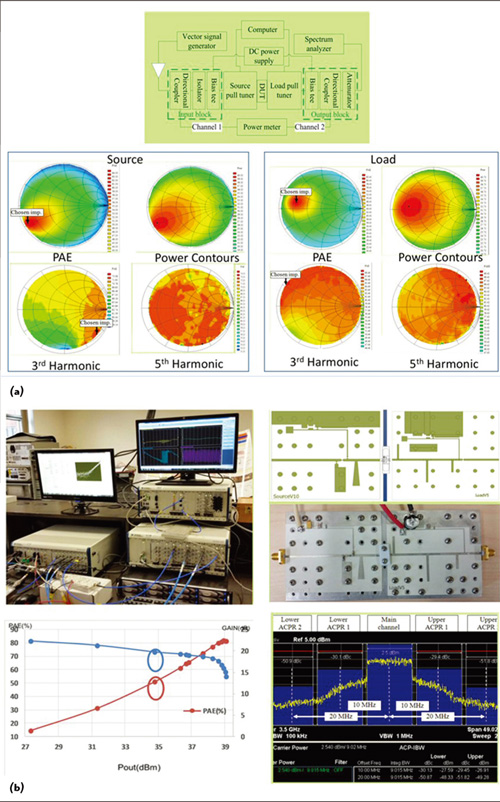

在魁北克瑞姆斯基大學(UQAR)最近開展的一項工作中,Chan-Wang Park博士帶領學生將模擬和測試資料應用於5G設計。設計團隊為5G MIMO多載波訊號開發一個6瓦(W) 1GHz功率放大器。

由於希望在未來能夠線性化功率放大器,該團隊打算使用AWR Design Environment和LabVIEW開發一個伏爾特拉級(Volterra Series)數神經網路預失真或多項式預失真線性電路來校正功率放大器的非線性行為。基頻(Baseband)的數位預失真雖然會增大非線性度,但可由功率放大器的壓縮特性進行補償。

該設計團隊使用Microwave Office、Axiem和Cree GaN電晶體的可擴展高頻模型(來自Modelithics)、導入Focus Microwave的多諧波源和負載拉移資料(Load Pull Data)(用於阻抗匹配和模型驗證)、PXI RF儀器以及LabVIEW,透過詳細的電路/EM協同模擬快速獲得了基於印刷電路板(PCB)的原型測試結果(圖6),一次就成功設計出功率放大器。團隊使用LabVIEW軟體編寫了一個預失真線性化程式,並在賽靈思(Xilinx)Virtex-6現場可編程閘陣列(FPGA)執行該程式,由此開發了一個滿足未來(5G MIMO)通訊系統標準的簡化版解決方案。

|

| 圖6 用於模型驗證和阻抗匹配(基波和三次諧波)的負載�和來源拉移資料和測試裝置圖(a);用於4×4 MIMO的PXIe射頻測量平台(b)。 |

總歸來說,這些可交互操作的平台將給設計團隊提供所需的性能和靈活性來開發高頻電子產品,進而推動5G和IoT的發展。

(本文作者任職於國家儀器)