礙於成本問題,過去廠商仍固守SoC或SiP封裝技術,以達成異質晶片的封裝整合,因此使3D IC TSV技術一直處於邊緣地帶,然而隨著3D IC成本不斷下降,加上以研究機構組成的聯盟持續推動下,3D IC躍升主流之路指日可待。

在前幾期的介紹中,讀者已可了解三維晶片(3D IC)在發展時,市場上各界的考量,3D矽穿孔(TSV)技術的發展,不單只看製程,設備與材料也須要能支援,量產的可能性才能提高,否則以現行主流技術系統單晶片(SoC)仍可應付多種領域的應用時,讓廠商願意付出額外成本,執行TSV作立體封裝的可能性必不會太高。

在不同選擇的TSV規格架構下,所造成的對應製程流程步驟,都須求更進階的設備配合,諸如在形成高深寬比TSV所使用的蝕刻、鈍化與金屬化、填孔、晶圓薄化與處理、對準與組裝、測試與測量等,都將無法再完全延用舊式設備。因此在本期的內容中,將會探討3D IC背後驅動的力量與提供解決方案須面臨的問題,並延伸出未來TSV應用的趨勢與預測,以便讓讀者可了解未來半導體市場,在3D IC當道時,所將形成的初步輪廓,本文將先分析為何需要3D IC。

3D IC TSV成本仍高

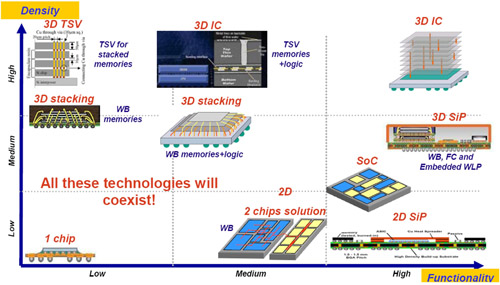

3D堆疊並非全新技術,在摩爾定律(Moore's Law)規範著半導體業的研發數年後,電子元件的功能需求,讓技術的瓶頸極限漸漸浮現,然而,為何要有另外的第三維度?許多專家的看法並不相同,仍有許多廠商仍寧願死守二維(2D)的SoC,也不願及早進入需要額外成本的第三維空間,因此,市場上的封裝技術,漸漸進入戰國時代,許多的技術將並存,並且各有主力廠商可供應相關技術。若從封裝時電子元件可擁有的功能與訊號密度來分,並存的技術可如圖1的矩陣所示,目前主流技術打線接合(Wire Bonding, WB)與覆晶技術(Flip Chip, FC)雖可應用在3D系統封裝(System-in-package, SiP)及立體封裝(3D Stacking),但是在元件密度上,將很快到達極限。另外,以2D的SoC來看,雖然可提供較多功能的整合晶片產品,但在元件密度上,亦將面臨挑戰。因此應用TSV技術堆疊晶片往第三維的方向發展,是封裝技術未來的趨勢,但是並不會完全淘汰其他的技術。如在非高階元件的應用上,由於單價較低,使用加工成本高的TSV方式作封裝,並不易被廠商所接受。

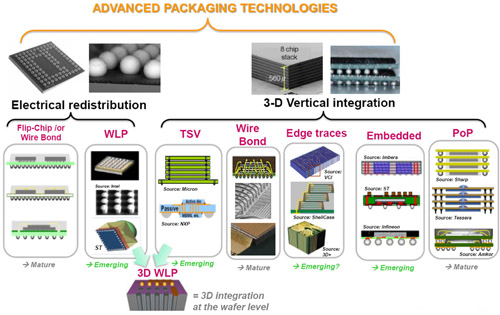

圖1的矩陣及圖2的先進封裝技術圖,可以看出目前可應用於半導體元件作3D垂直整合堆疊的封裝技術,主要涵蓋以下五種技術,包括打線接合、層疊封裝(PoP)、嵌入式(Embedded)、TSV與板邊銅膜導線Edge Traces。

|

資料來源:Yole

圖1 封裝技術矩陣 |

|

資料來源:Yole

圖2 先進封裝技術圖譜 |

其中,以前兩項技術較趨成熟,市場應用占八成以上,而在Vertical Circuit、ShellCase與3D Plus有進行研發的Edge Traces技術,在市場上仍未定調,也因此,相較於其他的技術來看,3D整合封裝的技術,主要以利用晶圓級封裝(WLP)技術搭配TSV技術,才是未來主要進行立體堆疊封裝的主流應用,其可以用來整合IC、邏輯晶片、射頻(RF)、互補式金屬氧化物半導體(CMOS)影像感應器,與微機電系統(MEMS)。

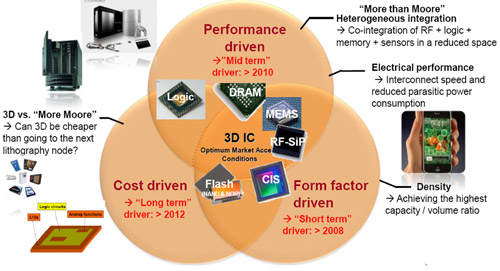

效能/尺寸/成本為3D IC主要驅動力

立體堆疊主要的幕後推手來自於三個部分,亦即3D IC技術發展的市場驅動要素,如圖3所示,主要是由於半導體元件以效能、元件尺寸大小與成本為首要考量,而立體封裝的3D IC則可同時具有這些優勢。若以此三個驅動因素來看,在短期內,元件的尺寸大小是主要的考量,從2008年起,在手機、消費性數位相機等持續追求輕薄短小,但卻也擴展功能的強化,這便是中期的驅動因素,在此階段(稱為More than Moore)強調可整合異質晶片,經由整合不同功能的晶片模組,電子元件的功能便可更加豐富。若拿長期的目標來看,業界要願意投入量產,成本仍是一個首要的考量因素,此階段稱為More Moore。以EMC3D所設定的3年成本目標來看,每晶圓加工成本150美元是一個階段任務,根據2009年EMC3D第四季對成本的估算,120美元已經是個可達到的目標,若是成本能再更低,TSV立體堆疊技術才可進入封裝的主流,也許TSV無需如覆晶技術要到10年,才得以進入主流技術,預估到2015年,全球將會有約10%的晶圓採用TSV,因此TSV進入主流,並不遙遠。

|

資料來源:Yole

圖3 3D IC市場趨動因素 |

研發組織聯盟成3D IC轉機

3D技術的好處,持續表現在TSV製程的成本效益與高良率、超薄晶圓處理可靠度,以及可對晶片到晶圓(D2W)或晶圓對晶圓(W2W)垂直晶圓的整合上,以晶圓接合技術而言,大量的MEMS應用早已發展出來,且已可對200毫米(mm)或更小尺寸的晶圓進行加工,但對於300毫米而言,晶圓接合技術才剛被導入到IC製造。

大約10年前,半導體產業已有能力可以進入300毫米晶圓的製造,以目前全球晶圓加工的產值看來,300毫米的晶圓已占全球IC製造約50%的比例,但當持續往300毫米晶圓發展的同時,以往研發組織卻不願意把錢花在相關的300毫米晶圓工具設備上。

當然有些例外,如比利時微電子研發中心(IMEC)即傾向認為較大的晶圓尺寸並不與新技術發展直接相關,充其量只是會增加生產力,因此對研發組織而言,並沒有即刻性的存在。然而在過去幾個月以來,研發組織開始以聯盟的方式,對3D整合技術的300毫米生產線進行投資,如IMEC、Leti、工研院、ASET、IME、Sematech及Fraunhofer IZM等,都已取得300毫米設備,或宣稱在不久未來會增購進行研發,很明顯地,進入3D IC應用時,研發組織已強烈意識到,若無法提供300毫米晶圓研發能力,可能將會很難再取得業界的合作計畫,舉例來說,Fraunhofer IZM已籌畫可在3D系統中,異質整合不同晶圓技術的200與300毫米的生產線,而此由研發組織帶頭的開放平台,將非常有幫助。

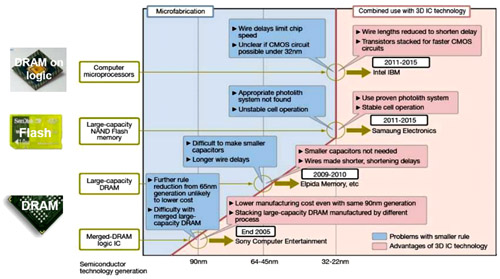

若是以技術的角度觀察目前3D IC市場的應用,圖4探討提供靜態隨機存取記憶體(DRAM)、快閃(Flash)記憶體與DRAM on Logic等應用的記憶體大廠,將會遇到的技術瓶頸,以及預期的解決方式,圖4左邊方框是各種記憶體應用時將會面臨的問題,而右邊方框則是3D IC技術可以提供的解決之道,以DRAM結合邏輯晶片的應用來看,首先會在線寬90奈米(nm)製程之後,面臨是線寬必須縮小到64~45奈米,但成本卻無法縮減,且較難整合較大容量DRAM的問題;而在大容量DRAM的應用,且在64~45奈米製程時,便會有打線距離過長的問題出現。此外,大容量NAND Flash記憶體在2011~2015年間,雖進入到32~22奈米製程,但卻仍沒有適當規格的顯影設備。而在同一技術節點時,電腦微處理器技術會因過長的打線距離而造成晶片速度受到限制,另外,CMOS製程能否提供小於32奈米的線寬,也仍未有解決方案。這些記憶體應用時所將遭遇的問題,可在導入3D IC技術後,獲得解決之道,並依序已由索尼(Sony)、爾必達儲存(Elpida Memory)、三星電子(Samsung Electronics)、英特爾(Intel)及IBM等進入研發。

|

| 圖4 3D堆疊進入市場的契機 |

2010年初時,由SUSS MicroTec所主辦,以及業界夥伴與IMEC協辦的研討會中,強調將於300奈米暫時晶圓接合時使用新的技術選擇,但由於仍有多項問題,若可讓材料與設備供應商一齊與研發組織開發解決方案,則可行性可大為提升,並對於研發組織可突破在3D IC製造的技術瓶頸有顯著的助益。 一直以來,研發組織對半導體業可說相當重要,因此,持續觀察3D IC研發聯盟如何重整業界與公開研究計畫,是掌握產業動向時,非常值得注意的事,尤其在技術遇到瓶頸時,通常是另一進階技術得以獲得轉機的時刻,而從2D到3D,TSV可謂首當其要。

(本文作者依序為南台科技大學科技管理研究所助理教授、工研院資通所專案副組長)