隨著消費者對延長電池使用壽命和強大處理能力的期望愈來愈高,智慧型手機與平板電腦對充電和電池保護功率金屬氧化物半導體場效電晶體(MOSFET)的需求也同時與日俱增。

其中,電池組保護電路模組(PCM)中的共用洩極(Common-drain)背對背(Back-to-back)功率MOSFET能夠對充電/放電進行控制,並且可在發生短路、過電壓、欠電壓以及發生會損壞電器的其他類似電池故障狀況時,發揮保護作用,讓消費者有更佳的使用經驗。

共用洩極功率元件具有非常低的串聯電壓降(In-line Voltage Drop),有助於延長下游電路的工作時間,並且大幅降低將能量從電池轉移至其他電路的功率損耗。對於電器設計人員而言,小巧的尺寸和非常低的導通阻抗可以把電路板尺寸縮得更小,以便增加內部的容積,進而容納體積更大的電池,藉此增加功能性或縮小元件的尺寸。共用洩極功率MOSFET可對流過元件的雙向電流進行獨立調整,而該元件則是電池組PCM電路所需要的關鍵零組件,因此已備受市場矚目。

此外,共用洩極配置也能很好地適應使用晶片背部連接電晶體洩極的普通功率MOSFET元件的基本結構--即將兩個獨立源極和洩極連接布置在頂部表面完成所需的功率控制元件。

通道寬度大幅提升 溝槽式功率元件效能加倍

事實上,溝槽式(Trench)功率MOSFET已成為低壓應用的最佳元件選擇。相較於平面型VDMOS結構,溝槽式MOSFET技術的最大優勢在於它能獲得大很多的通道(Channel)寬度。更重要的是,由於通道寬度增加,通道阻抗得以大幅降低,且隨著元件結構中通道寬度的增加,通道阻抗也大幅降低,即便是這些低壓元件,漂移阻抗也會更加突出。

事實上,最初針對高壓元件而發展的電荷平衡概念,即便對於低壓MOSFET,此一概念也已成為降低漂移阻抗的一種具有吸引力的選擇,但電荷平衡元件的製造會更加複雜,且成本也會更高,因此並非完美無缺。

|

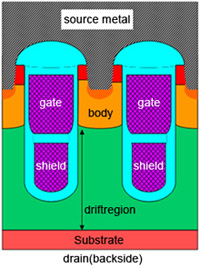

| 圖1 最新一代低壓MOSFET的元件截面和模擬結構 |

本文討論的元件技術將高通道寬度密度與使用遮罩閘(Shielded Gate)溝槽結構的電荷平衡特點相結合,以提供非常低的導通阻抗。圖1為遮罩閘元件結構,圖中可見在閘電極的下面另外含有一個遮罩電極,並包含一個比閘極電介質更厚的絕緣層。

另外,層間電極電介質(IED)亦可將遮罩電極和閘電極分開,由於遮罩電極將閘電極與洩極隔離,因此可大幅減低閘極和洩極之間的電容(Cgd)。不論遮罩電極連接至源電極或閘電極,它在優化元件性能方面都具有重要的作用。此外,由於遮罩電極的場板(Field Plate)效應,因此這兩種方式都能夠提高漂移區域的摻雜濃度。

提高穿擊電壓 有效降低導通阻抗

另一方面,對於給定的漂移區域濃度,增加遮罩電極進入漂移區域的深度能夠改善電荷平衡效應,並得到高於平行平面式(Parallel Plan)的擊穿電壓,提高擊穿電壓將有助於降低R(DS)(ON)。與先前的普通溝槽式技術相比,新的優化元件使得特定的導通阻抗降低50%。

對於雙共用洩極結構而言,源極至源極導通阻抗的主要成分是主元件阻抗、基體阻抗和背部金屬阻抗,主要是由於橫向電流從一個源極流向另一個源極而產生。該元件使用先進的MOSFET技術降低通道導通阻抗和漂移阻抗成分,使得基體阻抗和背部金屬阻抗成為主要的阻抗成分。透過以下一種或者全部三種方式可降低該阻抗:首先是更薄的基體層和更厚的背部金屬層;其次為電阻率更低的背部金屬;第三為縮短第一至第二源極區域之間的距離。

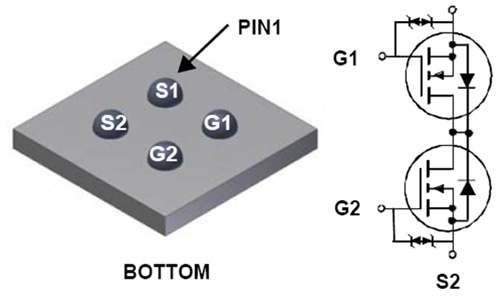

事實上,近年來晶圓級晶片尺寸封裝(WL-CSP)非常受到產業界青睞,因為它為解決上述那些問題提供了較為可行的方案(圖2)。

|

| 圖2 封裝外形和WL-CSP內雙共用洩極MOSFET示意圖 |

WL-CSP封裝由於具有更小的尺寸和較低的寄生阻抗和寄生電感而被廣泛地應用於蜂窩電話等可攜式電子產品中,與傳統薄型小尺寸封裝(TSOP)的接腳型封裝相比之下,WL-CSP封裝設計具有低電容特性,更適用於高頻設備,因此遂成為市場新寵兒。

基體阻抗最小化 WL-CSP封裝獲市場青睞

有鑑於此,新一代功率MOSFET WL-CSP封裝針對可攜式功率應用進行了仔細優化。透過大量的模擬,確保WL-CSP設計的最佳布局與背部金屬層厚度,使元件基體阻抗的損耗最小化。圖3為該元件總體源極至源極導通阻抗的模擬計算結果,該模擬使用了MOSFET個體單元的特定導通阻抗和元件的其他參數。

|

| 圖3 模擬產品Rss(on)與MOSFET元件特定導通阻抗的對照圖 |

為了獲得最低的RSS(ON)及便於用於特定的應用,焊球布局也經過了優化,這些WL-CSP元件的典型製程流程包括在引入晶圓的頂部鈍化層堆積聚合物層,以作為緩衝應力等步驟。然後,凸點下金屬化層(UBM)沉積在用於後續無鉛焊球凸點製程的焊盤上。0.5毫米(mm)或者0.65毫米間距布局可利用現有的電路板裝配設施在標準印刷電路板(PCB)上直接進行裸片表面安裝,並不須使用更加昂貴的高密度電路板。之後是Ball Drop和回焊製程,所有這些都在元件進行最終檢測(以晶圓形式完成)之前完成。

新型封裝最大的優勢在於可靠性。WL-CSP 1.0毫米×1.0毫米,四球0.5毫米間距新封裝已經歷電路板級溫度週期、跌落和反復彎折試驗。

上述這些試驗的目的是為了獲得WL-CSP封裝的電路板級可靠性。試驗遵循現有的工業標準和模擬電路板安裝和現場應用過程中應力條件的最佳實踐。這些CSP元件進行了溫度週期、跌落試驗和反復彎折試驗等三種試驗。溫度週期試驗是為了獲得有關表面安裝元件與電路板連接的焊點的疲勞性能資訊,來自熱裝載的CTE失配引起的週期性應力可能會導致與疲勞相關的故障。

其中,彎折試驗是為了確定安裝元件承受較嚴重衝擊的能力,例如意外的作用力或在搬運、運輸、正常現場操作、意外錯用與產品跌落所造成的運動的突發性改變;反復彎折試驗則是為了進一步確定在週期或者反復彎曲作用之下,電路板級互連的破裂強度是否完善。產品經過試驗後,所有部件皆通過試驗,並且沒有發現任何焊點故障。

隨著低阻抗功率MOSFET技術和優化的WL-CSP技術的發展,半導體業者即可提供具有超小占位面積的解決方案,而這些元件的超低RSS(ON)有助於使總功耗最小化,進而延長電池壽命和使用時間。

(本文作者任職於快捷半導體)