隨著多功能可攜式電子產品的日漸普及,半導體技術的發展多聚焦於微型化、高效能、低功耗、即時上市(Time to Market)等構面的追求。系統單晶片(System on a Chip, SoC)雖然可以符合需求,但是在不同功能區塊的整合上,卻面臨嚴苛的挑戰。

根據摩爾定律(Moore's Law),晶片上可以容納的電晶體數目,約每隔1年半至2年便增加一倍,性能也提升一倍。然而,受限於物理極限,電晶體微縮的製程技術發展日益困難,晶圓廠的建置成本也隨著大幅提升。

市場對低成本的要求是持續摩爾定律最大的風險。考量經濟因素對製程進步的限制,在市場需求追不上晶圓廠可產出的晶片數量的情況下,製程開發勢必放慢腳步。

跳脫摩爾定律框架

跳脫傳統的電晶體微縮,還是可以讓摩爾定律繼續走下去。穿矽孔(Through-Silicon Via, TSV)是一種貫通矽晶圓基底的電氣連結或電極。運用穿矽孔技術的三維晶片(Three Dimensional Integrated Circuit, 3D IC)堆疊,藉由提供晶片間高密度的連線,提高處理器與記憶體間的資料傳輸的頻寬。

所謂的「超越摩爾(More than Moore)」便是倡議以系統應用的概念為出發點,不應受限於執著在電晶體微縮技術的摩爾定律,而更應該將其他科技進行異質整合。由美、台、日、韓、歐等半導體工業協會所贊助的國際半導體技術藍圖(International Technology Roadmap for Semiconductors, ITRS)公布一分「超越摩爾」白皮書,為其成員提出相關技術發展的指標與方向。

這分白皮書提到半導體產業要跳脫傳統的循環模式,進而提升到可以超越摩爾定律的新循環模式,重點已不只在電晶體的微縮,而是要從系統層級、技術層級、電路層級到元件層級導入全面性的創新。這些創新包括前段製程(晶圓製造)與後段製程(封裝技術)之間的整合技術。

現在「更多摩爾(More Moore)」被定義成數位功能(邏輯與記憶儲存)元件最小尺寸的持續微縮,用以改進密度(降低單位成本)與效能(速度、功率);「超越摩爾」則是以不同方式提供附加價值的多功能元件的整合,而不必要隨著摩爾定律微縮。

三維晶片技術優勢明顯

|

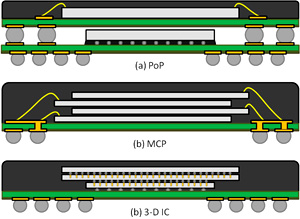

| 圖1 三維整合的技術應用 |

這裡所要介紹的三維晶片技術是指利用穿矽孔連接、晶圓薄化與晶片接合,將傳統二維(2D)平面晶片轉變成立體堆疊的技術。由於它能夠有效地利用空間並縮短傳輸的距離,提供極低電阻連接,因此三維堆疊晶片技術能在輕薄短小與價格的要求下,提供多功能元件的整合的優點。

不過,在垂直方向堆疊不同功能的晶片畢竟是一種跳躍式的技術思考,為使晶片能夠正確堆疊與相互連接,從晶片設計、晶圓製造到封裝與測試都比以往更需要嚴謹的規範。廣義的三維整合的技術應用,約略可以分為三類(圖1):

| ‧ |

|

| |

封裝堆疊(Package Stacking)是將個別晶片封裝後再進行堆疊連接。熱門的電子產品iPhone、iPad內的處理器與動態隨機存取記憶體(Dynamic Random Access Memory, DRAM)的封裝層疊(Package on Package, PoP)即是此技術商品化的應用。其好處是產品良率高、成本低,但是封裝後體積較大,難以應用於真正需要微型化的晶片組合。 |

| ‧ |

|

| |

晶片堆疊(Die Stacking)則是將晶片薄化後進行堆疊,然後用打線(Wire Bond)的方法將訊號連接。目前廣泛應用的Micro SD卡的多晶片封裝(Multi-Chip Package, MCP)即採用此方法。其優點是技術成熟、成本低,但因打線、磨薄及黏合材料等限制,在厚薄度和效能等方面仍有進步空間。 |

| ‧ |

|

| |

三維晶片則是指透過穿矽孔將晶片正面的訊號傳導到背面,使得其他晶片可以與之進行堆疊連接。由於堆疊的晶片間訊號的相互傳遞不必經由外部的導線,因此封裝後整體的尺寸較小,同時也因為訊號傳輸路徑的縮短,訊號的延遲現象可以改善,使系統運作的效率提高,功耗也可以隨著減少。 |

發展三維晶片技術已經成為目前半導體產業技術發展的一股新趨勢,究其因主要有以下數項:

| ‧ |

|

| |

為了提升效能,傳統晶片的做法是在二維平面上增加電晶體數目,導致晶片面積必須變大,但是高度卻不會改變;而三維晶片則是將薄化後的晶片在垂直方向進行堆疊,讓相同面積下的電路密度可以提高,封裝後的尺寸將可變小,這項優點使電子產品可以設計的更為輕薄短小。 |

| ‧ |

|

| |

為了增添功能,傳統晶片的電晶體數量不斷地增加,造成晶片的複雜度越來越高,總導線長度也越來越長。這些導線所造成的訊號延遲與功耗的增加,將會直接影響晶片的效能。三維晶片中的部分導線走垂直方向,因為薄化後單一晶片的矽基底(Silicon Substrate)厚度是數微米(μm)至數10微米,透過穿矽孔,兩個點之間的導線長度可以大幅度的縮短,這也意味著晶片的效能與功耗都可以得到相當程度的改善。 |

| ‧ |

|

| |

|

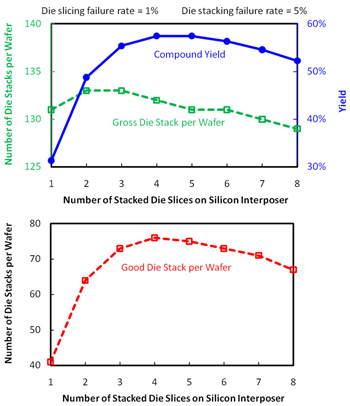

| 圖2 分拆晶片再組合的最佳化 |

將原本在相同矽基底上的電路區塊分拆成數顆晶片,然後使用堆疊的方法予以重建。因為可以事先針對個別的晶片進行測試,只有已知良裸晶(Known Good Die, KGD)才會被選用來堆疊。相較於未切割的版本,若在失敗率(Failure Rate)受到控制的條件下,複合良率的提升也許可以產出更多良好的堆疊,並足以支付三維整合所需要的額外費用。賽靈思(Xilinx)的堆疊式矽互連(Stacked Silicon Interconnect)技術使用矽載板(Silicon Interposer)承接以覆晶(Flip Chip)方式黏貼的現場可編程閘陣列(Field Programmable Gate Array, FPGA)的晶片切片(Die Slice)。切片的數目是最佳化的參數,以下舉例說明。圖2展示一顆2.18公分(cm)×2.08公分的晶片,切割成一至八等分,所對應的複合良率、可用的堆疊數與良好的堆疊數(上述兩者的乘積)。這裡假設每次切割的失敗率為1%,每次堆疊的失敗率為5%,得到四等分為最佳的結論。 |

| ‧ |

|

| |

|

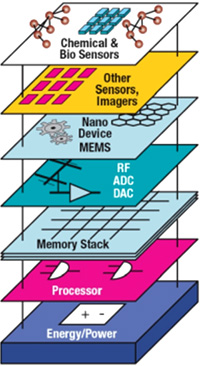

| 圖3 三維晶片異質整合的極致願景 |

整合不同類別的功能一直是系統晶片發展的方向,邏輯製程的內嵌記憶體(Embedded Memory)與混合模式(Mixed-Mode)元件是過去成功的例證。為了在單一晶片實現這些功能,往往需要標準製程之外的步驟,增加光罩的成本與生產的時間。當製程不斷微縮時,除了製程的提供者對這些元件重新開發與驗證,製程的使用者也必須針對其設計平台再次調校,尤其是類比電路的部分,因為自動化的程度低,更顯得耗時費力。三維晶片提供一個異質整合的方案,使用者可以針對不同功能的電路方塊選擇最適合的製程製作晶片,最後再將所有晶片透過穿矽孔進行堆疊。

異質整合還不單單局限於矽晶圓,也可以包括其他材料的晶片,大大地擴展系統堆疊(System on a Stack, SoS)的領域。圖3可說是三維晶片的異質整合一個極致的願景。將處理器、記憶體、類比電路、微機電(MEMS)、感測元件、電源管理單元,甚至是晶片電池與化學或生物感測晶片全部利用最適合的製程製作後,再使用三維堆疊技術整合起來。不過,這個時候穿矽孔的名稱就不怎麼適用,也許穿晶片孔(Through-Chip Via, TCV)或穿晶圓孔(Through-Wafer Via, TWV)會更恰當些。事實上,這些也都是文獻裡出現過的名稱。 |

三維晶片布局 各國方向大不同

全球多數的半導體廠商都認知,穿矽孔與堆疊是封裝或製程的進程,但是在三維晶片的布局方面則各有不同。

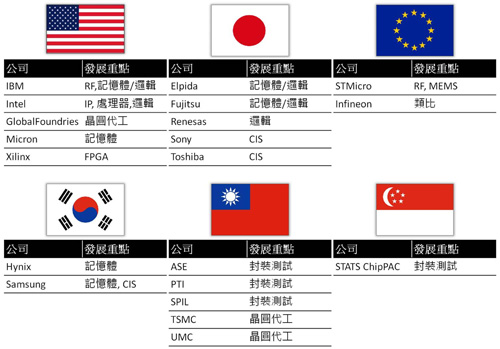

目前,日、韓廠商以記憶體產品為先發性的應用發展方向,美國廠商在意邏輯與記憶體晶片堆疊,台灣廠商則是以晶圓代工廠如台積、聯電以及先進封裝廠如日月光、矽品、力成等配合客戶需求發展偏向三維晶片的封裝技術。歐系廠商則傾向消費性電子等應用領域(圖4)。

|

| 圖4 全球主要半導體廠商在穿矽孔三維晶片的布局概況 |

整體而言,全球在技術布局的發展上,主要鎖定現在及未來市場已大量應用或有潛力的記憶體與邏輯這幾項領域。

國外業者爭相競技

東芝(Toshiba)在2007年底推出的互補式金屬氧化物半導體(CMOS)影像感測器模組,首先在正面受光(Front-Side Illumination)的感測器晶片上使用穿矽孔將輸出入埠聯通至晶片的背面與封裝基板(Package Substrate)連接,宣稱可以減少模組的體積55%與面積36%。

其他國際主要的影像感測器廠商,如意法半導體(STMicroelectronics)等,陸續採用穿矽孔技術進行量產。對正面受光的感測器,穿矽孔只是封裝的一個選項,但是對背面受光(Backside Illumination)的感測器,穿矽孔就成為必要。

東芝與三星都使用多對一的穿矽孔連接方式,而索尼(Sony)與豪威(OmniVision)則採用背面開孔,將接合墊片(Bond Pad)暴露出來打線。

影像感測器純粹是穿矽孔技術在封裝上的應用,並不涉及晶片堆疊。真正的三維晶片量產最可能是記憶體堆疊。

三星早在2006年4月就曾經對外公布穿矽孔堆疊的快閃(Flash)記憶體,使用八顆2Gb晶片構成16Gb容量的封裝。但是即便到現在,穿矽孔僅用來取代打線是否為適當的應用還有爭議。

三星在2010年12月又對外公布穿矽孔堆疊的8GB DDR3 DRAM模組,使用兩顆2Gb晶片構成4Gb容量的封裝;2011年8月再對外公布穿矽孔堆疊的32GB DDR3 DRAM模組,使用兩顆4Gb晶片構成8Gb容量的封裝。

爾必達(Elpida)也在2009年8月發布新聞稿,表示已經開發完成以銅為穿矽孔的三維堆疊DDR3 DRAM,使用八顆1Gb晶片構成8Gb容量的封裝;之後又在2011年6月發布新聞稿,表示已經開始送樣穿矽孔堆疊的DDR3 DRAM,使用四顆2Gb晶片構成8Gb容量的封裝。

這類產品因為其應用上的需求,封裝都有尺寸上的限制,因此幾乎都是以最先進的製程製作,而且現在各種電子產品都需要大量的記憶體作為資料儲存或計算暫存之用,若製程無法進一步微縮,增加使用記憶體容量將等於增加產品的體積及功耗。將記憶體晶片使用三維堆疊方式整合後,將可以提高其存取速度並降低其功耗。

國內研發能量以晶圓/封測為主

國內在製程技術的發展方面,包括台積電和聯電,均已經將三維晶片相關製程列入未來量產的計畫中,如圖5所示。雖然也有日月光、矽品及力成等封測廠投入三維晶片相關技術的研發,但是還未觸及供應鏈的垂直整合。

|

| 圖5 台積電、聯電在穿矽孔三維晶片製程發展的規畫 |

在市場應用未普及、製程技術與設計自動化(Electronic Design Automation, EDA)工具未成熟、供應鏈未建立之際,國內的IC設計公司普遍缺乏比較積極的作為。

即使如此,因為三維晶片的設計與測試需要系統層級的規畫,儘早預備仍然應該對業者會有好處。相對於國際IDM大廠如三星可以選定單一產品如DRAM整合三維晶片的製程、設計與封測開發,國內推動三維晶片的過程著實艱辛,需要更多設計業者的投入以提供產品驗證及獲取實際經驗。

工研院資通所鴨子划水

工研院的晶片中心從2008年開始矽穿孔三維晶片設計與測試技術的開發,起初是以既有的電子設計自動化工具作為實體實現方式,顯然受到諸多的限制。

到了2010年初,晶片中心與資通所合併後,矽穿孔三維晶片的研究仍然繼續而且擴大投入資源。在今年,它已經是結合系統整合、軟體發展、模型建立與實體實現等面向的大型關鍵計畫。

雖然各界對於三維晶片的進程有許多不同的預期,但是共通的看法卻是:在半導體製程的尺寸微縮日益困難的考量下,堆疊晶片似乎是不得不然的選擇。

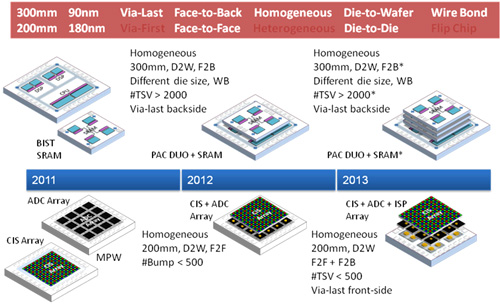

因此,工研院資通所制定兩個測試載具的開發時程,如圖6所示,目的在展示三維晶片實現的流程與可能的應用。工研院資通所專注於記憶體/處理器以及影像感測器/處理器堆疊的特定應用,而這將是一個漫長的開發與持續改進的過程。

|

| 圖6 工研院資通所的三維晶片測試載具發展藍圖,上圖為處理器與記憶體堆疊,下圖為影像感測器系統堆疊。 |

工研院資通所在去年5月首次以全光罩在八吋0.18微米製程下線,並且邀集學界參與部分晶片的設計,這可以算是國內第一次三維晶片多計畫晶圓(Multi-Project Wafer, MPW)共乘。但是到了11月僅取得少數失敗的樣本。

|

| 圖7 晶片對晶圓堆疊(只有部分位置進行接合) |

今年初,工研院資通所再投入一批晶圓,並於6月與8月分別得到新的樣本,期盼解決之前在製程上遭遇的問題。這兩批樣本皆是以晶片對晶圓(Die to Wafer)的方式接合(圖7),但是良率極不穩定,顯示製程仍然有非常大的改進空間。工研院資通所預訂於10月底再以全光罩在十二吋90奈米製程下線,同時也透過經濟部半導體產業推動辦公室的三維晶片論壇,邀請學、業界的共同參與。

(本文作者為工研院資通所設計自動化技術組技術組長)