在過去幾年中,具有高畫質視訊顯示器的產品大量增加,有些產品採用整合式的設計,有些則採取外接螢幕的方式來顯示高畫質內容。不論這些高畫質視訊顯示器是以整合或是外接的形態出現,原始設備製造商(OEM)都期望能夠利用標準的平面顯示器及介面技術來降低產品的成本,並希望能確保其所使用的零組件在產品的生命週期中不致發生停止供貨的意外。

因此,介面設計必須對這種挑戰做出回應,而平面顯示器驅動器如何降低成本,並確保長期供貨無虞,遂成為一大關鍵。利用低成本現場可編程閘陣列元件(FPGA)來充當硬體平台,將是一種可行 方案。

在消費市場上,平面顯示技術的增長有助於統一介面選擇和降低成本。目前高畫質顯示器上常見的介面,除了分量視訊介面(YCrCb)仍屬於類比技術外,大多數都已經改採數位技術,諸如數位視訊介面(DVI)和近年來已成為市場新主流的高畫質多媒體介面(HDMI)。

消費者的家庭影院市場爆炸式的增長,為DVI標準帶來了更多新的需求,然DVI標準有其先天限制,例如其連接器過於龐大、無法妥善支援數位版權管理(DRM),且缺少對單聲道或多聲道音訊的支援。為滿足這些新的需求,HDMI標準遂應運而生,其所使用的基本訊號傳輸大致與DVI相同,但支援較小的連接器、頻寬更高(可支援的解析度達1,080p),並支援DRM和八通道音訊傳輸。

由於這兩項技術有許多相似之處,因此平面顯示器製造商為提升系統設計的整合度,已開始研究將這兩種技術整合在同一台系統產品上。這個趨勢為低成本FPGA帶來新的應用契機。

DVI/HDMI標準相似

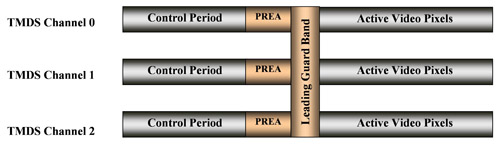

HDMI規範是可以傳輸和接收未壓縮數位流的音訊/視訊標準。它可以將視訊和多聲道音訊組合至單一的數位連接,去除了多條線路連接及相關的成本。對於沒有音訊要求的1,080i解析度顯示應用,HDMI訊號傳輸與DVI是向下相容的。 DVI和HDMI是基於稱為最小化傳輸差動訊號(TMDS)的訊號傳輸技術。TMDS也有類似電流模式邏輯(CML)的實體訊號傳輸電平。一個簡化的HDMI鏈路方塊圖如圖1所示。

|

| 圖1 HDMI收發架構簡圖 |

HDMI介面是一種帶有三個TMDS通道的遮罩電纜。其預設的配置是紅綠藍(RGB),每個通道傳送一種顏色。但與DVI不同的是,HDMI亦支援亮度及色度的分量傳輸,如YCbCr 4:4:4和4:2:2兩種模式。此外,這三條TMDS鏈路亦可傳送多達八個音訊通道。

除了上述音訊與視訊訊號外,HDMI的傳輸鏈路中還包含以1/10X TMDS位元率傳送同步時脈訊號的功能,並採用額外的線路來傳輸延伸顯示辨識碼(EDID)。此外,HDMI亦整合了輔助控制功能,如熱插拔檢測和EDID介面的電源和接地。

因此,一個HDMI介面中總共有二十九條連接鏈路,其訊號傳輸距離則受到接收器恢復訊號的功能限制。為了保證接收器能恢復訊號,對內偏移不應超過在HDMI規範中所定義的值。在規範1.3版中定義了以下限制:在接收連接器中對內偏移的最大容許值為0.2 Tcharacter+1.78ns。其中Tcharacter表示傳輸(10×Tbit)一個字元的時間。例如,若要以1Gbit/s的速率傳輸資料,則其Tcharacter即為10奈秒,因此對內偏移的最大值不可超過3.78奈秒。

HDMI鏈路在操作時有以下三種模式,分別是視訊資料週期、資料隔離週期和控制週期。收發器會在資料週期傳送有效的視訊,而在傳輸資料隔離週期傳輸音訊和輔助資料,傳輸時使用一系列的 封包。

|

| 圖2 HDMI接收器操作模式 |

在任何視訊或資料週期之間,則為控制週期。每個視訊資料週期開始時,有一個緊隨保護頻帶(Guard Band)的前同步訊號,針對從控制週期到視訊週期的過渡,提供穩定的指示。前同步是八個連續的預定義字元,分別為10'b1101010100、10'b0010101011、10'b0101010100和10'b1010101011。保護頻帶是針對每個通道的兩個連續的獨特字元,通道1為10b1011001100、通道2為10b0100110011、通道3則是 10b1011001100。

FPGA取代HDMI/DVI收發器好處眾多

DVI和HDMI的收發介面通常用特定應用標準產品(ASSP)來實現。本文提出了一種採用FPGA替代的解決方案。

採用FPGA替代方案的優勢主要在於提升整合度,藉此節省電路板面積、降低功耗,進而節省系統設計的成本。此外,由於FPGA所使用的製程技術通常走在業界最尖端,因此相較於目前市面上眾多仍採用0.18微米製程的收發器元件來說,在成本跟功耗方面的優勢更加顯著。

HDMI介面的終端應用裝置日益多元化,亦提升了系統設計人員採用FPGA的意願。舉例來說,FPGA的工作溫度在選擇上通常比ASSP來得更為寬廣,例如許多FPGA供應商均可提供滿足工業與汽車應用需求的寬溫元件,但絕大多數的ASSP通常僅能在商業溫度範圍內操作,這會使得產品製造商在開發汽車娛樂系統或工業級的顯示應用裝置時遇到不少的挑戰。

最後,元件本身的供貨時間長短,有時也是系統設計人員所關注的焦點。目前市場上大多數的DVI收發器元件是針對個人電腦(PC)應用開發的,但由於DVI介面本身很適合與其他ASSP整合成單一元件,因此隨著時間日久,許多市場上原有的獨立DVI收發器元件都已面臨停止供貨的狀況,若某一系統設計原本採用這類獨立元件,便有可能出現斷貨危機。但若利用FPGA平台來開發,就不會有這層疑慮,因為FPGA的設計是可移植的。

以FPGA為基礎的參考設計,還能夠實現一些深具創意的應用設計。舉例來說,設計人員可以將既有的7:1 LVDS顯示驅動器轉換至DVI;在接收端,用接收到的HDMI資料實現一個HDMI擴展器,然後將它格式化並通過另一種媒介傳輸,如光纖或第五類纜線(CAT5)。

另一種應用則是高畫質序列數位介面(HD-SDI)到DVI的轉換,或反之。針對圖形疊加、畫中畫和多螢幕應用,HDCP協議的許可證可以進一步處理和管理音訊和視訊資料流程。

參考設計加速取代效應發酵

但不可否認的是,利用FPGA來實現DVI/HDMI整合設計,雖然理論上能為系統設計製造商帶來上述優勢,但FPGA硬體平台本身的操作頻率,將是其性能可否與ASSP媲美的關鍵。因為FPGA的核心運作速度通常較ASSP緩慢,但此一缺陷已隨著半導體製程技術演進而有所改善。

此外,FPGA本身的功耗也是一大問題,有些標榜高性能、大容量的FPGA,其功耗與成本相當可觀,不適合用來取代HDMI/DVI收發器標準產品。因此,低成本、低功耗的FPGA在這波取代風潮中,扮演了相當重要的 角色。

另一個不容忽視的關鍵,則是FPGA供應商所提供的HDMI/DVI參考設計。因為系統製造商不一定熟悉晶片開發的流程,且晶片設計本身即為一高度專業的技術,有其門檻存在,因此參考設計無疑加速此一趨勢發酵不可或缺的關鍵。近來便有FPGA供應商針對DVI/HDMI介面提供完整的參考設計,以方便系統製造商進行導入。

在硬體(FPGA元件)與軟體(參考設計)的互相搭配下,目前系統製造商已經可以很容易地利用內建多路SERDES收發器的FPGA,實現資料速率可達250M~3.125Gbit/s,且無過採樣(Oversampling)情況的HDMI/DVI收發器。

有些供應商所提供的方案,甚至針對HDMI/DVI所使用的TMDS訊號傳輸構建了一個獨特的介面。在DVI/HDMI電纜中,TMDS訊號是有一個外部時脈的源同步訊號,因此在FPGA內建的SERDES中,應具備恢復並產生合乎TMDS資料和格式要求的訊號的能力。這是對FPGA內建的SERDES的一大考驗,特別是其動態範圍性能。

FPGA實作剖析

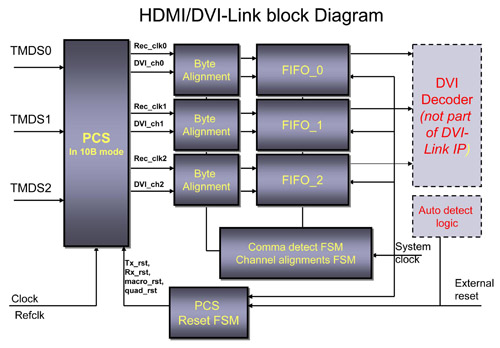

以目前的參考設計平台來看,這些設計挑戰均已有解。在接受端,FPGA可利用其內建的SERDES恢復TMDS訊號。透過FPGA中SERDES內的時脈和資料恢復(CDR)電路完成這個處理。這個CDR電路會將每個串列的TMDS通道轉換成10位元格式,並在資料封包中添加同步時脈,再傳送至FPGA介面。然後在FPGA中進行資料處理達到HDMI標準所要求的同步規範。

同步要求可以分成三個層次來看,分別是位元組對齊的10位元同步、通道調整與多通道對齊。在達成同步要求後,HDMI /DVI收發器還應具備自動檢測運行中的資料流程的解析度(480p、720p、1,080p或1,080i)的功能,並調整物理編碼子層(PCS)參數,以保證顯示螢幕在這些解析度之間動態切換時,其運行能夠最佳化。針對傳輸方向,沒有必要進行位元組和通道對齊。10位元模式的PCS是用來使資料串列化,並與液晶顯示幕通訊。

以本文的實作範例來說,當CML SERDES輸入(圖3的接收訊號流)收到TMDS三個通道的訊號(0、1,和2)數據時,由於DVI/HDMI的訊號不使用標準的8B/10B編碼,因此SERDES後的PCS被設置成10位元模式(旁路)。TMDS訊號傳輸亦使用對本協定唯一的四個對齊的字元,不同於8B/10B方式。

|

| 圖3 HDMI/DVI鏈路方塊圖 |

串列器與SERDES的CDR傳遞10位元的原始資料,FPGA進行位元組對齊。DVI/HDMI鏈路連接可以多個不同的頻率發送資料,自動檢測邏輯用來檢測正在傳送的是哪種解析度,並配置PCS,以便在SERDES鎖相環中實現鎖定。

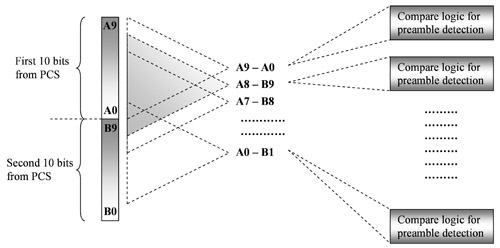

要在FPGA平台中傳輸10位元資料,上述定義的三個步驟(位元組對齊、通道對齊、多通道對齊)是不可或缺的。位元組對齊的設計,可確定10位元資料位元組的開始和結束。

在FPGA結構中,可利用有限狀態機(FSM)來完成這一任務。把資料流程的第一個和第二個10位元組合在一起,形成一個20位元的匯流排;然後分解至9位元、10位元匯流排。

在這一階段,資料與對齊的字元進行比較,當字元順序發生了八次(稱為單通道對齊),同步訊號有效。狀態圖如圖4所示。

|

| 圖4 同步狀態圖 |

同步檢測之後,對齊資料的位元組寫入先進先出匯流排(FIFO)。當所有三個通道都完成了通道對齊,就可以寫入FIFO,至此通道對齊的任務就結束了。在這一階段,FPGA將等待直到FIFO處於半滿狀態,並在同一時間(多通道對齊)對三個FIFO進行讀取操作。這將保證三個通道對齊,並完成同步。

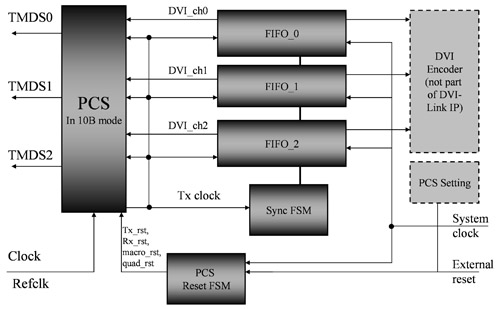

在傳輸的過程中,FPGA內建SERDES的鎖相環預定義的範圍為:Low、MedLow、Med、MedHigh和High。設計人員可利用SERDES用戶端介面(SCI)匯流排,針對這些範圍進行動態配置。

因為顯示器須顯示的數位內容可能有各種的解析度,因此,為了滿足不同的輸出率需求,DVI/HDMI參考設計必須有SERDES組。例如,若應用需求為一個可支援720p解析度的HDMI顯示介面,則此一介面設計的通訊頻寬即須達742.5Mbit/s,SERDES PCS亦必須設置在適當的範圍,如在本文範例平台中,須設定為MedLow。

顯示的資料是放置在一個由DVI/HDMI參考設計定義的FIFO中,同步從三個TMDS的通道中讀取資料。然後將FIFO的資料移至PCS,再用SERDES進行傳輸。PCS設置成10位元模式,串行輸出FIFO的資料。在這一階段,採用合適的時脈,資料將被轉換為新的TMDS流,使接收器恢復訊號,如果配上顯示器,就會出現所欲輸出的內容(圖5)。

|

| 圖5 DVI/HDM傳輸原理圖 |

設計驗證不容偏廢

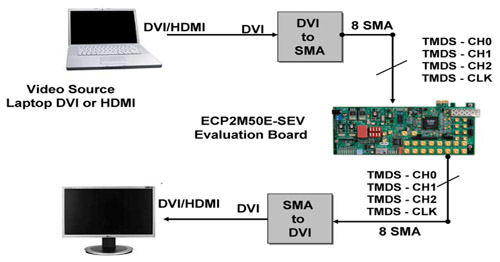

當設計人員依照參考設計,利用FPGA開發出整合HDMI/DVI收發器功能的單晶片設計後,即可將設計移植到測試電路板上進行功能驗證。一個典型的展示和測試配置安排如圖6所示。

|

| 圖6 HDMI/DVI整合設計驗證配置 |

設計人員可利用DVI或HDMI轉DVI纜線,從筆記型電腦的介面得到DVI/HDMI介面的資料流程。接著由DVI至SMA介面卡將DVI連接器轉接成SMA,再利用SMA電纜與評估板相連接。當訊號到達FPGA時,將進行處理並傳送回TX SERDES通道。然後透過SMA電纜,將整筆傳輸資料送回到電路板上的SMA至DVI適配器,並最終在顯示器上進行比較。

在本實作範例中,FPGA整合了用來接收和發送三個DVI TMDS資料流程的代碼,並在FPGA內完成位元組對齊和同步邏輯,以及將資料存入FIFO。在傳輸方面,FPGA從FIFO中取得資料,以10位元的模式直接傳送至SERDES。設計確保在FIFO中三個DVI/HDMI通道完全 對齊。

FPGA為HDMI/DVI應用帶來新契機

從本文的實作範例可知,在低成本、低功耗FPGA方案也開始內建SERDES的趨勢發展下,在FPGA平台上整合HDMI與DVI介面收發器功能的構想不僅可行,更具備商業上的應用價值。

而在FPGA靈活彈性的加持下,未來這些視訊傳輸的應用空間,可望從目前高度集中於各種影音消費性電子設備,拓展出更多元的應用,因為只要選用車規或工業級的FPGA元件,即可輕鬆滿足這些寬溫操作需求。

(本文作者任職於萊迪思)