在4G無線基頻的演進中,目前仍有兩大技術陣營競逐領導地位,亦即長程演進計畫(LTE)和全球微波存取互通介面(WiMAX)。雖然兩大陣營的技術應用領域有其重疊之處,但就其發展過程而言,兩者還是有些許差異。例如WiMAX的主要定位是為各種運算裝置提供無線寬頻存取,亦是機器對機器(M2M)通訊應用的首選技術。

此外,為有線寬頻尚未成熟的地區提供固定式的無線連線網路,也是其一大應用市場。相較之下,LTE則與全球行動通訊系統(GSM)一脈相傳,以為手機提供寬頻接取為其主要應用目標。

除了應用目標有所差異外,兩種技術的支持廠商也有顯著不同。WiMAX的主要支持者為英特爾(Intel)與其他資通訊產業大廠所領導的WiMAX論壇,LTE的支持者則主要來自手機產業鏈,包括高通(Qualcomm)、意法-易利信(ST-Ericsson)、威瑞森(Verizon)、沃達豐(Vodafone)等在內的眾多基頻原始設備製造商(OEM)和電信業者。

多模共存勢在必行 基頻設計考驗加劇

雖然目前對於第四代行動通訊(4G)江山誰屬的討論,支持LTE的聲浪已日益高漲,但由於兩者的應用目標仍有部分未重疊的市場,因此最終結果極有可能是兩者共存,在不同地區服務不同的用戶群。為了確保兩個標準都為4G數據機所支援,市場便需要一種能夠同時滿足在兩種技術發展藍圖的靈活解決方案。

行動數據機的發展所面對的限制,不單限於越來越複雜無線標準。今天的智慧型電話必須支援多個無線介面。除WiMAX和LTE之外,4G行動設備還須支援大量無線介面,如GSM、整體封包無線電服務(GPRS)、增強數據率GSM演進(EDGE)、寬頻分碼多重存取(WCMDA)、高速封包存取(HSPA)和最新推出的強化版高速封包存取(HSPA+)等。對數據機晶片供應商而言,這些主流標準都是必須支援的標準項目。

由於無線基頻市場的未來不可預見,晶片供應商所面臨的環境十分嚴酷。日益高昂的晶片開發成本和標準本身仍持續演變的現實,均使終端數據機的傳統硬體線路設計方法要面對更大的風險。譬如供應商可能押錯寶,使得晶片瞄準錯誤的標準,最終導致解決方案在發表之前就慘遭淘汰。更重要的是,硬體線路很難在不進行大量設計變更的前提下支援所有標準,故其成本高昂、體積笨重且功耗大。

這自然催生了具有足夠靈活性,支援多個標準並能縮短開發週期的可編程解決方案的需求。

混合式/SDR架構將成主流

雖然如此,在新一代行動基頻晶片的設計中,硬體線路方案還是三大主流之一,因為這種方案具備可讓首批晶片快速上市的優勢。此外,針對某個特定標準而設計的硬體,通常可確保最低功耗。但由於缺乏靈活性,也不能因應標準更新做出快速的反應,因此提供另兩種方案崛起的機會。

目前行動寬頻數據機晶片市場上,為了解決純硬體方案彈性不足的缺點,已發展出混合式方案和軟體定義無線電(SDR)兩種以彈性見長的設計方式。混合式架構是將硬體線路設計與可程式設計處理器結合在一起,數據機中須保持設計彈性的部分,以嵌入式數位訊號處理器(DSP)核心和軟體演算法來實現。只有運算密集和靈活性較小的數據機部分,如傅立葉變換(FFT),才利用硬體線路的作法來實現。

軟體定義無線電則是一種完全的「軟體數據機」實現方案,可在同一塊晶片上以軟體同時支援多個無線標準。這種方案採用完全可編程設計解決方案,具有全面的靈活性,能夠處理多個現有或未來的標準,而毋須對晶片進行重新設計。然而這類方案並非十全十美,其主要問題在於,和所支援標準而優化的硬體線路方案相比,軟體定義無線電晶片的設計工作較複雜,功耗通常也較硬體線路方案高,因此若要採取軟體無線電來開發數據機晶片,則低功耗與簡化設計將是兩大重點。

由於採用純硬體方案存在高風險性,無法滿足當前不可預測的市場需求,所以現階段大多數供應商不太可能選擇完全硬體化的設計架構。因此,在新一代行動寬頻數據機晶片市場上,後兩種可編程設計方案才是各家供應商選用的主流開發策略。

高性能DSP核心扮演關鍵角色

為了在新一代行動寬頻數據機晶片中保持一定彈性,高效能的通用型DSP核心所扮演的角色,將日益吃重。目前在各種行動和無線應用中的數據機晶片已內建數量不等的DSP核心。這類高效能DSP核心均採用混合了超長指令集(VLIW)和單指令多資料(SIMD)架構的混合式架構。

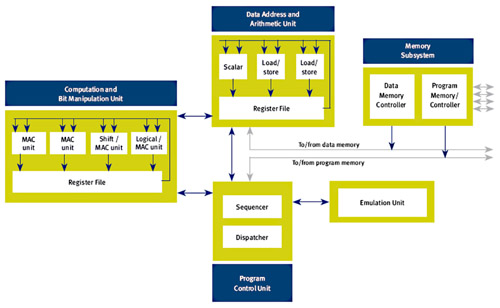

VLIW允許以高階語言(如C語言)撰寫的程式碼進行平行指令處理,從而提供更佳的平行運算能力,並有助降低晶片的功耗。以高階C語言來進行程式設計,可大幅減少研發團隊的設計時間,並降低開發成本,縮短上市時間。圖1為此類DSP核心的典型功能方塊圖。

|

| 圖1 可支援VLIW和SIMD的混合式DSP核心功能方塊圖 |

以CEVA-X1641的DSP核心為例,這是一款具備四個乘累加器(MAC)單元的嵌入式DSP,由四個資料寬度為16位元的MAC單元組成。若晶片製造商以65奈米製程來實現此一核心,即便是在最差的條件下,該核心的運行時脈也能高達700MHz。

這種高性能且易於使用的DSP針對行動數據機系統單晶片(SoC)提供多個軟硬體分區。不同的基頻客戶能在自己的數據機設計中,採用從單核心到多核心的不同實現方案和分區,並結合不同的硬體加速器來完成數據機功能。

SDR設計考驗DSP核心

除了前文所提的混合式架構外,目前業界也開始出現軟體定義無線電概念的實作晶片方案。如果要開發出在功耗、成本、尺寸等各個面向上均具備市場競爭力的軟體定義無線電數據機,則必須更小心地評估其所採用的DSP核心。因為在此架構下,數據機的所有核心功能都是透過DSP和軟體演算法來實現的。

若選擇軟體定義無線電架構,其晶片所採用的DSP核心通常必須針對先進的無線通訊而設計與最佳化,以確保其運算能力可以支援各種不同行動寬頻標準。

目前在DSP核心授權市場上,已有足堪擔此重任的DSP核心問世,可支援要求最嚴苛的4G行動標準如第五類LTE(LTE Cat. 5)和IEEE 802.16m,而且也能同時兼容現有的3G與3.5G無線通訊標準。也唯有採用能滿足上述標準所立下的效能門檻的DSP核心,晶片供應商才能同時在單一架構中支援多種無線介面,實現真正的軟體式數據機。

這類DSP核心是以單一引擎來完成所有無線處理工作,毋須仰賴多顆基頻輔助處理器。對於軟體定義無線電數據機的商品化而言,至關重要,因為以往的軟體定義無線電方案通常是以一顆主DSP晶片搭配基頻輔助處理器的方式實現。

這類分散式架構除採用多顆處理器外,還必須採用額外的記憶體、資料緩衝器等元件,因此整個系統的功耗和尺寸相當可觀,成本亦過於高昂。

事實上,軟體無線電架構以往只有軍事或航太通訊產品採用,與系統尺寸過大、功耗太高、價格高昂這三項因素有密不可分的關係。若軟體定義無線電技術要應用在行動數據機等消費性市場上,勢必要設法妥善解決這三大難題。

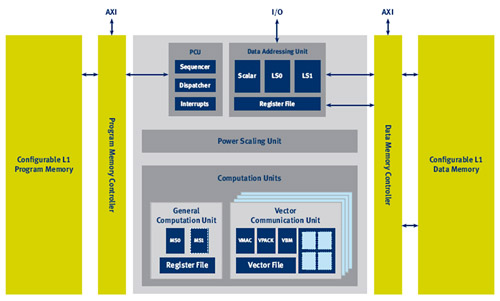

為了解決上述三大缺陷,專為軟體定義無線電通訊應用所設計和最佳化的DSP核心中,除了部分DSP功能區塊外,還整合了數量不等的向量通訊單元(Vector Communications Unit)。每個向量單元是一個256位元SIMD引擎,採用三路VLIW和大量16位元MAC、演算法、邏輯及位移單元。

透過這些向量通訊單元的幫助,這些特殊化的DSP核心可以滿足4G無線數據機的要求,包括矩陣處理、多重輸入多重輸出(MIMO)檢測器、複雜濾波、資料交換和位元流處理。圖2為內建向量通訊單元的DSP核心功能方塊圖。

|

| 圖2 專為SDR所設計的DSP核新功能方塊圖 |

彈性化設計勢在必行

隨著行動通訊產業朝向4G發展,因開發成本和多個變化標準的問題,使傳統以硬體線路為基礎的設計方案的風險大增。所以,設計一個能夠迅速適應不斷變化的標準,並可在多代產品上重複使用的靈活解決方案至關重要。

以混合式方案或全軟體式數據機為基礎的可編程設計解決方案,正式因應此一趨勢而誕生的產物。可編程方案能讓設計團隊輕鬆地套用先前所完成的設計,並確保產品能快速上市。

無線基頻領導廠商早已認可轉向可程式設計解決方案的發展趨勢,而投入DSP架構標準化的工作。在DSP核心標準化後,晶片廠商可以更輕鬆地根據其系統架構和靈活性水準選擇正確的DSP核心。而且,最新的節能和製程幾何尺寸縮小技術,也使得這些可編程設計方案漸漸成為多種應用中實現4G方案的首選方法。

(本文作者為CEVA產品市場總監)