電路板設計人員的主要專業技術集中於元件的挑選,以及將主要的建置區塊組合在一起,進而構成電路板架構。

然而,隨著光學傳輸網路(Optical Transport Network, OTN)這種較高速度及多重通訊協定輸入/輸出介面的問世,使得時脈樹設計(Clock Tree Design)的複雜程度突然間躍升。

電路板設計學問大

隨著大多數電路板設計人員已經意識到時脈元件的選擇不再是一件簡單的事情時,設計與供應時序元件產品的公司也已察覺到他們的顧客所面臨的問題,並且提供一套工具讓一些沒有類比設計博士學位的設計人員能夠很快速地完成時脈樹。

接著來看一看現今在選擇與設計時脈元件時必須處理哪些問題,並討論可以利用哪些協助來完成工作。

在電路板的設計流程中,時脈提供可滿足架構區塊需求的服務功能。直到架構元件都已被選定,完整的時脈規格還是無法決定。請注意有些複雜的通訊系統已解決一些時序功能的問題,例如在架構階段的網路同步。一旦選定架構元素後,其功率、面積與氣流需求,就是交由電路板設計人員來負責。然後是加入與布局重要相關的元件,例如連接器、面板開關以及白色發光二極體(LED)等等。這樣一來,留給膠合邏輯、電源供應器及時脈等服務元件的電路板面積、功率或成本預算往往就很少了。

衡量電路板面積大小

在所有最簡單的情況中,不同的協定、電壓及效能規格須使用不同的時脈。雖然可在時脈樹中簡單描述每一種所需功能並常被視為離散元件來處理,然而針對每一個功能使用分離裝置,就成本、面積及功率代價(Power Penalties)而言,都是不可行的。基於這個原因,時序元件供應商已經創造出一種將許多功能整合至單一封裝的元件。這是為了協助達成最佳化的電路板設計,但這也產生一個問題,就是究竟是哪一組零件所提供的最佳化混合功能,可以滿足特定需求。同樣地,介於成本、面積、功率及效能之間的取捨優先順序,也會因為這個設計與另一個設計不同而有所差異。

時序元件供應商體認到其龐雜的零件目錄,雖然代表著可讓顧客找到最佳化解決方案的機會,但同時也可能是許多困惑的源頭。其結果是,大部分的時序元件供應商提供時脈樹建構工具或快速服務,包括由其知識淵博的應用工程師提供加速服務,以及提供一整套調整至符合每一種設計需求的解決方案。與可以提供全部所需元件的時序供應商一起合作,能夠讓數位電路板設計人員得以擺脫必須結合數個局部且不相容的解決方案的痛苦。

將時域抖動限制納入考量

時域(Time Domain)抖動指的是時脈邊緣位置不準確,在一般示波器上查看時脈可看見這個現象。週期至週期(Cycle-to-cycle)抖動代表非常短期的情況,指的是一個時脈邊緣至下一個。這在數位邏輯應用上是很重要的,在這裡若時脈脈衝太短,則會造成建立(Setup)時間或保持(Hold)時間的衝突。週期抖動是一個較長時間的情況,這在資料回復應用上很重要,因為過多的週期抖動會闔上「眼睛」,進而導致較高的位元錯誤率。這兩者都可以透過直接比較目標值與時序元件規格來處理。透過時序元件供應商網站上的參數搜尋工具,可以輕鬆地選定相容元件。

嚴密計算功率消耗

從歷史上來看,時序元件是一種有著單一電源軌及一些可程式化功能的簡單元件。其規格資料中包含單一功耗或電流值,因此很容易直接進行比較。再者,其功耗通常是遠小於元件的封裝在沒有氣流或散熱片的情況下所能消耗的功率,所以針對特定晶片的散熱計算是不必要的。

很不幸地,須符合低相位雜訊(Phase Noise)目標的整合及較高的功率消耗,已導致功耗計算及散熱分析都變得複雜,且須要針對特定應用進行解決。近期許多時序元件已提供高彈性,且有能力關閉不使用的功能。針對適用於應用環境的電壓軌,它們也有能力去驅動個別電路。

解決方案就是一套元件配置器工具(Device Configurator Tool)。這樣的工具不僅可讓電路板設計人員決定時序元件的設定,同時也可針對特定電路板和用途提供有效的功耗與相關溫度的預估,是極佳的建構工具。

留意頻率擴散問題

一直到最近,特定市場區隔中的電路板設計人員,都只須擔心提供五或六種不同的頻率,而這些頻率一旦在電路板通電後就會固定下來。舉例而言,乙太網路路由器可能必須根據安裝的可插式光學模組種類,來決定須提供25MHz、125MHz或是156.25MHz三種頻率的其中一種頻率,以提供線路介面(Line Interfaces)使用。

而現今被設計給某個市場的功能,已被快速淘汰替換成其他功能。上述乙太網路的路由器現在可能需要一個第三代通用序列匯流排(USB 3.0)連接埠,以及一個SD卡的插槽,這就需要40MHz和12MHz的時脈。它也可能支援相容於光學傳輸網路的上傳連結埠,而這就需要三十至四十個不同的時脈頻率,這些頻率能夠根據軟體的配置不同而有所改變。如此的做法不僅最終會導致更多的頻率,而且那些頻率也不再以簡單的整數比形成關聯。

在時序元件能夠提供更多的彈性,以及在單一元件內有著多重鎖相迴路(PLL)後,這些問題都得到解決。然而,彈性往往會增加程式設計的複雜度。這些新元件須配備如IDT的Timing Commander配置器工具,來協助設計人員利用簡單的方式以設定複雜的元件。只要插入所需要的輸入與輸出頻率,這個工具就會釐清如何針對所有暫存器進行程式設計。它也會針對每一個頻率方案提供一個簡單的輸出檔案,並提供給作業軟體,或是永久燒錄至零件中。

關注頻域抖動現象

|

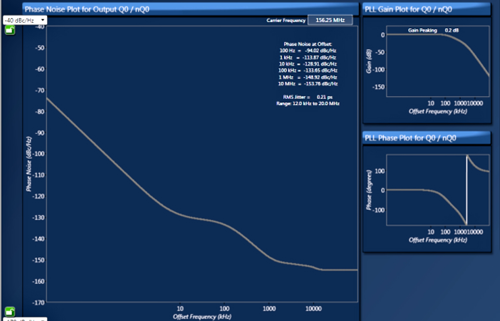

| 圖1 IDT的時序Commander所顯示的相位雜訊範例 |

頻域抖動指的是在預期之外、通常是不需要的,存在於所有的真實世界時脈訊號中的額外頻率。這項規格最常用一條曲線來代表,這條曲線是指1Hz頻帶中的相對能量,是期望的頻率(載波)能量,相對於來自載波的頻率偏移量。若是出現在高效能類比數位轉換器(ADC)或數位類比轉換器(DAC)的參考時脈中,則這些不必要的頻率元件顯得更為糟糕,這是因為那些元件將會增加許多其他不必要的頻率。還有,用於高速串列介面(Serial Interfaces)的實體層元件(Physical Layer Devices)通常會內含ADC或DAC,所以頻域抖動問題在此也日益受到關注。

在高效能的應用中,須要比較時序元件的相位雜訊效能,相對於它所驅動元件的輸入規格。相位雜訊效能是取決於時序元件的確切配置,配置器工具可顯示每一個設定的曲線(圖1)。

找出訊號協定關連

|

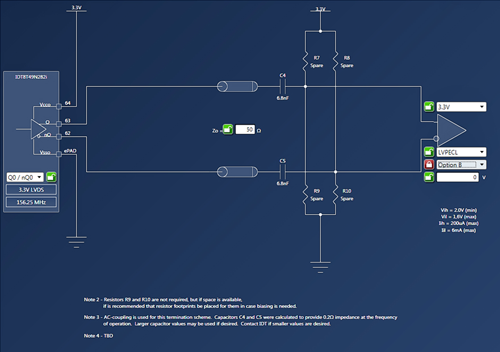

| 圖2 時序Commander所顯示的終端原理圖(Termination Schematic)範例 |

電路板設計中的時脈樹,試著將全部或是大部分來自電路板上的次系統元件,以及石英晶體與振盪器等頻率來源元件結合在一起。結果往往須要轉換在單端(CMOS)協定,以及一種或多種差分(Differential)協定(如低電壓差動訊號)之間的訊號,而且也往往須要調整電壓擺動(Voltage Swings)。這通常是利用被動元件網路來完成,雖然有時會使用到主動式位準調節器(Level Shifters)。對於不熟悉每一協定的電流與電壓規格的設計人員而言,這通常就須要閱讀大量的應用說明。針對如何處理這些協定,以及特定時序元件的輸入或輸出電壓不匹配問題,配置工具會提供建議(圖2)。

此外,還可以產生建議的原理圖、電源濾波器的元件規格值,以及可能須要使用的迴路濾波器,特別是在較高效能的元件上。

演練備援/故障情境

隨著社會場所越來越依賴網路連接來滿足日常生活需求,因此從行動電話到兆位元(Terabit)等級核心路由器裝置的可靠運作就變得比以往更為重要。用於語音電話交換機及軍用等級容錯系統的尖端技術,已慢慢地進入網路層級中。任何系統的設計方式都必須能夠將故障可能性(FIT Rate)最小化,且當故障真正發生(適度的降級)時,要能將影響最小化。許多系統在故障情境(Failure Scenarios)下的行為,也須符合ITU-T G.8261等國際標準。

對於時序元件而言,這些主要是與切換(Switchover)和延遲有關。切換是一種程序,這種程序會辨識出某個時脈來源已受到品質降級的影響,或是訊號整個全部丟失,並且切換至備用來源。延遲是切換的最終情況,並且是發生在所有備用時脈來源全都不合格時,退回至本地的石英晶體或振盪器以維持某種程度的功能性。

創建一個可靠的時脈樹,是一種系統層級的問題,必須在整體時脈樹的層級來解決,特別是在必須符合某個外部定義的系統層級規格時。這是一項仍然須有經驗豐富的工程師參與其中的任務。電路板設計人員必須與來自時序元件供應商的資深工程師團隊合作,而這些工程師擁有豐富的系統經驗,可解決現今所面臨的問題。這並不是一個可以在個別晶片基礎上輕易解決的問題,那些試圖混合使用不同供應商的元件的人,可以證明這個觀點。

事半功倍

電路板設計是一項困難的工作。在過去五年的時脈領域中,頻率擴散(Frequency Proliferation)、緊密時序與頻域抖動的需求,以及像大雜燴般的不同訊號協定與電壓水平,更快速地提升了電路板設計的難度。

時序元件供應商已認知到此一問題,並且以時脈樹建構器(Clock Tree Builder)、參數搜尋以及多元和易於使用者的配置器工具來回應這些問題。這些工具為電路板設計人員提供寶貴的協助,但仍然無法解決全部的問題。針對依然存在的問題,還是必須仰賴對時脈樹涵義有深刻了解的資深應用工程師團隊提供協助。

(本文作者為IDT時序及同步部門系統架構處長)