雙倍資料傳輸速率(Double Data Rate, DDR),有別於傳統同步動態隨機存取記憶體(SDRAM)僅用時脈(Clock)上升沿傳輸的概念,DDR同時使用Clock上下沿傳輸,藉此達到傳統SDRAM的兩倍傳輸率;如表1所示,可發現Data Transfer Rate訊號傳輸率為Clock頻率的兩倍。此外,DDR規格持續演進,不僅傳輸率更快,工作電壓也逐代降低,更符合攜帶式電子產品所要求的省電能力及電池續航能力。

除廣泛應用的標準DDR以外,聯合電子裝置工程協會(JEDEC)還針對行動裝置特別規範LPDDR(Low Power DDR)標準,主要差異在於工作電壓較DDR低。由表1可知LPDDR3的Operating Voltage比標準DDR3還要少0.3伏特(V),也因此,LPDDR3在功耗上會比DDR3少,能讓行動裝置的電池續航力更久。

此外,一般的DDR由於傳輸速度及效能不夠符合顯示卡需求,JEDEC也特別針對顯示卡IC設計Graphics DDR,與標準DDR相比,其特色就是降低功耗、提高性能來符合顯示所需要的DRAM需求。

DDR五類訊號各司其職

|

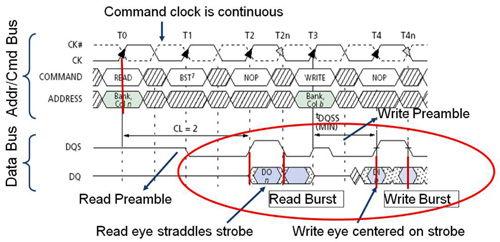

| 圖1 DDR訊號傳輸示意圖 |

有別於其他高速數位應用如第三代通用序列匯流排(USB 3.0)、串列式先進附加介面(SATA)和PCIe等使用串列式匯流排(Serial Bus)的方式,DDR依然使用平行匯流排(Parallel Bus)架構,如圖1所示,其訊號主要分成五類,分別是Clock、Command、Address、DQ、DQS。

Clock是DDR中最重要的訊號,因此,在DDR架構中,Clock採用的是差動訊號(Differential Signal),避免雜訊的影響進而造成DRAM工作異常;此外,訊號傳輸是透過Clock的上升沿跟下降沿來觸發,在DDR規範中可看到幾乎所有Timing的時間單位都是以Clock為主。

Command則代表記憶體控制器(Memory Controller)對DRAM所下達的動作,從圖2可看到時間點在T0時,控制器下達的指令是要對DRAM進行Read的動作,在經過CL(CAS Latency)=5的時間之後,DRAM就開始傳送資料給控制器。其中,CL係當控制器下達Read指令後,DRAM須經過多少時間才正式開始讀取的表示方式,CL=5即代表DRAM接收到指令後,需要五個Clock週期才開始傳送資料;因此CL愈短,也就是DRAM準備時間愈短、效能愈好。

|

| 圖2 DDR3 Read週期示意圖 |

在JEDEC的規範中,Command是由RAS、CAS、WE及CS這四個訊號所組成,表2為Command的真值表;舉例來說,CS、RAS、CAS為Low Level,WE為High Level時所代表的Command為Refresh。

至於Address訊號係告知DRAM存取資料的位置,在每次存取資料時,從Address訊號可得知資料所在位置如Bank Address、Row Address、Column Address。以DDR3 512Mb為例,在DDR3內會將512Mb分成八個Bank,每個Bank可想成一個儲存空間,其概念係假設須讀出Data這個資料的話,記憶體除對DRAM下達Read指令外,還須告知DRAM所要讀出的資料Address。

DQ則是實際在傳輸的訊號,為Single-End訊號,根據傳輸方向,將從控制器傳輸到DRAM的訊號定義為Write;從DRAM傳輸到Controller的訊號定義為Read。

最後一種DQS訊號為同步訊號,可用來判斷訊號開始或結束,也可透過DQS與DQ的相位關係判斷傳輸訊號是Read或Write。在DQ訊號開始傳送時,DQS會先有一個從中間態先往下再往上的訊號,維持時間為一個Clock週期,這個訊號稱為Read Preamble,用於提示控制器讀取的資料即將出現;而在DQ訊號即將結束時,DQS也會有一個由下往上的訊號,維持時間為半個Clock週期,此訊號稱為Read Postamble,提示控制器讀取的資料即將傳送結束。

同樣地,Write訊號也會有Write Preamble跟Write Postamble,不同之處係先上再下的訊號,而DQS與DQ的Edge則有一個90度的相位差。

DDR2封裝革新 BGA載板測試應運而生

|

| 圖3 DDR2改用BGA封裝後,新的量測方式案例。 |

JEDEC規範中,定義DDR標準測試點在DRAM顆粒上,以DDR1來說,採用的是TSOP封裝,所以從DRAM接腳直接拉出訊號,就能得到一個良好的量測點。但是從DDR2開始,JEDEC改用BGA封裝,無法像DDR1封裝一樣從TSOP腳位拉出訊號量測,因此大多工程師通常量測印刷電路板(PCB)的Trace線(圖3),惟這種方式離顆粒已有一段距離,除訊號變差以外,甚至有可能因阻抗不匹配造成訊號反射,進而得到錯誤的量測結果。

為避免量測結果出錯,建議可使用下列兩種量測方式,來得到較好的量測訊號品質,首先是在顆粒下預留Via Hole;其次則是利用儀器商提供的BGA載板進行量測。

|

| 圖4 Via Hole測試方式 |

Via Hole量測方式如圖4所示,在DRAM顆粒下方預留量測點,由於量測的位置離顆粒相當近,量測出來的品質相當不錯,缺點則是在初期設計印刷電路板布局時須預留孔位。

儀器商提供的BGA載板量測則如圖5所示,即在DRAM跟PCB板中間嵌入一片量測載板,這種方式可將顆粒的訊號從載板兩側拉出來量測,由於儀器商也會提供各種載板的S參數,使用者還能透過軟體模擬方式去除載板效應,以得到更好的量測品質。

|

| 圖5 BGA探針應用位置圖 |

與此同時,由於JEDEC對Read/Write訊號量測參數分別有所規範,因此,在正式進行量測之前,工程師須針對DDR做訊號分離的動作,以下將介紹傳統分離Read/Write方式,以及現在儀器商所提供的圖解訊號分離方式。

MSO助臂力 DDR訊號分離更快速

傳統方式係利用混合訊號示波器(MSO)分離Read/Write訊號,如前面表2提到,DDR的Command是由RAS、CAS、WE及CS這四個訊號組成,因此可在針對Clock、DQ、DQS等訊號進行量測的時候,額外使用MSO提供的十六個數位通道擷取四個Command訊號,以判斷此時訊號是Read/Write。但此種方式費時、且工程師須相當了解JEDEC對Command的定義,光是在分離Read/Write訊號時就已花費相當大的心力及時間。

較新的方法則是利用儀器提供的Zone Qualify觸發實現訊號分離。圖6為DDR2 Signal Diagram,可發現在Read/Write訊號開始傳輸前都有一個先下再上的Preamble,當DQ訊號為Read時,DQS與DQ的Edge是切齊的;而DQ訊號為Write時,DQS的Edge則切齊在DQ的中間位置。

|

| 圖6 DDR2訊號傳輸示意圖 |

使用Zone Qualify觸發Preamble,可看到圖7中,1號訊號為DQS,2號訊號為DQ,透過在示波器上畫出一個方塊,並將觸發條件設定成訊號不能通過這個方塊,就可輕鬆觸發到Preamble的開始位置,此時雖然還不能將Read/Write訊號分離出來,但已可看到DQ訊號明顯穩定下來,並持續觸發在Read/Write剛開始傳送的狀態。

|

| 圖7 第一道Read/Write訊號分離步驟 |

第二步再利用一個方塊將Read/Write分離,如圖8所示,可明顯看到1號的DQS有兩個略為不同的Preamble,分別是Read/Write的Preamble,透過畫第二個方塊,並將觸發條件設定成訊號須通過這個方塊,就可分離出Read/Write訊號,其判斷方式如圖7提到。此種分離方式相對於上面的傳統方式,能更快速的分離Read/Write訊號,並節省整體量測時間。

|

| 圖8 第二道Read/Write訊號分離步驟 |

DDR電氣測試面面觀

除手動量測DDR訊號外,儀器商都會提供相當方便的自動化測試軟體來節省工程師在開發產品時候的測試時間,在正式利用自動化測試軟體進行量測的時候,測試人員須先了解幾項參數才能進行正確的量測,如DRAM Speed Grade、SDRAM Type及AC Level等,以找到相對應的規範進行量測。

以DDR3來說,主要量測項目分成電氣(Electrical)和時序(Timing)兩個區塊。電氣測試部分主要包含AC/DC Level測試、Rise/Falling Slew Rate及Overshoot/Undershoot等,多針對電壓進行測試,下面將說明這三種測試的概念。

|

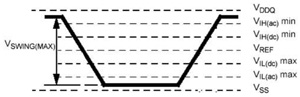

| 圖9 DDR Input Logic Level |

首先是Single-Ended AC and DC Input Levels for DQ and DM,基於DDR訊號速度快、反射較嚴重的原因,JEDEC在規範Input Logic Level時,特別著重直流(DC)與交流(AC)兩個參數,以降低訊號完整性問題;並在規範中定義VIH(ac)、VIH(dc)、VIL(ac)、VIL(dc),如圖9所示。當訊號向上穿過VIH(ac)後並保持在VIH(dc)以上,為High Level State或「1」;反之,當訊號向下穿過VIL(ac)後並保持在VIL(dc)以下,為Low Level State或「0」。

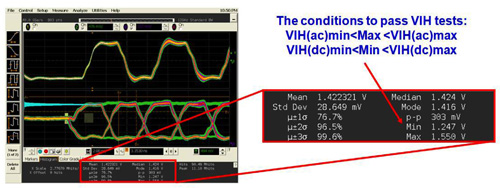

因此,在電氣測試中,工程師須針對AC/DC Level進行測試,以DDR3 DQ與DM的AC/DC Level規範為例,VREF=0.75伏特、VSS=Ground,Note2則為Overshoot/Undershoot規範。實際進行量測時,將透過Histogram方式,如圖10為VIH量測示意圖,由Histogram找出High Level的Vmax跟Vmin之後,再對比DDR3 DQ與DM的AC/DC Level規範。

|

| 圖10 VIH測試方法 |

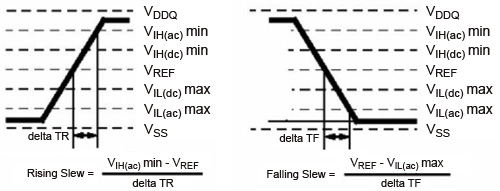

此外,DDR3規範還要求針對訊號做Rise/Falling Slew Rate測試,測試概念如圖11所示,透過協會所定義的公式計算出VREF到VIH(ac) or VIL(AC)的斜率。

|

| 圖11 Rise/Falling Slew Rate測試概念圖 |

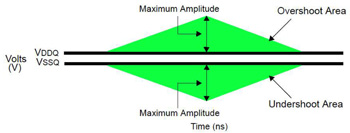

至於圖12為JEDEC針對DDR3 Clock、Data、Strobe and Mask Overshoot and Undershoot的定義及規範。除規範Maximum Amplitude以外,JEDEC還規範Overshoot跟Undershoot的區域不能過大,透過表3可看到Maximum Amplitude的單位為伏特,Overshoot跟Undershoot區域的單位為秒,藉此定義Overshoot跟Undershoot範圍不能太大。

|

| 圖12 Overshoot and Undershoot範圍定義 |

掌握Read/Write位置 DDR時序測試更精確

另一方面,時序測試部分較常見的有Read/Write Preamble、Postamble測試、DQ/DM Setup/Hold Time等,下面將說明這幾種測試的概念。圖13為DDR2/3 Read與Write示意圖,可看到DDR2/3在Read部分不管是Preamble或Postamble的定義都一樣;Write的部分則是在Postamble定義相同,比較特別的是DDR2/3Write的Preamble的部分定義不同。

|

| 圖13 DDR2/3 Read與Write中,Preamble及Postamble的定義。 |

另外,經常讓工程師誤會的是Preamble/Postamble時序量測的結束點,在DDR2/3 tRPRE、DDR2 tWPRE、DDR3 tWPRE的量測位置都是從中間態(也就是0伏特的位置)的起始點量測到中間態的結束點;但是在DDR2/3 tRPST、tWPST的部分則是從中間態的起始點量測到「由低往高的反折點」,一般測試者經常會誤解而導致量測參數錯誤。

DQ、Address and Control Setup/Hold Time的定義中,tIS、tIH指的是Address and Control Setup/Hold Time,tIS量測的位置是從VIL(ac)到Clock上升緣的交叉點(Cross Point),tIH量測的位置為從Clock上升緣的交叉點到VIL(dc);tDS、tDH指的是DQ Setup/Hold Time;tDS量測的位置是從VIL(ac)到DQS的Cross Point,tDH量測的位置是從DQS的Cross Point到VIL(dc)。其測試概念就是在量測交叉點到規範Logic Level的位置,DQ對應的是DQS的交叉點;而Address and Control則對應的是Clock上升緣的交叉點。

透過詳盡的DDR測試方案介紹,相信有助於工程師找出合適的方法進行量測,並加快產品設計腳步。

(本文作者任職於安盟科技)