自從IEEE 802.3af 15.4W乙太網路供電的標準於2003年公布以來,PoE的需求量每年都穩定成長。從最早於網路電話及無線基地台的應用,到後來的安全監控新需求,在在證實了整體乙太網路供電市場規模的成長態勢,卻也帶來全新的挑戰。

由於新的需求一直增加,IEEE802.3af規定的15.4瓦供電裝置(PSE),其輸出功率已不足以應付日益增加的受電裝置(PD)耗電的需求,因而刺激新一代標準的問世。一般來說,新一代的PD設備,耗電的要求如表1。

| 表1 傳統與新興之終端PD功耗比較 |

| 傳統終端應用 |

網路電話

(IP Phone) |

單無線模組之無線基地台

(WAP) |

|

具有方向控制機能的網路攝影機

(IP Camera) |

| 功耗 |

7瓦 |

7瓦 |

|

靜態工作時10~20瓦 |

| 新興終端應用 |

視訊電話

(Video Phone) |

多無線模組之無線基地台

或WiMAX AP |

高功率RFID讀取器 |

具有方向控制機能的網路攝影機 |

| 功耗 |

15~20瓦 |

13~25瓦 |

15~30瓦 |

動態啟動瞬間15~30瓦 |

由表1的PD設備耗電要求可知,IEEE 802.3af所訂的15.4W PSE輸出功率,已無法滿足新一代的PoE應用。因此IEEE協會從2005年就開始著手討論新一代的乙太網路供電標準IEEE 802.3at。

直至2007年7月為止,對於IEEE802.3at的規格,會員間所討論的議題包括:

由以上規格可知,IEEE 802.3at的PSE與PD裝置的系統設計,將比以往的IEEE 802.3af規格,在PSE與PD裝置的系統設計上,有更多的挑戰。

高功率直接影響PSE元件功耗

在802.3at的發展趨勢之下,高功率PSE裝置的系統設計,所面臨的問題之一,就是元件功耗加大。

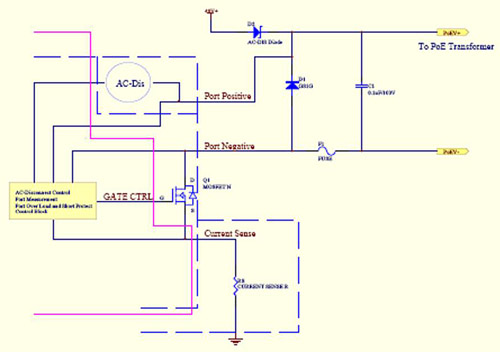

現今PSE ASIC的基本架構及輸出端線路圖如圖1。茲對每一元件做簡單之描述:

由上述元件可知D1、Q1 Rds-on與RS皆為PSE線路主要的功耗元件。以下則對每一主要功耗元件做評估。

|

| 圖1 PSE ASIC的基本架構及輸出端線路圖 |

考慮600毫安培迴路電流,內建MOSFET Rds-on數值為0.5~1歐姆,D2 Forward Voltage為1伏特, 則單一迴路功耗如下:

從以上的數值可以看出一個值得思考的問題,「應如何散熱及降低功耗?」

乍看之下,似乎利用外置MOSFET的PSE架構在功耗上有明顯的優勢,但由於現今市面上外置MOSFET的PSE ASIC都沒有提供完整的PSE輸出功率監控及量測的功能。而且外置MOSFET的PCB面積太大,在多端口的PoE SW上有其限制,所以國內用的客戶並不多。

內建MOSFET的PSE架構,由於目前市上的ASIC大都內建較完整的PSE輸出功率監控及量測的功能,而且又有印刷電路板(PCB)面積小的優勢,在多端口的PoE SW上,大部分還是採用內建MOSFET的PSE ASIC。目前的廠商包括博通(Broadcom)、意法半導體(STMicroelectronics)、德州儀器(TI)與Microsemi等。

考慮內建MOSFET PSE ASIC的功耗分布,AC-Disconnect Diode的功耗是無法避免。其他可以改進的地方,包括降低MOSFET的Rds-on值,以及採用較低阻值的的電流檢測電阻。但都有其相對應的問題:

|

|

| |

該項作法牽涉到每一家晶圓廠製程的技術,另外,較低的Rds-on值意味著晶圓尺寸(Die Size)的加大,同時帶來成本上的考量。 |

|

|

| |

較低阻值的電流檢測電阻,意味著相對應的量測電壓也較低。這樣的電阻牽涉到DC-Disconnect及功率分級檢測Class0的準確度。IC供應商必須精確的控制PSE ASIC電流量測線路的精準度,才能順利提供產品。 |

高功率PD裝置設計面臨瞬間電流抑制考驗

高功率的PD裝置,其系統設計所會面臨到的問題,主要是在如何抑制瞬間啟動電流、增加DC-DC轉換效率及降低系統功耗上。

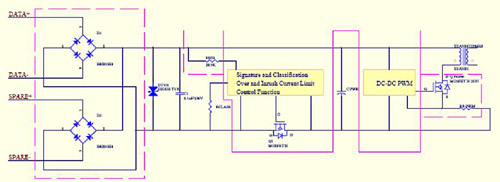

圖2為現今PD ASIC的基本架構及輸入端線路圖。

|

| 圖2 PD ASIC的基本架構及輸出端線路圖 |

同樣對每一元件做簡單之描述:

先來看PD線路功耗的問題。PD線路中主要的功耗來源如下:

由上述結果可發現,橋式整流二級體及PD ASIC本身的耗損占去大部分。

對於某些內建整流二級體及PWM Switching Power MOSFET高整合度的PD ASIC,一般而言只建議用於4瓦Class 1等級的PD應用。大於10瓦的PD應用,則不建議採用此種高整合度的PD ASIC。

另外,PD ASIC也須提供低壓VCC輸入的功能,以降低晶片本身的功耗。

瞬間啟動電流同成門檻

關於瞬間啟動電流的問題,原先在7瓦以下的PD並不明顯,但隨著電壓提升,在10瓦以上及高功率的PD就須特別注意。

在PD ASIC的基本架構及輸入端線路圖中,C PWR表示DC-DC之能量儲存電容,用以提供PWM DC-DC線路能量以及降低迴路上的紋波雜訊值。但太大的C PWR值會造成PD Power On瞬間的電流值太大,因而觸發PSE端的過流保護機制,而造成相容性的問題。所幸,近年來包括美國國家半導體(NS)、意法半導體、凌力爾特(LTC)等公司,其推出的新一代PD ASIC,都增加了瞬間啟動電流限制的功能,以解決這個問題。

DC-DC須提振轉換效率

目前大部分的線路,都為傳統之順向(Forward)或馳返式(Fly Back)。以12伏特的輸出而言,效率約只有80~85%。如果考慮90%以上的效率,改採同步整流的架構將是必需之路。

雖然目前高功率PoE還有一些系統設計上的挑戰,但在眾多ASIC廠商的努力下,相信不久的將來,這些因素會逐一消失。到時IEEE 802.3at將會取代現有的IEEE 802.3af,提供更多範圍的乙太網路供電應用。