新型低漏電MCU與損耗分析開發工具將顯著推升嵌入式系統節能效益。設計人員可選用採先進低漏電製程並內建FRAM的新款MCU,搭配半導體公司提供的即時電源損耗分析工具和除錯器,全面強化系統電源管理功能,進一步實現低功耗設計。

所有使用電池的裝置都有一個共同點:有限的電源,如果須延長操作時間並減少替換電池的需求,設計者必須減少微控制器(MCU)系統電源需求。許多現代裝置都以電池供電,從單一的鈕扣電池到鋰離子電池,這些電池的共通點就是他們所能提供的電力是有限的;然而在某些情況中,這些電池不該、甚至不能被更換,這時系統電源需求就必須降至最低,以減少電池更換的需求。

在開始設計一個極低耗電的系統前,設計者必須先了解各個採用不同的低耗電技術及周邊元件的MCU之間的取捨,以及可在電源預算內達到最大化應用壽命的工具,因此,選擇一個低功耗MCU可說是減少系統耗電的第一步。

採用低漏電製程/FRAM MCU節能效果有保障

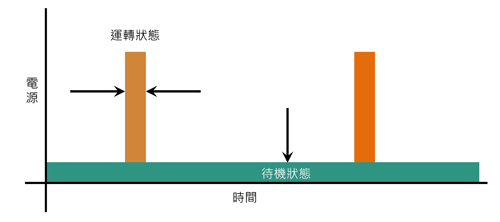

在某些案例裡,MCU甚至支配整體系統的電源消耗,如果某個應用裝置通常長期處於休眠狀態,並定期啟動以處理資訊,那待機時的電源消耗就會是主要的考量因素(圖1);當然也有些案例所需的應用會是50%處於運轉狀態,50%處於待機狀態。

|

| 圖1 系統耗電量可依運作時間製成圖表 |

不論如何,選擇最佳運轉及待機節能的MCU皆能幫助降低應用裝置的平均耗電。因此設計人員可選擇採用先進低漏電製程的MCU,以降低啟動電流(通常以μA/MHz為測量單位)及待機耗電。理想中,要達到最低的耗電,應用裝置應同時減少運轉時間及待機耗電。

檢視記憶體技術及其在應用裝置內如何被使用,能夠明顯地降低C-startup與其他應用程式的啟動時間,並因此降低系統的能源需求。例如,在應用裝置中使用採用非揮發性記憶體技術--鐵電隨機存取記憶體(Ferroelectric RAM, FRAM)的MCU,那麼程式碼、常數、變數及堆疊皆能當作靜態隨機存取記憶體(SRAM)處理,但實際上卻是以非揮發性的方式儲存。

FRAM寫入是即時的,且不需特別設定,不像快閃記憶體(Flash)一樣需要一個通常相當耗電的電荷幫浦(Charge-pump);此外,FRAM屬於統一記憶體,能輕易地針對應用裝置需求分割及客製化。

那麼FRAM如何幫助減少系統能源呢?設計人員只要將某些變數或內含應用狀態、校正資訊、運算的中級結果,以及其他數據的大型陣列存在FRAM中,應用裝置便可從關機或睡眠狀態更快速的啟動,且不須重新初始化這些變數或重新運行相當耗資源的硬體矯正步驟。

此一方式將大幅降低MCU的C-startup程序和應用程式碼初始化的執行時間。由於儲存於非揮發性記憶體,這些變數能夠立即供開發者使用,且上一次的執行設定也能快速恢復。如果要使用快閃記憶體來達成同樣的功能,就必須面對可能在寫入/消除時斷電的風險,因此挑戰性相當高;FRAM則沒有這種困擾。

MCU功耗模式取決於時脈設計

所有極低功耗MCU皆有多種低耗電模式能夠讓裝置進入不同的睡眠狀態。這些模式通常會將CPU核心關閉,或將系統內的某些時脈停止運作,讓部分周邊元件完全獨立於CPU之外運作,因此必須要有某種時脈來源以保持周邊元件的運作。這些細節完全依各別MCU所使用的低耗電模式及架構來決定,通常使用任何的低耗電模式都會比不使用低耗電模式好,因此如何將系統設定至最低耗電模式將會是下一步。

時脈是一個相當重要的因素,因為耗電量會隨使用頻率線性成長,因此選擇最低時脈速度會是最理想的。一個好的做法是從例如1MHz的最低時脈開始,並於必要時再提高時脈,低耗電應用裝置通常會想要在啟動時以最快速度執行,並立即回到待機狀態。

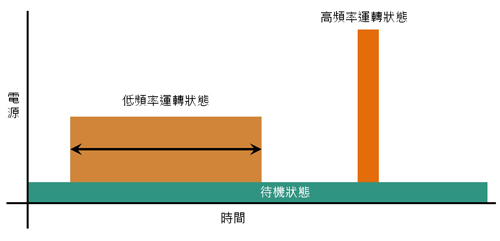

圖2顯示由於使用低CPU頻率,而讓應用裝置長期維持啟動狀態所導致的更高耗電。不過,高CPU頻率也相對有其設計限制,因此也不是所有應用裝置的最佳選擇,主要原因在於更高的CPU頻率代表更高的最大電流,而某些電池可能無法承受更高頻率所需的最大電流。

|

| 圖2 裝置電力消耗會隨運MCU運算速度的高低而改變。 |

以低耗電應用裝置來說,理想狀況下,高頻率的時脈來源應該被停止運作,而低頻率的時脈來源應該保持運作以幫助CPU在需要時定期啟動。

至於將運轉狀態的耗電降至最低的另一個重要考量,適用於CPU核心由獨立(通常內建)的穩壓器供應,且穩壓器的輸出電壓可依所需運作頻率手動或自動調整的MCU。根據所選擇的電壓設定,這些穩壓器通常也占裝置運作狀態電源損耗的一部分。

仔細閱讀這類型MCU的數據表,通常會發現若以最高頻率運作,每MHz的CPU與低壓差線性穩壓器(LDO)綜合運轉電源損耗,在特定的電壓範圍內會有所謂的「甜蜜點」。由於在運轉狀態下完成每單位工作所須消耗的能源,須依據CPU與電壓調節器隨時間消耗的電流需求決定,因此更快的時脈頻率通常會導致較低的電源損耗,即使在運轉時的電源損耗會因此增加。

善用除錯器/損耗分析工具 系統耗能情形一覽無遺

另一個技巧則是了解每個MCU周邊元件的長處,透過內部互連機制讓周邊元件相互連結,並從CPU獨立出來自行運作。例如,在類比數位轉換器(ADC)轉換後,直接記憶體存取(Direct Memory Access, DMA)能夠自動將數據移至記憶體內,CPU毋須介入;如此一來,CPU能在整個資料轉換和存取過程中處於睡眠狀態,直到必須處理數據的時候才啟動。

另一個例子是設定計時器自動定時觸發ADC,因此不須啟動CPU來觸發ADC。通常周邊元件損耗的電力都會比CPU明顯少很多,因此讓CPU保持關機狀態,並利用這些周邊元件執行工作的設計模式,是相當值得考慮的。

使用者還能更進一步關閉任何不須使用的周邊元件,但並不是所有時候都能輕易找出這些元件。一個又快又有效率的周邊元件識別方式,就是使用能夠提供系統智慧型電源損耗資訊的即時電源除錯器;而使用現有的工具和軟體也能幫助開發者最佳化系統電源損耗。

這樣的現代工具組合讓開發者能透過視覺性回饋,快速辨識並解決有問題的設計區塊。透過軟體將系統電源最佳化變成重複回饋過程,且能以正確的工具,如德州儀器(TI)的ULP advisor和EnergyTrace來加速開發流程,也因此加快產品上市時程。

除此之外,工程師利用一些通常已針對架構最佳化的應用裝置專用軟體框架、驅動程式和演算法函式庫,還能得到較低的CPU週期,並因此降低執行時間。如此也能幫助降低整體系統耗電。

另一方面,有些位於矽谷的半導體公司已提供專門為特定MCU架構客製化的數學或數位訊號處理(DSP)函式庫,能夠用來處理訊號及篩選演算法。大部分的編譯器皆內建通用數學函式庫,應用前提是必須供多種MCU架構使用,所以無法針對特定架構最佳化,僅可針對周邊元件進行最佳化。

與其試著找出如何啟動一個周邊元件,或思考初始化流程是否已最佳化,不如使用這些矽谷公司專為以最佳方式初始化周邊元件所設計的驅動程式。不過,設計人員在選擇第三方軟體時,應通盤考慮電源效率,以及軟體是否已針對特定裝置最佳化,才能更加貼近使用需求。

運用這些建議應能幫助開發者減少系統的電源需求。開發者應該考慮選擇正確的微控制器、對進入待機模式保持正確觀念,並利用智慧型周邊設備及現有的即時電源分析工具,進一步提升系統電源效率。

(本文作者任職於德州儀器)