隨著新興應用對資料速率的要求愈來愈高,FPGA支援收發器的頻寬也不斷提升,造成產品設計人員面臨極大的除錯挑戰,而高頻寬混合訊號示波器由於可同時進行類比和數位除錯,將有助提升FPGA設計人員實作效率,加速產品上市時程。

近年來,許多使用現場可編程閘陣列(FPGA)的新應用,都要求FPGA能提供更高速率的收發器,因而帶動新一波高頻寬類比量測及數位分析技術的發展,以協助工程師更有效率地進行FPGA除錯。本文將說明如何使用高頻寬混合訊號示波器(MSO),對FPGA進行數位和類比除錯。

若某個裝置有數以千計的內部邏輯單元,而且收發器速率高達28Gbit/s,工程師該怎麼進行測試和除錯?從數位除錯的角度來看,最大的挑戰在於無法探量FPGA內部重要的邏輯節點,而且測試儀器可用的實體接腳數極其有限。

收發器傳輸速率激增 FPGA除錯挑戰叢生

許多工程師透過內部訊號多工、測試行動聯合組織(Joint Test Action Group, JTAG)介面和內部邏輯分析儀等創新技術克服這些挑戰。不過,這些技術各有優缺點,而且須搭配使用合適的量測設備才能達成目標。

一直以來,工程師都是使用邏輯分析儀對FPGA內部的數位訊號進行除錯。邏輯分析儀是非常強大的數位訊號分析和除錯工具,可提供大量的數位通道(從三十二到成千上百)、同步和非同步擷取能力,以及複雜的狀態觸發條件。不過,邏輯分析儀並不適用於某些特定應用,若工程師須同時量測數位和類比訊號,混合訊號示波器是更為有效的量測工具。首先,混合訊號示波器的類比通道讓設計工程師能有效量測數位裝置中的重要類比訊號,例如測試FPGA上的收發器。此外,若邏輯單元中的訊號看起來有問題,設計工程師可比對現成可用的類比通道的關聯性,以便進行更深入的分析。

混合訊號示波器提供豐富的類比和數位觸發功能、深度記憶體及友善易用的介面。過去混合訊號示波器大都是低和中頻寬示波器,主攻混合訊號量測的核心市場,然而,隨著新興應用要求更高的資料速率,例如最新的FPGA支援28Gbit/s的收發器速度,高頻寬混合訊號示波器的需求開始升溫,以協助工程師處理高速串列量測要求的邏輯分析,並且克服訊號完整性的挑戰。

FPGA數位除錯新方法紛出籠

工程師無法洞察FPGA內部資訊讓除錯任務變得十分困難,促使業界持續發展新的FPGA除錯方法。最常見的FPGA除錯方法包括:直接將訊號從邏輯節點繞接到接腳、透過多工器將訊號路由至接腳,以及使用內部邏輯分析儀。

| ‧ |

|

| |

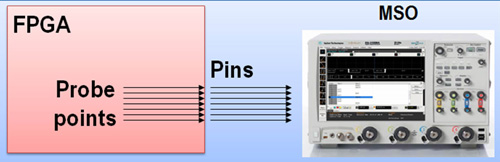

想要存取FPGA內部節點,最簡單的方法是利用FPGA的可編程特性,將這些訊號路由至實體接腳,然後透過混合訊號示波器的數位通道探測訊號。圖1顯示這種簡單的訊號探測方法,此種方法雖然有效,但卻有明顯的局限性。首先,FPGA封裝元件大多僅提供非常有限的實體接腳,因此工程師在測試與除錯時,必須在可用的實體接腳數和可探測的內部節點數間加以取捨。再者,進行FPGA除錯時,工程師根本無從得知應該觀察哪些節點。更糟的是,當工程師想直接將節點繞接到接腳,卻發現只有八或十六支接腳可用來除錯,這意味著如果工程師要探量FPGA新的內部訊號,須更改設計,以便將這些訊號路由到可用的實體接腳。

在此過程中,工程師必須以手動方式更新FPGA設計,以及節點至接腳路由結果。整個過程不但非常耗時,而且很容易造成錯誤。不過,儘管效率不佳,但是這個除錯方法非常簡單,而且同時提供狀態和定時模式,可透徹分析所探量的訊號。

|

|

| 圖1 使用混合訊號示波器的數位通道進行FPGA除錯架構,最多可將十六個探測點直接路由至實體接腳。 |

| ‧ |

|

| |

另一種直接將訊號繞接至接腳的方式,是使用多工器將訊號路由至FPGA上的實體接腳。這種方法有許多好處,首先,設計工程師不再受限於實體接腳數,亦即訊號繞接至接腳的方式可直接探量訊號的內部節點數,比實體接腳數多出好幾倍。假設工程師只能使用十六個接腳進行除錯,藉由使用16:1多工器,工程師可將二百五十六個內部節點繞接到多工器,並僅使用十六個實體接腳來觀測訊號。這種靈活操作讓工程師毋須重新設計FPGA就可觀測更多節點,可節省重複設計的時間。此外,由於工程師可直接在實體接腳觀測訊號,因此混合訊號示波器仍具有可用的狀態和定時模式供工程師使用。 |

| ‧ |

|

| |

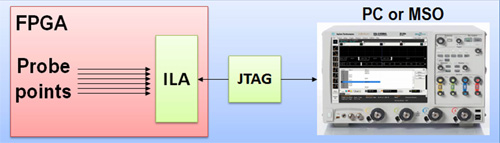

現在許多FPGA供應商均提供FPGA內建的內部邏輯分析儀(ILA),目的是加速除錯。ILA具備觸發電路並使用內部記憶體來儲存軌跡線。JTAG在FPGA和個人電腦間傳輸的資料,可用來配置ILA並讀取所輸出的邏輯訊號(圖2)。這種配置非常方便,因為不須增加實體接腳,而且只須使用一台個人電腦進行基本的邏輯分析。同樣的,這個方法也有許多限制,如ILA很耗資源,須占用FPGA和內部記憶體以便處理邏輯訊號。此外,使用ILA時,工程師只有狀態模式可供使用,不支援定時模式,使工程師無法觀察訊號間的關聯性,也不能量測非同步事件。 |

|

| 圖2 FPGA內部邏輯分析儀可透過JTAG介面與MSO溝通邏輯資訊。 |

即便使用ILA進行FPGA的方式限制不少,但該技術仍被廣為使用,許多供應商提供兼具ILA和多工器的混合除錯解決方案,以提高量測靈活性。另外,許多混合訊號示波器提供JTAG解碼軟體,以便直接在示波器上分析ILA輸出的邏輯訊號。

某些狀況下,類比量測是不可或缺的功能。能看到FPGA底層的類比訊號,將有助於工程師發現與了解邏輯元件的異常行為。儘管如此,對於最先進的FPGA而言,類比和數位訊號對於元件效能都有關鍵性的影響,因此工程師需要真正的混合訊號來進行測試與除錯。

類比量測有助發現FPGA異常

隨著業界不斷研發速度更快的乙太網路(Ethernet)裝置,高速FPGA收發器的需求也持續攀升。業界已經開發出每通道速率達10Gbit/s的CFP模組,實現100Gbit/s乙太網路裝置。現正開發的第二代100GbE採用4×25Gbit/s的架構,可整合入CFP2模組,最終將整合CFP4模組。

為支援標準所要求的25Gbit/s串列資料通道,FPGA業者進一步將收發器速率推升至28Gbit/s,以加速實現更新一代16×25Gbit/s的400GbE技術。

當工程師設計與量測速度達28Gbit/s的串列資料流時,須處理許多類比訊號的問題,包括插入損耗、訊號反射、串擾等。有一些類比訊號問題在資料速率小於1Gbit/s時可完全忽略,但是在28Gbit/s速率下卻可能釀成大災難。為了解決這些問題,即時示波器提供訊號完整性軟體,可大幅改善在高資料傳輸速率下進行類比量測的量測品質。

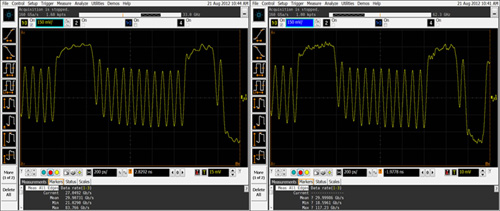

過去工程師認為如果要看到三次諧波(3rd Harmonic),須採用至少提供42GHz頻寬的量測系統,才能量測28Gbit/s訊號,然而,事實並非如此。圖3顯示的28Gbit/s PRBS^7訊號是分別透過33GHz和63GHz的擷取頻寬量測,除63GHz的擷取頻寬會有不可避免的高頻雜訊外,兩個量測結果幾乎毫無差異。將這個訊號進行快速傅立葉(FFT)運算後,顯示三次諧波為30dB,低於基本要求,在實際量測中完全可以忽略不計。最近混合訊號示波器已提供充足的類比頻寬,以便擷取28Gbit/s訊號。

|

| 圖3 混合訊號示波器在33GHz(左)和63GHz(右)擷取頻寬下量測到的28Gbit/s的PRBS^7訊號。 |

針對先進的FPGA進行測試和除錯時,工程師同時面臨嚴苛的數位和類比挑戰。首先,工程師很難探量數位訊號,而且實體接腳數相當有限;再者,當FPGA收發器速率達到28Gbit/s,將會遇到有問題的類比訊號,因此在這個充滿挑戰的環境中進行量測,工程師須採用具備30GHz以上的類比頻寬、優異的訊號完整性,以及十六個數位通道的整合式高頻混合訊號示波器。

(本文作者任職於安捷倫)