MEMS與一般IC封裝方式有極大的不同,為節省成本,業者多選擇採用SOIC的封裝方式,但卻會發生良率低,或是封裝過程中受到應力影響,而導致MEMS元件破裂的問題。為解決此難題,廠商進行多面向檢測,並成功找出合適的晶片外掛材質,有效防止元件受到應力作用而失效的問題。

微機電系統(MEMS)產品的商業化要取得成功,封裝方式扮演極為吃重的關鍵性角色。封裝系統必須要讓MEMS發揮感應的功能,同時還要保護它不受環境干擾,並將測量敏感度提升到百萬分之一的等級。先前以小外形封裝(SOIC)的加速器(Accelerometer)便曾經歷過低度ppm情況,導致元件破裂。

MEMS封裝的重要性,在於它必須維持特定的共振頻率,以便保護感測器不致於卡死(Sticking)或折斷(Clipping)。在此同時,封裝還要能夠讓感測器保持可靠且準確,避免損壞或是輸出誤差。而所謂的多面向方法,亦即涵蓋振動分析、電氣響應偵測、應力分析,以及破裂力學機制等,藉以判斷適當的晶片附掛材質,以徹底解決元件破裂的問題。

MEMS加速計在汽車安全氣囊系統中,作為碰撞感應器之用已超過10年。直到最近,應用範圍又拓展至消費性產品,如行動電話、筆記型電腦、遊樂器以及手持式個人數位助理(PDA)等。加速計產品必須經過兩個不同的製造階段,即感測器的製作及封裝,其中還會用到表面微機械製程,以便製作加速感應計晶片的可動部件與慣性質量。

封裝MEMS元件難度高

要有效地封裝MEMS元件,通常代表必須面臨多項挑戰,同時也是妨礙MEMS技術全面普及與成長的主要障礙之一。

MEMS封裝主要源自於微電子業所研發的技術,與積體電路(IC)相比,前者只須以封裝將電子元件與外界隔離,但是MEMS封裝卻須讓元件能實際接觸外界,或至少能觀測外部環境,以便發揮感應效果,同時還要保護元件不受損壞或是長期故障。感測器封裝的難處,在於除了要提供印刷電路板(PCB)的固定基礎以外,環境或封裝對感測器所造成的應力也不得影響到感測器的性能。

MEMS加速計由特定應用積體電路(ASIC)與MEMS元件封裝而成,而ASIC會將MEMS元件的電容輸出轉換為電壓,以便呈現出MEMS元件所感知的加速量,這個加速度被整合並計算出元件的移動速度。

在安全氣囊的應用裡,當衝擊速度達到一定程度時,氣囊便會爆開。任何MEMS加速計的失真,如封裝應力過大或是元件本身的振動,都可能導致誤報,進而觸發安全氣囊的運作。安全氣囊的爆發感測器必須要能正確感知車輛碰撞的動能,但又必須隔絕它自身所在四週環境震動的響應作用,因此封裝及感測器的動態特性是十分重要的考量。舉例來說,在特定的汽車應用裡,震動訊號頻率可能高達20kHz,如果封裝本身有一種以上的原始模式剛好位於或接近該種高能輸入訊號的頻率,則感測器的封裝輸出訊號將會失真、甚至對感測器造成實際的損害。

飛思卡爾(Freescale)MEMS加速計的感測器是對矽質基板施以表面微機械技術製成。感測器的可動部分會使用蝕刻空腔晶片,以陶瓷材料緊密固定在基板上,並密封以隔絕外界,固定的感測器晶片為已去框、並以晶片附掛固定在無鉛框架上,再以線路連結ASIC晶片,感測器周圍以凝膠包覆,再把整個組件完全密封。基於成本考量,使用16-lead SOIC封裝並排的ASIC晶片和g-cell固定掛載。經研究顯示,訊號失真的主因通常與封裝的共振及晶圓附掛點的共振有關,為矯正這些封裝問題,須重新處理封裝,並改用硬式晶片附掛。但不幸的是,所使用的硬式晶片附掛材質又會引起低度入射導致晶片破裂,因此採用多面向的檢測方法,藉以評估晶片破裂的過程及材質所造成的影響,並提出更好的辦法解決此一問題。

應力/破裂力學檢測防堵MEMS破裂

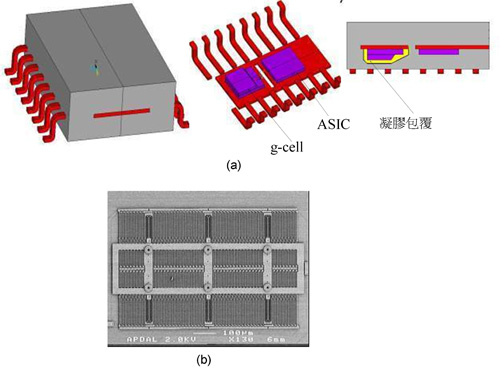

在16-lead SOIC的加速計,其完整封裝模型與剖面圖如圖1(a)所示。封裝由感測器晶片組成,其細部結構如圖1(b)所示,以一個部分延伸至基板、靠近線路固定襯板的外罩結合。ASIC與g-cell並排,晶片附掛在無鉛框架上,另一片極薄的矽晶凝膠則覆蓋在整個g-cell上,然後才完全密封。

|

| 圖1 (a)完整封裝與16 leads SOIC封裝外露的外觀、(b)感測器的掃描式電子顯微鏡影像 |

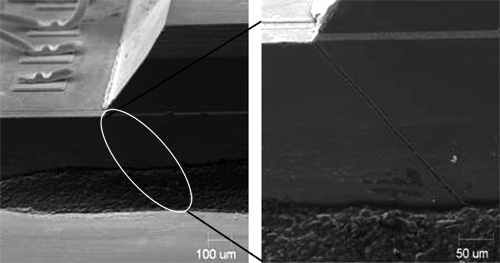

在應用場合裡,震動的環境會要求封裝的自然頻率應該高於20kHz,以便避免造成感測器的共振問題,為達成這一點,原本的四點軟式晶片附掛A必須換成高模化的環氧基樹酯晶片附掛D。低度ppm組件無法正常運作,而且事後發現整個g-cell基板晶片都已破裂,破裂部分整個深入主動元件,如圖2所示。斷面圖分析顯示,破裂起於g-cell基板頂端,沿著基板、陶瓷及外罩之間的表面擴散。破損通常會從切割邊緣開始,部分組件只有一個破裂起點,其他則會有一個以上的起點,因此馬上浮現一個問題,是什麼引起g-cell晶片破裂?是處理、組裝或逆流狀況造成變化的嗎?封裝是否可以重新設計,以增強在用戶或實際應用現場面臨處理、組裝的周遭環境下的可靠性?

|

| 圖2 在g-cell基板上裂縫的掃描式電子顯微鏡影像 |

選擇有限元素分析作為故障分析及封裝再設計的方法。為了診斷出在組裝過程中及暴露於外在環境下的晶片張力及破裂風險,採用兩種方法,首先是傳統的應力分析,其次是以破裂力學機制為基礎的分析。評估的階段包括將外罩晶圓與g-cell基板晶片的結合、g-cell附掛至鉛框架、線路連結、密封、銲劑逆流及熱循環等。

| ‧ |

|

| |

|

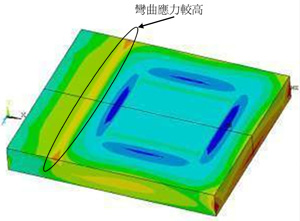

| 圖3 g-cell基板上的最大張力 |

傳統的應力分析可用來找出不同封裝階段的高度應力區域,一般假設晶片邊緣不具缺陷,圖3顯示的就是g-cell基板在密封過程中出現高應力的位置。最高的彎曲應力出現在基板、外罩與陶瓷接合的部位。由於外罩在蝕刻過程中有大約54度的角度,因此會產生幾何性的不對稱,並導致特別的張力高漲區域。該區域的張力值對於網狀格局十分敏感,若調整網格,則張力會愈趨激烈,但是可有效分散張力,高張力區域的位置,正好與所發現的破裂起始位置相吻合。 |

| ‧ |

|

| |

矽晶片的機械完整性與其製程密切相關。此類製程包括晶圓切割、表面處理(研磨、拋光、蝕刻等),以及晶圓成型等。在任一製程中,晶片表面或邊緣都可能出現缺陷,如果缺陷所在位置剛好與張力高漲的區域相吻合,那麼晶片的可靠性在後續的封裝及品管測試過程中就可能受到影響。在表面機械性分析時,假設在基板的關鍵性位置存在一個既有的缺陷,這個假設的缺陷大小大概是晶片厚度的1/300。應力能量的釋放率G則代表使裂縫擴大的能量,可以公式1定義:

.............................公式1 |

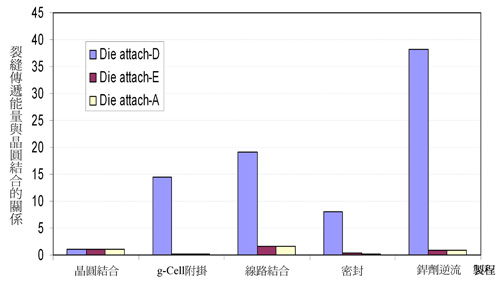

Γ表裂縫尖端四週的任何可能路徑;W代表應力能量;Ti代表牽引向量;ui代表位移向量,nx則是Γ向外的單位正規量的x分量。從晶圓結合、晶片附掛、線路結合、密封到逆流等封裝過程,都以模型模擬,而與晶圓結合時有關的裂縫擴散能量則顯示在圖4。可以看出,現行採用的晶片附掛材質Die attach-D,以及焊接劑逆流,是導致裂縫擴大的主要過程,先前沒有裂縫的相同產品,在設計時採用的是Die attach-A。從圖4看來,發現在採用Die attach-A時,裂縫擴散的機率比採用Die attach-D時低得多,然而Die attach-A會在封裝固定到線路板時造成共振問題,因此要如何選擇正確的晶片附掛,才能避免晶片破裂,但又不會造成共振,即為解決問題的關鍵。

|

| 圖4 在每個封裝過程中所產生的令裂縫擴大的能量 |

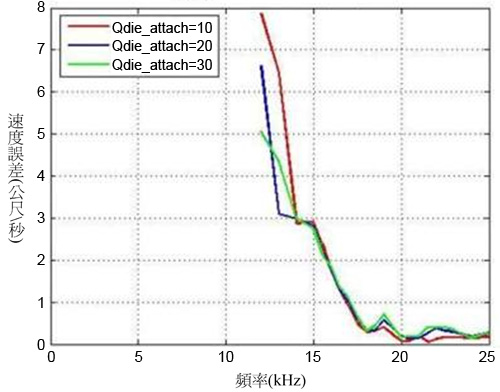

由於晶片附掛材質會造成晶片破裂,因此評估多種材料。原本的Die attach-A會在7kHz時引起g-cell共振,進而導致訊號失真問題,接著以Die attach-D取代,其共振頻率為400kHz,因此不會形成失真問題,然而卻會影響已有裂縫的晶片。於是須設法在共振頻率與硬度間尋求合適的晶片附掛材質,圖5即用來顯示晶片附掛的共振頻率必須要保持在何種狀況下,才能避免失真。許可與否的關鍵,即在於速度必須低於1m/s。圖5指出,不論晶片附掛的Q值為何,其最低共振頻率都在約17kHz。

|

| 圖5 速度誤差與晶片共振頻率的關係 |

晶片附掛材質選擇至關重要

廠商的MEMS加速計設計兼具可動式與固定式的基板。一旦g-cell的頻率達到切割點,機械(Mechanically)MEMS的中央基板就會遇到阻擋,以避免它觸及感應基板的上下部分,進而造成阻力與短路。標準製程則會引起MEMS元件的誤差,其不對稱又影響到上下方基板的阻擋,最後導致高度加速輸入訊號時的輸出失真,若已達晶片附掛的共振頻率時,失真會再乘以Q倍。

球體墜落測試的目的則是要偵測失真,並改善元件的能力。測試時,金屬球會掉落在一片懸吊的不鏽鋼板上,當球體撞及基板時,會產生多種不同的頻率。如果MEMS加速計發生失真,那麼積分得出的速度就不會回到0kph的初速。

在圖6中,硬式Die attach-D的響應較為理想、亦無失失真,但是Die attach-A就有-0.2kph的失真誤差。根據球體墜落測試,g-cell切割點頻率約在20kHz,任何高於該數值的封裝頻率都不會引起共振問題。此外,針對使用不同晶片附掛的封裝,進行有限元素模型分析,這裡只有第一和第二種自然頻率的模式標示出來,因為在平面動作上,只有它們與跟g-cell的X軸及Y軸有關聯。各種晶片附掛材質屬性,以及相對應的封裝共振頻率。這些材質約可歸類為兩大類,硬式Die attach如#D可滿足封裝共振限制,但會造成晶圓破裂;軟式Die attach如#A則不會導致破裂,但是其封裝卻無法滿足共振限制。

|

| 圖6 各種晶片附掛進行球體墜落測試時的速度 |

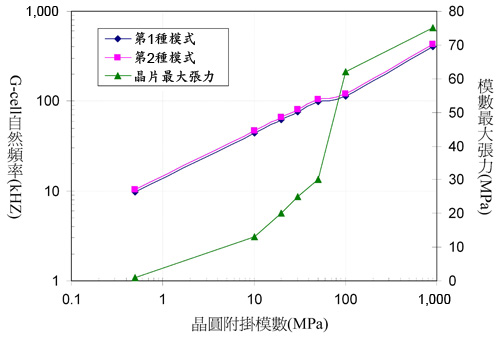

MEMS業者又做了研究,設法找出最適合晶片附掛材質的屬性範圍、其對於封裝共振的影響,以及晶圓的應力。圖7呈現的是g-cell的自然頻率對晶片附掛模數的函數,以及有關的g-cell基板最大張力。

|

| 圖7 g-cell基板最大張力與封裝共振頻率對晶片附掛模數的函數圖 |

可發現,晶片張力對於晶片附掛模數的敏感程度,要比對於熱膨脹係數變化來得高。根據圖7,也可看出晶片附掛材質模數如接近10時,晶片張力便會較低,因此可以滿足共振頻率的限制。

|

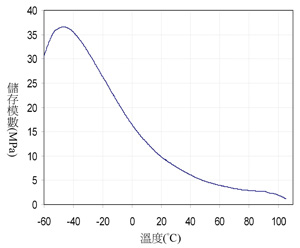

| 圖8 晶片附掛E的儲存模數 |

經過研究,發現晶片附掛材質E可滿足既定的需求。為確保使用新材質的晶片共振效果,須測量某溫度範圍內的材質模數。這是透過一種稱為動態機械性分析(Dynamic Mechanical Analysis, DMA)的方法,將材質塗布在中空的平面上,再加以處理作為樣品,然後將樣品置於各種溫度下進行測試,材質模數如圖8所示。

封裝的模態分析及晶片附掛E的內部特性顯示,其自然頻率高於20kHz。此外,圖8也顯示晶片附掛E的裂縫傳遞能量相當接近晶片附掛A,因此破裂問題應不至於擴大。以晶片附掛E取代晶片附掛D,就可以一方面不讓裂縫擴大,又有足夠的硬度可以避免共振,此種新晶片附掛材質的封裝品管測試與製造經驗都顯示,所有受測樣品都不復見晶圓破裂的問題。

晶片附掛E解決SOIC封裝問題

16 leads SOIC加速計封裝所經過的全部流程都經過裂縫擴大傾向的調查,該傾向會導致低度ppm時的晶片破裂問題。MEMS業者找出兩個損害程度最嚴重的製程步驟,最糟的就是焊劑逆流和隨後的線路結合階段,導致晶片破裂的主要因素就是g-cell晶片附掛的硬度。目前的晶片附掛D會使得g-cell基板晶圓非常易於破裂,因此採用逆向工程法尋找合適的晶片附掛,既要能滿足g-cell的自然頻率,又要符合封裝可靠度的需求,而改用晶片附掛E之後,封裝變得更堅固,足以因應一般因處理過程而來的缺陷,同時也能兼顧g-cell的自然頻率需求。

(本文作者皆任職於飛思卡爾)