透過模型化設計工具、SoC FPGA和整合隔離、電源、訊號調節和測量元件的智慧類比前端驅動方案,馬達驅動系統設計、驗證、測試和實現將更加快速,從而縮短產品上市時間,且能兼顧性能要求。

現代馬達控制系統很重視控制迴路性能,希望藉此降低能源消耗,減少震動,以及做到精確的速度、位置和轉矩控制。這表示控制器須具有快速更新速率,並能量測電流、電壓和位置等馬達參數,以執行高性能演算法,而類比前端技術的要求亦不下於控制器端。對此,現場可編程閘陣列(FPGA)具有高速平行處理能力,可支援即時計算密集型的控制演算法,如磁場定向控制或模型化控制器,此外,多個控制器可整合到同一個FPGA中,以進行高精度多軸機台控制,且不會有性能損失。

舉例來說,新型系統單晶片(SoC)FPGA,即結合FPGA的平行處理能力與中央處理器(CPU)的泛用性,做為實現混合控制演算法的理想平台。在SoC架構下,FPGA將負責密集處理型任務,而處理器子系統則能滿足較慢速的控制迴路、系統監控與使用者介面等應用。

由於SoC架構複雜,因此MathWorks已開發一套模型化設計流程,提供自動生成的控制器模型HDL程式碼,以便直接在FPGA中編程,縮短概念和生產系統實現之間的路徑,並驗證控制系統的實作符合原來的模擬模型。本文接下來將討論SoC FPGA、類比前端(AFE)和相關模型化設計工具,如何有效提升馬達控制性能。

FPGA/模型化設計添力 馬達控制兼顧性能與開發速度

|

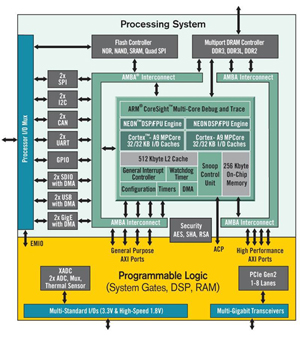

| 圖1 SoC FPGA功能方塊圖 |

現在的電動馬達廣泛用於各種工業和商業應用中,並已成為各種機器、設備與裝置的操作中不可缺少的組成分子,而電動馬達利用規模之廣,由它們占全球40%以上的能源消耗量即可窺見。

電動馬達的動作是由馬達驅動器控制,藉由改變馬達輸入功率來調整軸轉矩、轉速或位置。目前的市場趨勢是建構高性能馬達驅動器,可提高馬達效率,並提供更快、更精確的控制。此將牽動控制迴路設計更新,以及控制演算法、工業網路與使用者介面技術的組合,所以系統須導入更強的處理器,以便即時執行所有任務。

傳統的馬達控制方案係基於多晶片架構,有一顆分離式數位訊號處理器(DSP)執行馬達控制演算法,一顆FPGA實現高速輸入/輸出(I/O)和網路協定,以及一顆分離式處理器負責系統控制。隨著SoC FPGA問世(如賽靈思Zynq All Programmable SoC),馬達控制器可結合CPU通用性和FPGA強大的處理能力,將所有功能整合到單一元件。

SoC的好處在於能以合適的運算核心處理不同任務,進而縮減系統功耗。例如系統控制、監控、診斷和使用者介面支援可由CPU執行,而密集型任務如控制演算法與網路,就會被卸載到SoC的可編程邏輯元件(PLD)。一般情況下,可編程邏輯容許多個控制核心平行處理以控制多軸機台或多重系統,在單晶片上具有完整的控制器可讓硬體設計更簡單、更可靠且成本更低。

過去幾10年,模型化設計一直是FPGA產業熱烈討論的話題,但一直到最近幾年,隨著MathWorks的Simulink模型化設計工具出爐,FPGA才具有完整的設計流程(從模型創建到完成實作)。模型化設計正在改變著工程師和科學家們的工作,將設計任務從實驗室和現場移動到桌面上。

現階段,包括受控體(Plant)和控制器,整個系統都可被模型化,讓工程師觀察控制器的行為並加以調整,以前則必須在現場實作。這有幾個好處,例如減少損壞風險,加快系統整合和減少對元件可用性的依賴;一旦工程師完成控制器的模擬模型,在SoC FPGA上執行的C和HDL可自動產生,既節省時間,也避免人工撰寫程式碼時出錯,再藉由鏈接系統模型到快速原型環境,進一步降低控制器系統開發風險。

SoC FPGA滿足各種控制演算法需求

先進的馬達控制系統須執行控制、通訊和使用者介面等任務組合,各有不同的處理頻寬和即時性要求,所以實現這種控制系統的硬體平台必須是可靠且可擴展的方案,透過圖1結合可編程邏輯和高性能處理系統的SoC FPGA,將能提供出色的平行處理、即時控制和I/O連接多樣性,滿足所有設計要求。此外,業界最新的SoC FPGA還整合類比數位轉換器(ADC),可連接類比感測器用於系統監測。

SoC FPGA處理系統端由一個雙核心安謀國際(ARM)Cortex-A9處理器、Neon協同處理器和浮點運算單元(FPU)組成,以加速軟體執行。該處理系統用來解決影像監控、運動控制、系統管理、使用者介面和遠端維護的功能,這些功能都很適合用軟體實作。此外,雙核心ARM處理器還可支援嵌入式Linux或即時作業系統,增進系統功能。

至於可編程邏輯端,可支援多達444,000個邏輯單元和2,200個DSP處理分割(Slice),進而提供大量處理頻寬。FPGA屬於可擴展架構(Fabric),因此用戶可從28,000個邏輯單元到444,000個邏輯單元的範圍內客製化元件功能,搭配DSP功能區塊,可解決各種馬達控制的訊號處理問題。

SoC FPGA透過五組高傳輸量的AMBA-4 AXI高速互連介面緊密結合可編程邏輯的處理系統,相當於三千多支接腳的有效頻寬,因此非常適合用來實現時間敏感型與處理密集型任務,如即時工業乙太網路協定或控制演算法,並可容納用於多軸機台或多重系統控制的多個平行控制核心。

模型化設計工具降低開發風險

|

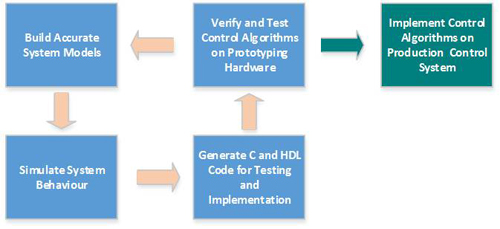

| 圖2 馬達控制演算法設計的工作流程 |

另一方面,模型化設計工具對提升馬達控制方案的品質和開發速度亦扮演關鍵角色。MathWorks的Simulink是一種方塊圖環境,用於多域模擬和模型化設計,非常適合於模擬受控體系統模型,以及調節轉速、扭矩、精密定位和其他性能變量的馬達控制演算法。利用模擬評估控制演算法是一種非常有效的方法,對於確定馬達控制器設計的適宜性,並於確定要進行昂貴的硬體測試之前降低演算法開發的時間和成本。

圖2描述一個設計馬達控制演算法的高效率工作流程,可按照以下步驟:

模型化設計工具可提供業界標準演算法及應用程式進行系統分析、設計和調整線性控制系統,以及元件庫和分析工具進行模型化和模擬系統,涵蓋機械、電氣、液壓等物理領域。在移到真正的實體實現之前,這個模擬環境對驗證功能邊界和極端操作條件而言是很理想的,可用以驗證控制系統的行為和性能,避免現實生活中的操作發生危險。

透過如MathWorks模型化設計工具中的嵌入式編碼器(Embedded Coder)和HDL編碼器工具,讓控制系統在模擬環境中獲得充分驗證,使用者可以Embedded Coder生成C語言程式碼,並以HDL Coder生成VHDL或Verilog,然後將程式碼部署到硬體原型進行測試,之後到最終生產系統。此時,軟硬體實現的要求如定點和時序行為會被指定,自動程式碼生成有助於減少從概念到實際系統實作所需的時間,並避免引入人工程式撰寫錯誤,確保實際控制器的實現與模式相匹配。

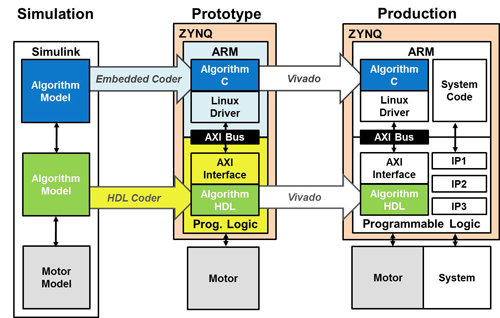

圖3描述在以Simulink進行一顆馬達控制器模型化在現實生活中所需的步驟,並將其轉移到以賽靈思(Xilinx)Zynq SoC為基礎的最終生產系統。第一步是在Simulink下,對控制器和受控體進行模型化和模擬,在此階段,控制器演算法被劃分為二:將以軟體實現的方塊,以及將要到可編程邏輯中實現的方塊。

|

| 圖3 馬達控制系統從模擬到生產的路徑圖 |

一旦分區和模擬動作完成,控制器模式便會使用Embedded Coder和HDL Coder轉換為C程式碼和HDL。基於SoC的原型系統被用來驗證控制演算法的性能,並在移到實際生產階段之前進一步調整控制器模型;在生產階段,自動生成的C程式碼和HDL被整合到複雜的生產系統框架之中,此工作流程確保設計完全通過驗證和測試。

此外,選擇正確的原型硬體在設計過程中是重要的步驟,後面將討論如何有效地使用新一代類比前端驅動器套件,以快速製作馬達控制系統原型。

智慧型驅動器套件快速製作系統原型

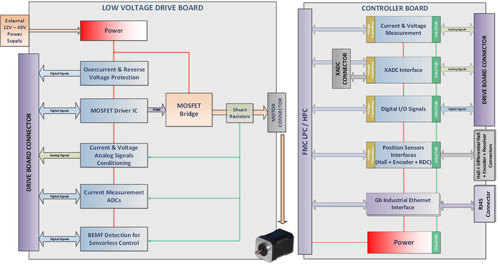

SoC FPGA加上高精密度資料轉換器和數位隔離方案,可提供高性能馬達控制和兩組Gigabit乙太網路的工業網路連接。此一套件附有一塊完整的驅動模組(圖4),對多種馬達類型均可有效控制,此外,該套件可使用亞德諾(ADI)的AD-DYNO1-EBZ測力計再擴充,這是一種動態可調負載,可用於即時測試馬達控制性能。

|

| 圖4 馬達控制智慧驅動器功能方塊圖 |

該控制器板是一片專用於連接到任何一款賽靈思FPGA或SoC平台的混合訊號FPGA夾層卡(FMC),以及低接腳數(LPC)或高接腳數(HPC)的FMC連接器,這些元件的特點如下:

在任何馬達控制系統中,隔離是一個既為控制器也為用戶提供防護的必要設計。控制器板卡上類比和數位訊號的完全隔離,可確保FPGA平台始終受到保護,避免可能出現在馬達驅動側的危險電壓。

驅動板包含驅動馬達所需的所有電力電子元件,以及電流/電壓檢測和保護電路。以下是驅動板的特點:

類比前端元件強化參數量測功能

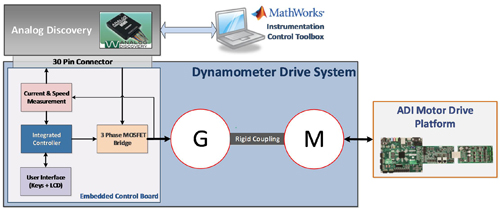

測力計是一個動態可調負載,可用於測試即時馬達控制性能。由兩個BLDC馬達透過剛性連接直接耦合。其中一顆BLDC馬達當作負載,由嵌入式控制系統所控制,第二顆馬達由智慧型驅動器套件所驅動,如圖5所示。該系統配備使用者介面,用以顯示有關目前由負載及其速度所產生的資訊,並可設置不同的負載設定檔。外部控制可直接透過Analog Discovery USB示波器達成,負載訊號擷取和控制可採用MathWorks的儀表控制工具箱,直接由MATLAB取得。

|

| 圖5 測力計架構圖 |

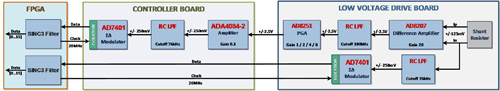

任何電動馬達控制系統的性能受到馬達電流和電壓測量的品質影響甚鉅。經由使用高性能類比訊號調節元件和ADC,智慧型驅動器套件將提供精確的電流和電壓測量,測量路徑在控制器和驅動板之間做一劃分,如圖6。

|

| 圖6 相電流訊號鏈 |

相電流是使用分流電阻檢測。在這裡依量測技術有兩個可能的測量路徑,一種是ADC可放置在靠近分流電阻處,另一種是ADC不能放置在接近分流電阻處,這兩種技術都致力於獲得最佳的測量精度。

當ADC放置在分流電阻器的附近時,分流電阻器和ADC之間的訊號路徑很短,不易發生雜訊耦合。在分流電阻上的小差動電壓可由隔離式ΣΔ調變器直接測量,不需要額外的介面和訊號調節電路。由於類比訊號在靠近訊號源處進行數位化,並以數位格式傳送到FPGA,因此不須特別注意測量的品質。

當ADC不是放置在分流電阻器的附近時,分流電阻器和ADC之間的訊號路徑長,很容易產生雜訊耦合,特別是驅動馬達的功率級會有開關雜訊,以及馬達本身產生的雜訊,此時必須在ADC和分流電阻之間加入適當的設計訊號調節電路,並對送往ADC的類比訊號加上完善的屏蔽。在分流電阻上的小差動電壓由驅動板上的差動放大器放大,應該靠近分流電阻放置,以避免雜訊耦合。該訊號從±125毫伏特輸入範圍放大到±2.5伏特,以減少耦合雜訊影響。

放大後的訊號進入驅動板上通過另一個可編程放大級,確保ADC在接收輸入訊號後調整成適當比例,以符合其輸入範圍。透過連接器將放大的類比訊號送到控制器板,該連接器針對每個類比訊號都有適當的屏蔽,以減輕雜訊耦合。從驅動板送來的類比訊號在控制器板上使用放大器將電壓平移回到適當的輸入範圍。

在電流和電壓回授訊號鏈中最重要的元件是二階隔離式ΣΔ調變器,這種高性能ADC具有16位元解析度、13.3有效位元(ENOB)和83dB的訊噪比(SNR)。數位介面有兩組數位訊號線:高達20MHz的時脈輸入端和一個1位元的數位資料流輸出。

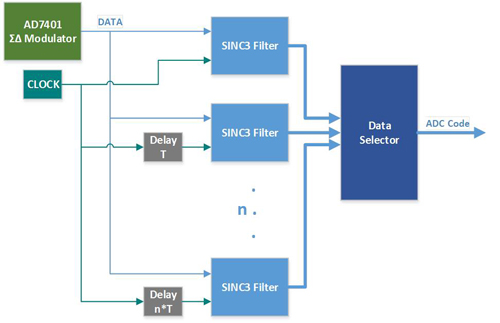

實際的ADC程式碼使用數位濾波器重建。在資料表中提供一個濾波器模型和HDL實作,可提供一組16位元輸出碼和78kHz取樣率。輸出程式碼的解析度和取樣率可藉由改變濾波器模型和抽取來控制。而78kHz取樣率在許多應用中可能就足夠,當然還是會有要求更高取樣率的情況,在這些情況下如圖7所示,用濾波器組增加系統的取樣速率到高達10MSPS用於純16位元資料。

|

| 圖7 濾波器組 |

濾波器組包含n個SINC3濾波器,其取樣時脈有一些延遲,等於延遲時間T的倍數,T則等於一個SINC3濾波器的傳播時間除以濾波器組的數量。一個資料選擇器方塊以相等於延遲時間T的週期性選擇適當的輸出碼。

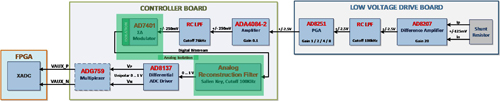

相電流的量測也可使用FPGA中的XADC執行,該訊號測量鏈利用常規量測鏈的完整路徑,並加在控制器板上的隔離式ΣΔ調變器之後,使用運算放大器實作一個Sallen-Key的類比重建濾波器,如圖8所示。隔離式ΣΔ調變器和類比重建濾波器之間的結合提供一種方便和廉價的方式實現了XADC輸入訊號的類比隔離而不會影響量測的品質。

|

| 圖8 8 XADC訊號量測鏈 |

借力軟硬體設計工具 馬達控制性能/成本更出色

整體而言,智慧型驅動器套件提供一套控制器模型,一個完整的SoC FPGA開發框架,一個Linux基礎架構,讓使用者能順利完成設計一個馬達控制系統所需要的所有步驟,從模擬開始,接著製作原型機,並落實生產系統的實現。

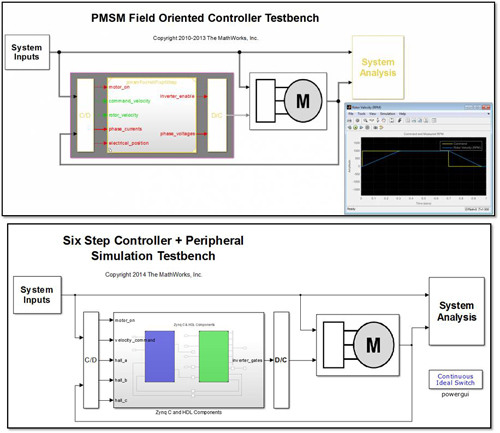

由MathWorks提供的一個六階控制器和一個永磁同步馬達FOC控制器,可用來開始設計流程。圖9顯示這兩個控制器的頂層圖,六階控制器實現一個BLDC馬達的梯形波控制器,而FOC控制器則提供一個FOC核心可被整合到控制系統中。

|

| 圖9 Simulink控制器模型 |

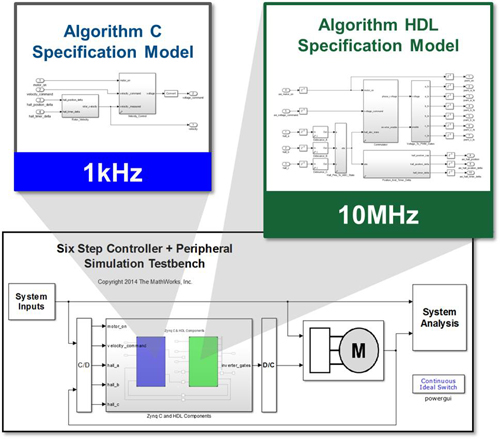

在模擬階段,受控體及控制器模型都要創建出來,對整個系統的行為進行模擬以驗證控制器是否按預期執行。控制器模型被劃分到不同的元件,分別以C和HDL來實作,並受到像時序、定點實作、取樣率和迴圈次數所限制,這些值被指定以確保控制器模型的行為就像在實際硬體實作中所作的一樣。圖10顯示軟體和HDL之間六步驟控制器的分區。

|

| 圖10 以C程式碼和HDL劃分控制器 |

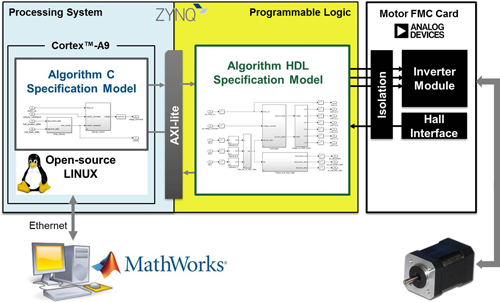

一旦控制器在模擬下充分驗證過,下一步就是移植到原型硬體平台上。SoC FPGA導向工作流會從Simulink模型生成C和HDL,分別針對ARM核心和可編程邏輯子系統。在此工作流程下的HDL編碼器生成HDL,目標為可編程邏輯,同時嵌入式編碼器生成C程式碼,目標為ARM CPU。圖11顯示控制器的實作以及與智慧型驅動硬體的關係。

|

| 圖11 在原型系統上控制器的實現方法 |

該位元流和可執行碼載入到實際硬體,就可開始控制器的操作測試。硬體迴路(HIL)測試可使用Simulink,以及Linux作業系統,之間用乙太網路連接來進行。例如軸轉速等馬達參數可在Simulink上擷取,並比對模擬結果,以確保實體系統實作與模型匹配。圖12顯示模擬結果,並從硬體上擷取實際資料之間的比較,結果的相關性為受控體及控制器模型提供信心,並確保模型和物理系統的匹配,一旦控制演算法的測試完成後,控制器可被轉移到生產系統。

|

| 圖12 模擬和硬體結果比較圖 |

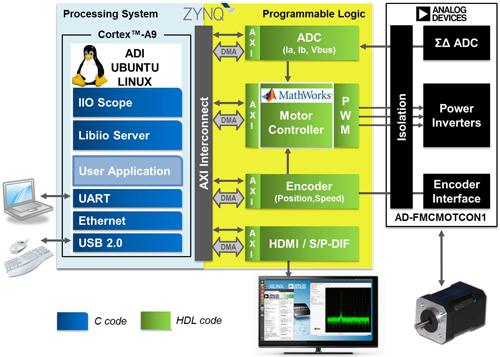

所有的IP都有低速AXI-Lite介面進行配置和控制,而高速AXI串流介面則能夠通過直接記憶體存取(DMA)通道傳送到軟體層的即時資料。高速乙太網路介面可使用ARM處理系統的硬體MAC周邊或乙太網路IP在可編程邏輯中實現。包括與智慧型驅動器硬體連接所需要的Linux IIO驅動程式,進行監測和控制的IIO SCOPE使用者空間應用程式,還有libiio伺服器能使即時資料擷取和系統控制介面透過TCP與用戶端一起在遠端電腦上執行,以及用在控制器的Simulink模型上,包含由嵌入式編碼器所生成的C程式碼在內的可選使用者應用程式等。

綜上所述,由智慧型驅動器套件所提供的Linux軟體和HDL基礎架構,對原型馬達控制應用是非常理想的環境。

(本文作者Andrei Cozma任職於ADI,Eric Cigan任職於MathWorks)