在製程技術發展速度漸趨緩慢之下,近年來系統單晶片的多功能整合進展速度也隨之趨緩。雖然行動通訊等產業對微型化元件的需求仍然殷切,但在現有的技術條件下,若要追求更高的設計整合度,系統級封裝往往才是最具成本效益的解答,也從而帶動業界投入推動SiP技術發展的浪潮。

近年來,半導體業界經常出現「摩爾定律到底還能再走多少年?」這個總是掀起各方激烈論戰的話題。事實上,即使半導體製程技術還能繼續演進,高昂的製程成本也使得半導體業者在採用先進製程開發整合度更高的元件方案時,必須承擔更高的風險。目前除了處理器、記憶體、可編程邏輯、繪圖晶片等高密度元件還有足夠的動力亦步亦趨地採用最尖端的製程技術外,其他元件多半都還在採用兩個世代甚至更久之前的製程技術。

|

| 圖1 工研院電子與光電研究所副所長洪勝富認為,發展立體堆疊技術將是台灣通訊相關半導體未來十年榮景之所繫。 |

工研院電子與光電研究所副所長洪勝富(圖1)略帶感嘆地表示,不論摩爾定律還能再走多久,晶片開發者都已經不像以前一樣,只要過一段時間,就可以有更多電晶體資源來實現更高密度,整合更多功能的晶片了。正因如此,從多晶片封裝(MCP)技術延伸出來的系統級封裝(SiP)技術,成為半導體業界近來的顯學之一,不僅各家大廠積極介入布局,許多技術組織跟團體也紛紛跳下來進行專利布局,一場技術卡位戰已然開打。

各方勢力搶進SiP技術前瞻研發

其實,若單從硬體封裝的角度來看,SiP已經相當成熟了。像是手機、數位相機的處理器加上記憶體晶片封裝、無線射頻模組晶片等產品,都已經在市面上相當常見。但洪勝富指出,若是考量到未來行動裝置的應用需求,SiP其實還有很多尚在開發階段的關鍵技術,如直通矽晶穿孔(TSV)(圖2)等可實現新一代三維IC(3D IC)的技術便是其中最受到各方矚目的新興SiP技術,因此北美、歐洲、日本的晶片公司與技術研發單位,在最近幾年來投入研發或彼此策略合作的消息便時有所聞。

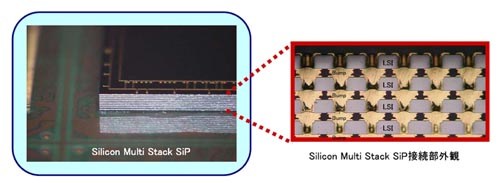

|

資料來源:瑞薩

圖2 TSV是實現極高密度封裝的關鍵技術之一

|

局勢到了2008年下半年突然變得異常熱絡,光是2008年下半年期間,全球各地的技術組織便總共召集了十三次3D IC大型技術會議或技術論壇活動,藉此對外展示其研發成果並進行專利權交易。台灣的工研院在2008年中也出面號召台灣的產業鏈上下游一同成立AD-STAC聯盟,希望能透過資源整合與凝聚共識的方式,將台灣垂直分工的產業鏈整合成虛擬整合元件製造商(IDM),才能和世界各國的晶片IDM大廠在3D IC領域一較高下。

從全球半導體產業陸續在SiP相關領域展開更積極的專利布局動作,就可看出3D IC技術的重要性,已經廣為業界認同。事實上,工研院投入相關研究已有3年左右,期間也累積了不少開發經驗與知識產權,因此就技術層面而言,台灣發展3D IC技術其實一直保持在世界領先集團中。然而,技術研究歸技術研究,從技術走到商品又是另一回事,偏偏台灣的產業型態其實對於推動3D IC商品化發展而言,是有些不利的。

IDM擁有發展SiP技術的 巨大優勢

洪勝富分析,雖然台灣的半導體產業鏈靠著徹底的分工切割而在營運效率上取得傲人的優勢,但在3D IC的時代,IDM似乎又有機會扳回一城,因為IDM公司先天上比垂直分工的營運模式具備較多優勢,其中之一就是晶片布局的詳細資訊可以在公司內部快速流通,不同的晶片設計團隊可以在進行晶片設計時,知道自己的最終設計會被如何封裝成SiP,在進行電路布局時,也可以較快因應其他同事的設計作協調的動作。

相較之下,台灣的晶片設計公司通常只專注在某一項產品開發上,就算了解客戶最終會利用SiP技術將自家的晶片與其他供應商的晶片整合在一起,也不見得能順利拿到第三方晶片供應商的電路布局資訊,更遑論對此做出設計因應了。 工研院AD-STAC聯盟的誕生,就是為了替這個問題找出解套方案。希望能藉由晶片設計的標準化,讓參加聯盟的半導體供應商與相關業者,都有一個統一的規格可循,這樣才能確保晶片最終在進行立體堆疊時的設計與製造過程能順利進行。

已經在SiP領域耕耘近10年,且在全球各IDM廠商中SiP業務規模名列前茅的日商瑞薩(Renesas)科技株式會社系統解決方案事業群SiP開發中心經理海野雅史在接受本刊採訪,聽到台灣AD-STAC聯盟的目標時,便表現出訝異與懷疑的態度。

海野雅史指出,SiP產品要成功,不同元件供應商之間溝通協調的工作確實相當關鍵,瑞薩有許多系統單晶片(SoC)在設計時,的確會將後續封裝製程和與其他第三方晶片供應商搭配等問題納入設計考量。但跨公司之間的SoC線路布局要標準化實在是件大工程,而且不同的SoC設計有不同的布局考量,真的能取得業界共識嗎?

洪勝富也坦承,要替台灣的半導體業界在進行邏輯設計時訂立一套可以依循的標準,以滿足SiP封裝設計的需求,是一件非常艱鉅的任務。事實上,不光是晶片設計業者、晶圓代工廠、後段封測業者必須通力合作,更上游的電子設計自動化工具廠商、半導體設備業者、封測機台業者甚至相關的化學用品供應,都必須一起為SiP的未來發展提供新的解決方案(圖3)。洪勝富說︰「這絕對是一場無可迴避的供應鏈競爭,因為在SoC發展已經面臨撞牆期之際,若要滿足未來行動通訊等應用市場對於微型化、高效能產品的需求,3D IC將是必然要走的一條路。」他並強調,唯有在3D IC領域作出成績,台灣通訊跟消費性半導體產業未來10~15年的長期競爭力才能有保障。台灣業界在這場競爭中,有輸不得的壓力

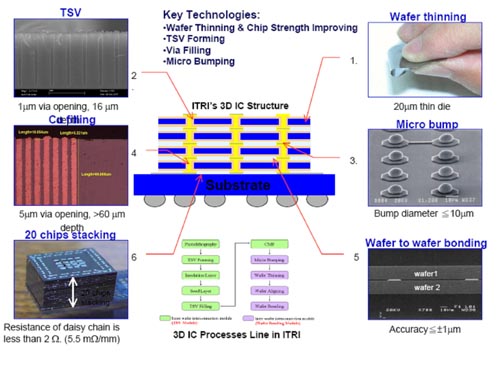

|

資料來源:工研院

圖3 TSV技術牽涉到眾多廠商間的彼此配合,整合難度不在話下。 |

先進堆疊技術將為通訊應用帶來新利多

直通矽晶穿孔技術一旦導入量產,將對行動通訊裝置如手機、可攜式導航裝置(PND)等產品所使用的元件帶來許多性能與功能上的改善。首先受益的將是手機記憶體,其堆疊層數將可望在封裝厚度不變的前提下,輕鬆地將裸晶堆疊的層數提升到七層以上。因此,即使不採用更先進的製程來生產記憶體晶片,手機記憶體元件的密度亦可以倍數成長。

但洪勝富指出,對TSV技術而言,封裝手機記憶體只是牛刀小試而已,因為記憶體的輸入/輸出接腳數在各種半導體元件中算是非常少的。TSV技術的真正威力,要運用在邏輯封裝上才能完全展現,因為TSV技術可輕鬆地實現上萬條晶片內部互連通道,其應用潛力甚至超過目前最複雜的邏輯晶片設計需求。

此外,TSV技術亦有助改善晶片內部連線的效能。眾所周知,打線製程所使用的導線越纖細,導線上的寄生電阻會使得電路延遲的情況越惡化,這點對於一些需要低延遲的高效能應用,如高速或高解析度影像擷取等,會造成不少問題。

這個問題其實存在已久,以手機應用為例,許多應用處理器大廠早在多年前就已經推出可處理千萬畫素相片的平台,但由於以現有的封裝技術一方面不足以提供足夠的記憶體給相機模組作為資料暫存使用,另一方面影像感測器到處理器之間的電路連線延遲時間過長,也使得手機處理器無法即時地從相機模組取得資料,因此時至今日,手機的照相功能都還未完全運用到應用處理器所能提供的全部效能。

事實上,AD-STAC聯盟鎖定的第一個TSV應用便是影像感測。希望能利用TSV可提供高密度、低延遲連線的特性,將影像感測器直接與記憶體和後段處理器貼合在一起,藉由縮短訊號傳遞路徑的長度,來提升影像擷取系統的性能。洪勝富指出,為TSV找到適合的舞台,讓TSV技術能夠一鳴驚人,將是吸引更多供應商使用TSV的關鍵。記憶體封裝雖然有很大的市場,但由於其連線數量少,沒辦法讓TSV技術的潛力完全發揮,所以AD-STAC聯盟並未選擇記憶體封裝作為技術載台。

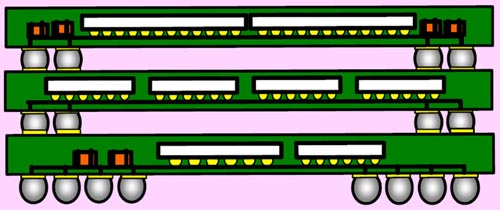

除了向上堆疊外,在各種尚未導入量產的先進堆疊技術中,還有一種向下發展,將晶片埋藏在封裝基板中的新技術(圖4)。海野雅史指出,立體化的封裝技術雖然可以有效縮減元件所占用的電路板面積,但由於行動裝置除了要小巧之外,薄型化也是一大潮流。

|

資料來源:瑞薩

圖4 為了妥善利用所有的空間,瑞薩正在發展將裸晶埋藏到封裝基板中的技術。 |

在目前裸晶厚度已經薄如蟬翼,會因為地心引力的影響而產生邊緣下垂的情況下,晶片本身的厚度已經很難在薄型化方面再有突破性進展,因此向上堆疊的作法總有一天會遭遇到極限,特別是在封裝堆疊(Package on Package, POP)這種整合架構中,元件的厚度挑戰更是嚴苛。

瑞薩科技看見這項隱憂,在幾年前便開始投入向下發展的封裝技術研發,希望盡可能利用所有空間,實現更高整合度。海野雅史指出,這類埋藏式的封裝技術未來在應用方面應該會與POP緊密結合在一起。

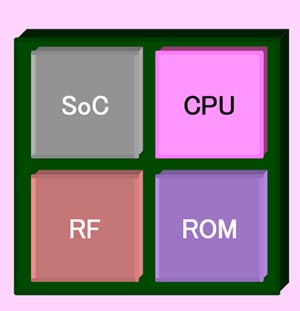

此外,在瑞薩的SiP發展藍圖中,還包含將處理器、SoC、記憶體、射頻電路等晶片都整合在單一封裝中的規畫,其應用目標鎖定在藍牙等高頻通訊領域,可說是SiP的終極願景(圖5)。

|

資料來源:瑞薩

圖5 將異質化晶片整合在同一個封裝中,可說是SiP的最高境界。 |

景氣不佳延遲新技術導入時程

雖然在行動通訊市場的強烈需求下,新一代的SiP封裝技術紛紛出籠,但每一項新技術都須要歷經一段學習曲線。洪勝富便指出,TSV技術由於透過在晶片上蝕刻出貫穿晶片的孔穴以實現連線功能,因此蝕刻技術若不穩定,連線功能就有可能會失效。

對於影像感測器而言,如果失效的連線數量不多,還可以視為是壞點而勉強接受,因為影像的解析度越高,壞點的情況就越不顯眼,但如果是其他邏輯晶片的互連,就不容許出現任何失誤了。

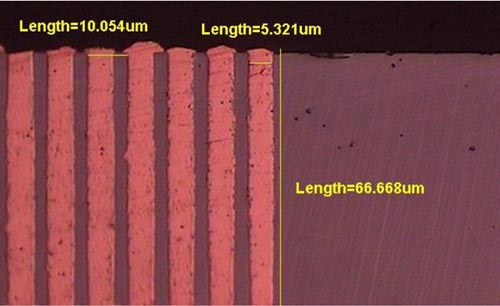

雖然目前工研院已經可以將TSV蝕刻製程所耗的時間壓縮在兩個小時內,但由於應用對製程良率的超高要求,TSV的製程成本勢必會比現有的打線製程來得更高。這對於蝕刻深寬比動輒超過十二(圖6)以上的TSV製程而言,無疑是技術上最大的挑戰,也是工研院和AD-STAC聯盟的廠商要攜手克服的工作 重點。

|

資料來源:工研院

圖6 由於TSV技術需要極高的深寬比,因此製程的控制變成一大技術門檻。 |

海野雅史則進一步表示,業界有些公司在發展TSV技術時,由於導入新的晶圓製程設備,因此其製程成本上升,是必然發生的現象。但不可諱言的是,成本就是TSV導入量產最大的障礙,導入新製程設備,只會進一步延緩TSV的普及。所以瑞薩在研發TSV技術時,特別將不增加新設備機台作為首要考量,希望能藉此壓低日後TSV進入量產時必須反映給客戶的成本。

但即便是以成本為主要考量來進行技術研發,瑞薩自行評估,以目前的技術成熟度來看,TSV的成本還是高於傳統打線封裝。這點非常關鍵,因為在目前這麼不景氣的市況下,如果供應商要推廣新技術,一定要做到成本跟現有技術一樣,甚至更低廉,客戶端接受的意願才會出現。

海野雅史透露,其實瑞薩在2008年便已經完成TSV技術的試產,研發團隊也都已經在進行後續的特性評估等動作,但考量到現在的景氣跟大環境,要推廣一項成本較高的新產品有一定難度,所以瑞薩選擇繼續進行內部研發,將TSV的良率與穩定度提升到更高水準,同時靜待景氣回春,等到客戶投資前瞻產品的意願提升後,再作量產的打算。目前看來,TSV真正進入量產,最佳時機應該會在2010年 左右。

台灣長期在SiP領域耕耘的封裝設計服務廠商鉅景科技也同樣認為,封裝的可靠度將成為TSV導入量產的關鍵。鉅景科技總經理王慶善指出,其實鉅景已經注意TSV製程技術的發展狀態有一段時間了,但從後段封測夥伴與前段晶圓供應商所得到的回應,TSV的良率還是有不小的改善空間,這意味著客戶若是要在這個時間點上利用TSV技術,一定得付出比較高昂的代價。

因此,鉅景認為現階段3D IC除了在設備、製程、材料等領域還要再加把勁之外,找到一個亟須透過TSV技術來改良產品性能的應用也很重要。畢竟每個技術都有學習曲線,TSV也不例外。總是要找到該技術已經能滿足其成本效益需求的客戶或應用,TSV才會有揮灑的舞台。