為因應MID等新一代行動上網裝置之發展,如何縮小零組件尺寸也是重要關鍵。雖採用不同封裝技術各有利弊,但若適當運用蝕刻技術,將可望減少組裝負擔,同時加速開發流程進行。

當今最新的運算平台之一,就是行動聯網裝置(Mobile Internet Device, MID)。只要在小型化手持式運算平台上整合持續上網的功能,一台體積小巧的裝置便能提供消費者完整的上網經驗。傳統行動聯網裝置的物料清單中,可能包含一顆像是凌動(Atom)的英特爾(Intel)架構處理器、一顆系統邏輯晶片、記憶體、大量儲存、無線子系統如3G、無線區域網路(WiFi)、全球微波存取互通介面(WiMAX)等,還有攝影機、麥克風,以及彩色顯示器等。

這類裝置已經在全球掀起一股風潮,並且成為不少業者下一波的營收主力。

而電子裝置的微型化,則是達成尺寸要求的關鍵。僅靠晶片級封裝(Chip Scale Packaging, CSP),仍不足以將PC零組件縮小至手持式裝置的尺寸;但多晶粒記憶體封裝(Multi-die Memory Package)與層疊封裝(Package On Package, POP)堆疊則能提供大量的微型化機會,包括減少IC電路板的面積空間,並縮短連結IC至傳統平面電路板設計的路徑等。

慎選封裝技術有助最佳化電路設計

更進一步的系統層級微型化,則是藉由建置高度整合的模組,將先進的晶片尺寸封裝、層疊封裝堆疊元件、晶粒及被動元件整合至一個微型化基板。

成本對所有的消費性電子裝置而言皆十分重要,行動聯網裝置當然也不例外。先進半導體元件攸關行動聯網裝置的功能優劣,同時也在物料清單成本中占有可觀比例。採用由良裸晶粒(Known Good Die, KGD)製成的多晶片模組,以避免昂貴的重複良率損失因而十分重要。超小型晶片尺寸封裝提供了簡單的方法,在僅略小於裸晶大小的封裝中,能支援完全測試的晶粒,為良裸晶粒問題提供了一個良好的解決方案。

運用異質性POP堆疊,即可垂直堆疊記憶體與邏輯晶片。如此一來就能節省可觀的電路板空間,因為晶片內部線路的走向垂直,且堆疊面積取決於該堆疊中的最大封裝尺寸。英特爾平行匯流排(PATA)介面的固態硬碟就是採用這種POP堆疊技術的例子。晶片級封裝的NAND快閃記憶體裸晶,被堆疊在一個連結至封裝兩側的PATA控制晶片上方。這種作法能在指尖大小的空間如12毫米×18毫米×1.8毫米內,提供小容量IDE硬碟的功能。

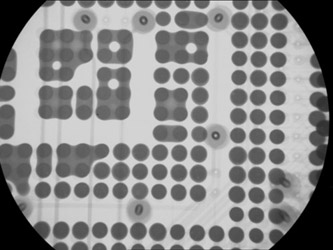

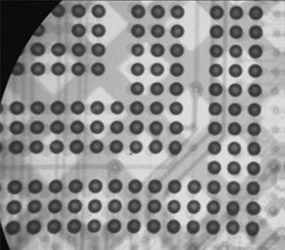

封裝訊號導線(Signal Lead)的間距,最終會限制堆疊元件的面積。最常用來連接晶片級封裝和電路板的技術,就是錫球(Solder Sphere)。當線路間距減少時,錫球的直徑也須隨之縮小。錫球直徑常受限於垂直堆疊的間距,以期能與組件相容。這亦確立了封裝訊號導線間的最小距離(圖1)。

|

| 圖1 線路間距將直接影響錫球直徑 |

|

| 圖2 儘管錫球直徑小於線路間距,仍有可能造成短路。 |

但縮小後的錫球間距,可能在回焊時造成短路。在圖2中,400微米導線間距的封裝,儘管具備低於50微米的共面,但在表面黏著技術(SMT)回焊中仍面臨短路的問題。

最後,POP堆疊組件的錫球,可能在跌落測試中出現故障。元件堆疊的質量,加上業界標準「跌落測試」的震擊力,經常導致堆疊元件連結破裂。若這種情形沒有解決,就會成為可靠性方面的嚴重問題。

新技術克服堆疊難題

為解決上述問題,有業者發展出新的互連技術MicroPilr。該技術以蝕刻銅質接腳為基礎,提供微間距或堆疊應用的許多優點,包括不必連結就能縮小訊號導線的間距;不必減少相同的垂直堆疊間距,就能縮短訊號導線間距;以及減少因跌落測試產生的故障。

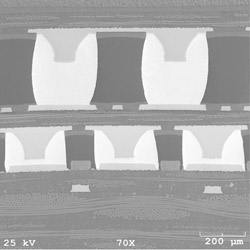

在電子顯微鏡照片的圖例中,顯示一個500微米間距記憶體元件堆疊於一個處理器上方的橫切面,該處理器與圖片中印刷電線板(PWB)連結部分的微間距為400微米。在電子顯微鏡橫切面圖(圖3)及圖4中可看到,焊接點的形狀其實更像是圓柱體而非球體。這是因為這些接腳為「半沙漏形」,可容納不同數量的錫膏,並維持理想的空隙,不會和鄰近的接腳形成短路。若使用較少的錫膏,錫膏就不會堆到和接腳一樣高,但即使在使用不同數量的錫膏時,都仍可形成良好的電氣與機械接觸點。

|

| 圖3 焊接點的形狀也可能影響短路與否。 |

|

| 圖4 接近圓柱體的接腳 |

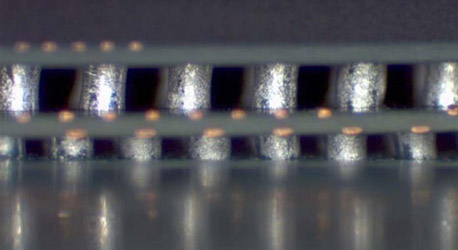

使用MicroPilr技術,可大幅減少微間距錫球BGA的錫膏連結問題。如圖5所示,若採用MicroPilr技術,相同的400微米導線間距,就不會有錫膏相連的情形。

若採用MicroPilr技術,垂直堆疊間距可配合各種封裝的Z軸尺寸,因為接腳可堆疊於小型錫球上方,進而形成如圖6所示的必要間隙。

|

| 圖5 新技術減少了短路的機會 |

|

| 圖6 針腳堆疊可形成必要間隙 |

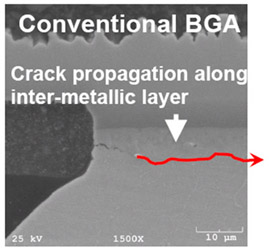

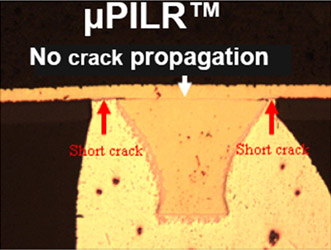

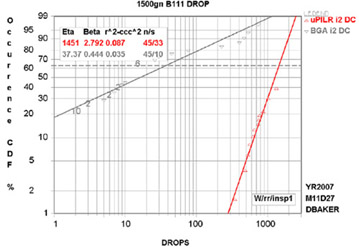

使用MicroPilr技術也能提升錫球通過跌落測試的能力,因為接腳將不再破裂擴散。如圖7橫切面所示,傳統錫球的連結方式會留下許多破裂缺陷。但如圖8所示,銅質接腳不會破裂擴散,因而不會產生接點故障。圖9則顯示MicroPilr與傳統焊錫球閘陣列(BGA)封裝基於錫球所進行跌落測試的結果。Micropilr或BGA都沒有使用底部填充,但MicroPilr表現較為優秀。

|

| 圖7 破裂沿著內部金屬層擴散 |

|

| 圖8 無破裂擴散 |

|

| 圖9 MicroPilr與傳統焊錫BGA封裝之測試比較 |

在微型化方面,MicroPilr互連技術提供行動聯網裝置許多優勢。它十分適合微間距堆疊元件,能比傳統BGA與錫球技術提供更小的導線間距,同時仍維持合理的垂直堆疊間距,不需要過度薄型化的晶粒。因為接腳形狀,以及容許焊料量變化,MicroPilr大幅減少微間距焊料相連的問題。銅質接腳能增加通過跌落測試的成功率,且這種技術能被輕易的建置在標準SMT生產線上。

(本文作者為Tessera台灣區總經理暨東亞區總監)