談及晶片立體堆疊技術,除了近期大為風行的3D IC吸引不少業界目光外,較早問世的其他技術如SiP、MCP與SoC等,也都擁有一定支持者。不過,其中又以SiP能快速因應市場變化,同時符合消費性電子生命週期短之特性,在近期表現亮眼。

在半導體產業各界龍頭之力拱下,由矽穿孔(TSV)技術領軍的3D IC近期風起雲湧,不但掀起諸多話題,也直接挑戰運行多年之摩爾定律(Moore's Law)。不少業者樂觀期待,隨著立體堆疊技術逐步成熟,未來不但電晶體數目可持續增加,晶片尺寸、效能與耗電等議題均可進一步改善,更加適合未來各式資通訊產品之發展。

如科磊半導體(KLA-Tencor)專案總監Irfan Malik便指出,不論是邏輯晶片、記憶體或是互補式金屬氧化半導體影像感應器(CMOS Image Sensor, CIS),最快在2010年下半年便可量產(圖1),無疑是3D IC逐步成熟之最佳佐證。

|

資料來源:科磊

圖1 2009~2011年3D IC之演進路程 |

簡單來說,半導體封裝是半導體晶片的物理保護外層,包括用以連結晶片與晶片運轉系統之電子連線。對於整體產品的微型化與效能,封裝尺寸向來為一項重要限制因素。而若能以先進的技術為半導體產業帶來可靠的封裝解決方案,將可提供消費性電子或其他可攜式裝置更先進的整合與微型化。

舉例來說,晶片尺寸封裝(CSP)由於支援許多封裝類型,包括引線接合、焊線以及各種多晶片封裝解決方案,因此可帶給晶片製造商許多設計選項,以因應產品在實體規格與效能方面的需求。

至於多晶片封裝(MCP)則屬於3D立體解決方案之一,其可針對效能與可靠度進行最佳化,同時也突破尺寸限制,同時降低整體系統成本。相關技術包括結合基板層與錫球堆疊的晶粒堆疊、混合晶粒系統級封裝(SiP)及層疊封裝(PoP)堆疊技術等。

而覆晶封裝(Flip Chip)則是針對高效能、多輸入/輸出(I/O)介面的元件,可提供具備高良率與可靠度的解決方案。其乃是一種將晶片與基板相互連接的先進封裝技術。透過允許晶片與基板互相連接,可降低晶片與基板間的訊號傳輸距離,維持晶片封裝前後尺寸之一致性。

另一種封裝技術則是晶圓級封裝(WLP),它能使廠商開發出更薄、更可靠、更低價的影像感測器封裝解決方案。舊有的晶圓級封裝多以小型晶粒應用為主,卻無法大量運用於如動態隨機存取記憶體(DRAM)及快閃記憶體(Flash)的大型晶粒應用。理想的WLP能可靠且支援高頻率運作,也具備理想的電源整合性。它支援晶圓級測試、提供更低的成本,並能減少晶粒尺寸。

若從晶圓級封裝技術的近期發展來看,其諸多特性將能滿足上述各項需求。例如運用WLP上的兩片金屬層,能提升電源與訊號的整合性。若省略封裝基板,能在各種高速應用中,縮短電路長度。至於在相容元件層頂部加上銅接腳,即能進行晶圓層級測試與預燒。運用重組晶圓搭配WLP技術,能克服晶粒縮小所衍生的問題,且能運用層壓來取代旋轉塗布,並減少微影製程步驟,以降低封裝成本。

不過,儘管3D IC正當紅,也有不少業者抱持保留態度。有業者便指出,儘管3D IC「最快」在2010年便可進入量產,但仍不會是大規模出貨。而相較於尚未全面成熟、不少專業知識(Know-how)尚須累積的嶄新技術,既有技術如SiP、MCP甚至系統單晶片(SoC)也都還有發揮空間。從表1可以看出,3D IC、SoC與SiP各有優勢,不過若從技術演進之成熟度來看,SiP仍是不少業者的首選。

| 表1 SoC、SiP與3D IC 之比較 |

| 種類 |

SoC |

SiP |

3D IC |

| 外型/尺寸 |

Δ |

Δ |

√ |

| 密度 |

Δ |

Δ |

√ |

| 效能(速度、頻率、功耗) |

Δ |

X |

√ |

| 製程完備 |

Δ |

√ |

X |

| 異體整合 |

X |

√ |

Δ |

| 單一訊號處理封裝密度 |

Δ |

X |

√ |

| 大量出貨之製作成本 |

Δ |

X |

√ |

| 中/小量出貨之製作成本 |

√ |

Δ |

X |

√: Best, Δ: Medium, X: Worst

資料來源:工研院

快速問世符合客戶需求 SiP優勢獲青睞

|

| 圖2 創意電子SiP專案總監林崇銘認為,面對更快速、更具競爭性的消費性電子產業,SiP無疑首選封裝技術。 |

創意電子SiP專案總監林崇銘(圖2)即表示,SiP可在極為精密的空間內完成異質整合,且有助提升訊號完整度。尤其針對通訊領域,若部分網路元件之實體(PHY)層難以用奈米製程實現,就須採用兩顆以上的晶片。如此一來,既增加成本又不符合實際。因此若能順利採用SiP方式,便可大規模減輕設計人員與元件設計之負擔,進而為元件本身帶來更多價值。

林崇銘進一步分析,若以今日的消費性電子生命週期來看,新產品從概念到量產的時間均不斷縮短,因此若欲與競爭對手拉開差距,或是快速提供滿足客戶需求之產品,就將需要更快速的晶片設計與封裝模式,而正是SiP得以發揮之處。

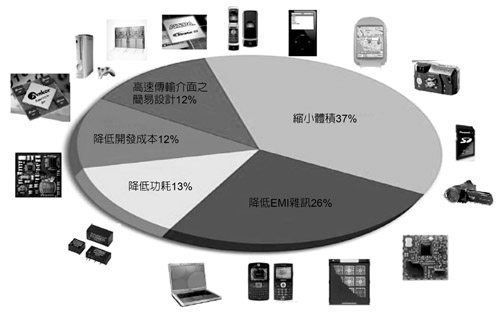

在圖3中可以看出,由於SiP具有的多項優勢,讓消費性電子得以大展身手,同時應用範圍極為廣泛,從手持式裝置到家用遊戲機等均可適用。林崇銘透露,量產多時的SiP,不但在實作經驗上已經獲得不少客戶證實,其不斷演進的技術也成為吸引更多客戶採用的關鍵,因此他對SiP之未來發展仍頗為看好。

|

| 圖3 SiP應用優勢分布圖 |

據悉,自2008年起,創意電子之三成營收即與SiP高度相關,而每四款新晶片設計中,就有一款會以SiP的形式出貨。因此,他認為,SiP封裝無疑是相對成熟的技術。

記憶體成最大動能來源

而若從2008~2013年之半導體產業發展(表2)來看,記憶體占半導體產業比例將持續增加,進而帶動整體產業成長。因此,以記憶體為主力之業者,也紛紛對來年表現表示看好。

| 表2 2008~2013年依半導體產業市場產值(單位:10億美元) 製表者:侯俊宇 |

| 元件\年度 |

2008年 |

2009年 |

2010年 |

2011年 |

2012年 |

2013年 |

CAGR |

| Memory |

47.4 |

41.0 |

47.5 |

55.3 |

59.9 |

56.0 |

3.4% |

| Micro |

48.8 |

39.4 |

42.0 |

45.9 |

49.3 |

51.1 |

0.9% |

| Logic |

11.8 |

9.9 |

11.0 |

12.3 |

13.4 |

13.8 |

3.1% |

| Analog |

17.8 |

14.4 |

15.8 |

17.6 |

18.8 |

19.6 |

1.9% |

| Discrete |

17.3 |

13.9 |

15.3 |

17.0 |

18.2 |

18.6 |

1.5% |

| Opto |

16.7 |

14.9 |

17.0 |

18.6 |

20.0 |

20.8 |

4.5% |

| ASIC |

23.7 |

18.5 |

19.4 |

21.1 |

23.6 |

24.1 |

0.3% |

| ASSP |

68.5 |

57.2 |

62.8 |

70.8 |

76.2 |

78.7 |

2.8% |

| Non-optical Sensors |

3.0 |

2.5 |

2.7 |

3.1 |

3.5 |

3.7 |

4.8% |

| Annual Growth Rates |

|

|

|

|

|

|

|

| Memory |

-20.0% |

-13.5% |

15.9% |

16.5% |

8.4% |

-6.6% |

|

| Micro |

0.1% |

-19.2% |

6.6% |

9.2% |

7.3% |

3.8% |

| Logic |

-7.3% |

-16.6% |

11.4% |

11.7% |

8.8% |

3.0% |

| Analog |

0.0% |

-19.0% |

9.2% |

11.4% |

7.1% |

4.1% |

| Discrete |

-1.6% |

-19.8% |

10.6% |

10.5% |

7.2% |

2.6% |

| Opto |

1.2% |

-10.5% |

13.8% |

9.5% |

7.8% |

3.9% |

| ASIC

|

-4.3% |

-21.9% |

4.5% |

8.9% |

11.8% |

2.2% |

| ASSP |

-1.0% |

-16.5% |

9.8% |

12.8% |

7.6% |

3.3% |

| Non-optical Sensors |

4.0% |

-16.4% |

9.4% |

14.1% |

13.0% |

7.1% |

資料來源:Gartner(08/2009)

儘管記憶體近年售價落差甚大,出貨情況也頗不穩定,但從表2中仍可看出,其在半導體產業中所占的比例仍持續成長,並貢獻一定之營收。而隨著消費性電子產品搭載記憶體的比例日益吃重亦可看出,相關市場的發展更是只增不減,甚至可望帶來一波全新商機。

|

| 圖4 鉅景科技總經理王慶善透露,記憶體向來是印刷電路板上最大面積單元,而SiP之出現可有效堆疊,成為設計人員福音。 |

不過,正因為記憶體角色至為關鍵,從製造商的角度來看,如何為其效能、尺寸、功耗乃至於成本,均能進一步改善,便是各家業者的當務之急。尤其若能搭上各式新問世之立體封裝技術,將有助減輕記憶體設計人員之負擔。

如鉅景科技總經理王慶善(圖4)便認為,由於記憶體一向是占據整體印刷電路板(PCB)最大空間之「禍首」之一,因此設計人員無不期盼將其「除而後快」。不過,在平面設計的世界裡,要談記憶體的尺寸縮減可說是難上加難。但隨著SiP技術的成熟,設計人員可將記憶體與其他晶片進行堆疊,進而縮減封裝尺寸,無疑是設計人員福音。

王慶善進一步解釋,如果從廠商選擇SiP之原因來進行分析可以看出,多數廠商選擇SiP是為了低成本、小型化與薄型化。尤其若能針對記憶體加以精簡,勢必可為設計人員與終端產品帶來更多變化空間。

以近期出貨量最大的消費性電子產品行動電話與數位手機為例,王慶善指出,兩大應用不斷在其中補強諸多功能,不論是各式射頻(RF)技術、照相模組、全球衛星定位系統(GPS)、陀螺儀感測器(Gyro Sensor)、加速度計(Accelerometer)、觸控螢幕、微型投影(Pico Projector)或是儲存裝置,都追求更高程度之整合,因此唯有透過SiP方式將其整合,才能實現消費性電子產品功能多元化之特性。

SiP仍有挑戰須跨越

不過,若說SiP已經爐火純青,卻也並非事實。林崇銘與王慶善均認為,SiP仍有幾項挑戰須要跨越。

林崇銘透露,在執行SiP產品設計時,最常面臨到的一大問題,便是異質整合(Heterogenous Independent)。尤其在射頻元件或類比元件中,要針對不同類型元件的裸片(Die)進行挑選就是一個非常棘手的難題。其中一項原因是相關供應商對提供電性參數模型(SPICE Model)仍有顧忌,因此封裝設計團隊很難預先挑選出功能正常的裸片(KGD)來進行SiP封裝。但對SiP封裝而言,KGD等同於上游原物料,此問題若無法解決,SiP的功效就會大打折扣。

另外,散熱也是亟須解決的問題。眾所周知,愈多的元件堆疊,將愈難進行散熱管理,且在近期相關軟體分析工具發展腳步遲緩的情況下,僅能倚賴手工計算將不符經濟效益。因此林崇銘認為,若想要推動SiP產業往更高層次發展,不論是設計人員的概念、半導體設備、電子設計自動化(EDA)工具與其他周邊均須一併搭配,才有實際效益。

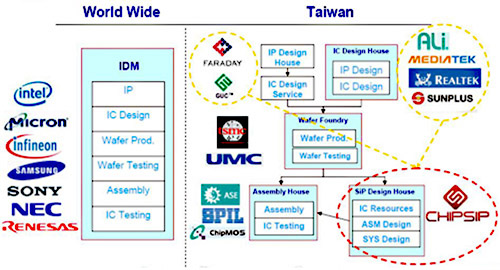

王慶善則認為,談到SiP,就不能忽略業者對「攜手合作」的認知程度。他指出,仔細審視SiP產業鏈便可發現,其上下游關係相當複雜,除了少數幾家整合元件製造商(IDM)大廠外,其餘廠商想要一手囊括所有SiP作業,幾乎是緣木求魚。因此相關業者必須緊密合作,才能各取所需、共創雙贏。

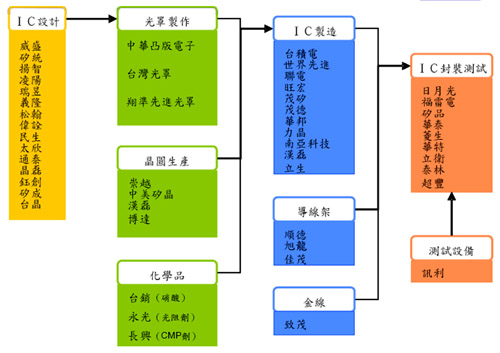

據悉,若欲整合SiP產品,便須依序完成晶片設計、晶圓製造、封裝測試與封裝設計等作業(圖5)。而上述作業無疑是一件相當龐大的工程,再加上部分資訊頗為機密,因此仍有許多晶片設計業者或晶片供應商對SiP充滿疑慮。

|

資料來源:鉅景科技

圖5 SiP作業流程圖 |

因此,王慶善表示,要在SiP市場大展身手,不但須要累積深厚的專業知識,也必須在業界培養一定的人脈與信任,才能讓封裝設計業者設計出最佳的SiP方案。目前該公司已陸續掌握全球各主要記憶體晶片供應商的晶圓參數,且除記憶體外,如邏輯晶圓、封裝廠製程參數等,也都是未來方向。

事實上,除了SiP之外,3D IC之產業鏈連結同樣動見觀瞻。如從圖6便可看出,流程中每一項作業的好壞都可能影響下一個步驟。而在國內業者扮演全球半導體關鍵角色的前提下,如何強化業者間的合作,也將是未來的重要關鍵。如工研院日前主導成立的先進堆疊系統與應用研發聯盟(Ad-STAC)便是希望能強化國內業者的連結關係,同時帶來更多收獲。

|

資料來源:工研院

圖6 3D IC產業鏈 |

MCP沾光記憶體市場

|

| 圖7 科統科技行銷業務處行銷業務部資深經理陳景文表示,透過MCP,各式記憶體將可整合至同一模組上,並視終端應用而彈性調整。 |

在記憶體受到立體封裝技術逐步成熟而日益起飛的同時,另一項封裝技術亦不可忽略。這項名為MCP的技術,其實在記憶體市場醞釀已久,亦已針對部分市場有所斬獲。

科統科技行銷業務處行銷業務部資深經理陳景文(圖7)表示,在記憶體大行其道的今日,幾乎各式電子產品均需一定容量的記憶體。但因應不同裝置的設計差異,如何在其中提供適合的記憶體解決方案,便是業者競爭力之所在。

如科統科技日前開發出小體積之固態硬碟(SSD)MCP後,又接著推出內建DRAM的2.5吋SSD及採用標準SATA介面規格的SSD模組,後者又可為單階儲存單元(SLC)及多階儲存單元(MLC)兩種記憶體。陳景文強調,透過MCP技術,該公司可為客戶開發出高度整合之記憶體,也同樣包括NOR MCP、NAND MCP與Pseudo-SRAM等。

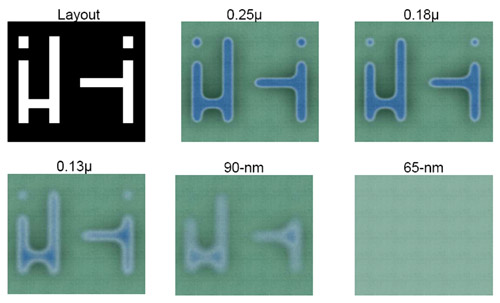

SoC應用環境有限

相對於其他封裝技術,SoC雖亦有一定優勢,但受限於開發時間長、設計困難、不同單元間之交互作用(Cross-talk)甚至矽智財(IP)的疑慮,都是亟須突破的難題。另外,SoC投資成本負擔太高、材料發展不易、微影(Lithography)技術太過困難(圖8),也都是問題。另有研究指出,SoC尚須面臨3D電晶體架構(Transistor Architecture)尚未成熟、製程變異性(Variability)難以掌握以及同樣無解的散熱問題(Thermal Dissipation),因此要將其視為未來最受歡迎的晶片整合方式,恐怕仍有疑慮。不過,儘管SoC技術挑戰所在多有,其適合大量出貨、生命週期長之優勢仍無人能敵。若相關業者能運用SoC找到適合之市場,發展潛力同樣不可限量。

|

資料來源:工研院

圖8 SoC微影技術隨著製程演進而愈加困難。 |

綜觀前文所述可以發現,各式立體堆疊技術均有其優勢,亦各具舞台。但在針對堆疊技術深入研究之同時,投身此產業之業者也必須不時停下腳步仔細思考,各項封裝技術的商機何在,又如何能將其放大,才能找到真正核心之價值所在。