採用OFDMA調變的LTE在實作時容易遭遇驗證挑戰,促使系統開發人員須透過邏輯分析儀及向量訊號分析軟體來進行模擬,以確保LTE編碼與調變正確配置。

長程演進計畫(LTE)正交分頻多重存取(OFDMA)波形的複雜性,對軟體定義無線電(SDR)實體層基頻的發展造成重大挑戰。由於上述波形所需的基頻編碼與解碼相當複雜,因此工程師為軍事通訊等可能的SDR應用設定波形前,須利用改良的設計與全新驗證方法,確認現場可編程閘陣列(FPGA)測試與商用實作的一致性。

本文將探討驗證FPGA實作的改良方法,該改良方法可適用於LTE等複雜的OFDMA波形,將使用模擬的LTE參考向量,確認與商用LTE配置的一致性。商用LTE參考向量模擬區塊亦可為軍事通訊等SDR應用特別設計。此外,邏輯分析儀也將採用向量訊號分析(VSA)量測軟體來探測FPGA設計,以確保在FPGA實作內部的各個測試點可利用VSA軟體進行解調。

LTE標準與配置複雜 加劇FPGA開發難度

事實上,工程師在循環冗餘檢查碼(CRC)編碼區塊上的實作問題,可能導致之後下游的每個編碼階段發生錯誤。工程師要將錯誤追溯回CRC編碼區塊相當困難,除非測試向量能與每個階段的參考向量進行比較。同樣地,FPGA有限脈衝響應濾波器(FIR)tap係數簡單的符號顛倒,也可能造成解調問題,且將反應在SDR射頻發射器輸出端測得的誤差向量幅度(EVM)上。

乍看之下,測試人員可能會認為發射器輸出的解調問題應該是射頻問題。然而,沿著混合訊號/射頻發射器鏈(射頻、中頻、I/Q、數位)探測各個階段的EVM後,可以將問題追溯回FPGA區塊。

FPGA開發人員通常從包含行為要求的系統規範開始著手,上述規範可能會使用一定程度的數學或虛擬碼(Pseudo-code)表示,也可能採用一部分仍在發展或不完整的無線標準。

FPGA開發團隊會解讀上述規範,且可能會自行開發參考模型,產生刺激輸入及預期的輸出。上述數值通常稱為測試向量,可用於硬體敘述語言(HDL)程式碼測試,該程式碼可透過合成及後端對映、配置與繞線工具,產生實際的設計。

目前的LTE OFDMA技術可支援許多配置,但產生測試向量參考模型來支援許多配置也相當耗時且困難。例如,LTE具擴展性,子載波的數量可隨選定的通道頻寬(1.4、3、5、10、15、20MHz)變化。此外,還有各種編碼配置和調變配置,如QPSK、16QAM和64QAM等。

由於LTE標準支援多種配置,產生LTE參考測試向量可能顯著增加FPGA工程師的開發時間。為了從頭開始建立行為測試向量參考,Turbo編碼器/解碼器等複雜區塊可能會耗費大量時間。不幸的是,這些工作會延長手邊主要任務所需的開發時間。

除了增加開發時間外,採用自行編寫/建立行為驗證向量等做法檢查HDL程式碼,FPGA開發人員將曝露在極大的風險中。

這就像作者自行編寫拼字檢查程式的情況,若作者對某個字的拼法不確定,或確信某個字是以特定的方式拼寫,那麼檢查拼字時使用自行編寫的拼字檢查程式驗證是沒有效果的。FPGA開發同樣也是如此。開發人員編寫HDL程式碼時,若曲解了LTE標準的意思,建立行為向量參考時,可能也會重複相同的錯誤。

確保LTE標準解讀一致性 模擬器與測試向量須同時驗證

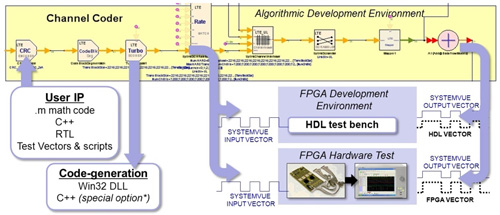

符合LTE標準的獨立測試向量參考已參數化,且能針對許多支援的LTE配置進行設置,可協助處理上述的挑戰。如圖1所示,使用施加到HDL模擬器的相同刺激(Stimulus),讓向量與獨立測試向量參考同時產生,然後將HDL模擬器輸出與獨立測試向量參考進行比較,驗證兩者的行為是否一致。

|

| 圖1 使用SystemVue LTE測試向量參考進行HDL程式碼驗證及FPGA硬體測試 |

若兩者相符,表示無線標準的解讀一致。若兩者不相符,則透過獨立測試向量參考的中間節點執行進一步的除錯工作。LTE參考區塊可針對LTE支援的各種配置進行設置。

此外,模擬的測試向量參考演算法,可以針對需要標準化技術的應用進行特別設計,例如SDR安全軍事無線電。開發人員也可將HDL程式碼帶入設計模擬,在設計模擬環境中與模擬的測試向量參考直接進行比較。如圖2所示,使用HDL協同模擬將向量與模擬模型直接進行比較。

|

| 圖2 在SystemVue使用HDL協同模擬進行除錯工作 |

向量訊號分析軟體立功 FPGA除錯快又準

除了比較基頻編碼/解碼階段的測試向量,在數位I/Q或數位中頻進行VSA調變域分析,可提供額外的FPGA設計驗證。

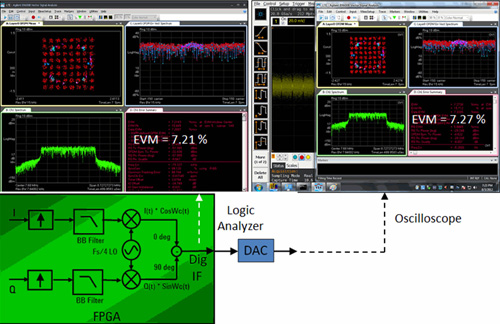

圖3顯示在FPGA開發板上完成的LTE I/Q調變器設計。FPGA板包含一個可將FPGA輸出轉換為類比輸出的數位類比轉換器(DAC)。圖3左側是使用搭載VSA軟體的即時示波器探測DAC輸出端的類比中頻訊號;圖3右側是使用搭載VSA軟體的邏輯分析儀同時探測DAC輸入端的數位中頻訊號。

|

| 圖3 在FPGA開發板上實作的LTE I/Q調變器 |

如圖4所示,仔細檢視以邏輯分析儀探測數位中頻以及以示波器探測DAC輸出的VSA調變域量測結果,發現波形品質下降,EVM性能約為7.2%。亦可從VSA顯示畫面左上方星狀圖中顯示的分散情形,觀察到波形失真的現象。由於來自FPGA輸出的數位中頻(輸入DAC)與DAC輸出顯示相同的EVM結果,表示問題來自FPGA實作的內部,而不是來自DAC的數位類比轉換。

|

| 圖4 邏輯分析儀對FPGA數位中頻的VSA量測結果(左)與示波器對DAC輸出的量測結果(右)。 |

究竟如何找出FPGA I/Q調變器實作內的錯誤來源?問題可能來自FPGA內部的數位升頻器(數位中頻)、數位I和Q路徑,或FIR濾波。但工程師要如何確定錯誤來源呢?為了對FPGA實作進行除錯工作,可利用賽靈思(Xilinx)ChipScope Pro Core Inserter在FPGA內配置測試點。該工具的其中一個選項為插入安捷倫(Agilent)Trace Core 2。利用這樣的量測核心,指定訊號將透過多工器和FPGA內建的FPGA繞線分配至「訊號庫」,然後選定的訊號會傳送至FPGA I/O,最後到達邏輯分析儀的連接點,即可對訊號進行深入追蹤。

如圖5所示,FPGA動態探棒應用程式可用來選擇與過濾後的I和Q資料相關的量測庫。FPGA內的MUX切換可存取上述訊號,邏輯分析儀擷取上述訊號,而VSA軟體負責處理訊號。VSA星狀圖顯示明顯的分散情形,導致EVM為5.1%。

|

| 圖5 探測FPGA實作內過濾後的I和Q輸出 |

工程師進一步檢查個別過濾後的I和Q資料訊號(圖5右側),即可以看到各訊號整體形狀的差異。值得注意的是,以曲線圖(Chart)模式(將數位資料轉換為時域波形)顯示的I資料,出現一些高頻失真的情形,而Q資料則無。再仔細檢查HDL程式碼,發現I上的有限脈衝響應濾波器tap係數符號顛倒。更正有限脈衝響應濾波器tap係數,並重新編譯FPGA設計。

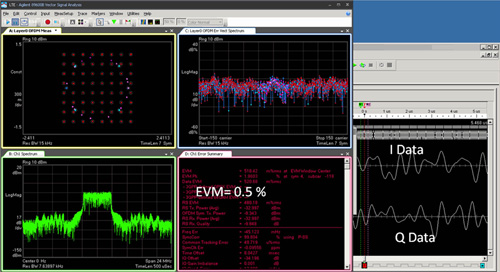

圖6顯示I上的有限脈衝響應濾波器tap係數更正後的新量測結果。產生的星狀圖很明顯較乾淨許多,且現在EVM為0.5%。頻譜不再產生鏡像,且圖6右側的I資料不再顯示先前圖5所觀察到的失真情形。

|

| 圖6 更正有限脈衝響應濾波器tap係數後,探測FPGA實作內過濾後的I和Q輸出。 |

除此之外,VSA軟體亦可以搭配射頻訊號分析儀使用,因此該除錯方法可以擴展到SDR的射頻發射器輸出,使用示波器進行射頻、中頻、類比I/Q的問題除錯,或如本範例中所進行FPGA實作的內部檢測。

本文探討了驗證FPGA實作的改良方法,適用於LTE等複雜的OFDMA波形。模擬的商用LTE參考向量可和來自HDL模擬的基頻編碼/解碼測試向量,或使用邏輯分析儀探測的向量進行比較。如此一來,可協助工程師確認LTE標準支援的各種編碼配置與調變配置(如QPSK、16QAM和64QAM)的一致性。

LTE參考向量模擬區塊可以針對安全軍事通訊等可能的SDR應用特別設計。FPGA設計的調變域分析亦可以用來驗證數位I/Q或者數位中頻階段的性能。

在邏輯分析儀上使用VSA軟體,可對FPGA實作內的各個階段進行探測與除錯,如案例研究中所探討的內容。

此外,在設計模擬軟體、示波器和射頻訊號分析儀中使用相同的VSA軟體,則可讓系統工程師在設計與測試階段,沿著SDR的類比基頻和射頻鏈(類比I/Q、中頻或射頻)進行探測,並快速找出並解決可能的問題,進而加速產品開發設計的時程。

(本文作者皆任職於安捷倫)