大規模多重輸入多重輸出(Massive MIMO)是一個非常有趣的5G無線研究領域。因為其可針對新一代無線資料網路提供多方面的優勢,比如說以更高的資料傳輸率容納更多使用者,加強穩定度之餘,還可降低耗電量。

只要使用大規模MIMO應用架構,研究人員可透過系統設計軟體如LabVIEW和軟體定義無線電(SDR),打造出一百二十八支天線的MIMO測試台,迅速製作大規模的天線系統原型。由於現場可編程閘陣列(FPGA)架構邏輯的設計流程經過簡化,高效能處理的部署過程也很順暢,所以該領域的研究人員可以透過一致的軟硬體設計流程,滿足這類超複雜系統的原型製作需求。

採大量天線 大規模MIMO提升無線資料傳輸率

行動裝置的數量和所消耗的無線資料量持續激增,促使研究人員須投入新技術的研究,才能滿足不斷成長的需求。新一代5G無線資料網路必須搭配目前的通訊系統,克服容量限制、網路穩定性、覆蓋範圍、能源效率和延遲時間等難題。

大規模MIMO為5G的候選技術,在基地台收發站(BTS)採用大量的天線(超過六十四支),能夠大幅提升無線資料傳輸率和連結穩定性。現有標準的BTS架構採用分區拓撲,最多也只有八支天線。

大規模MIMO囊括數百個天線元件,可透過預先編碼技巧把能源集中在目標行動使用者身上,進一步降低輻射。只要把無線能源導向特定的使用者,就能夠降低輻射,同時也可避免干擾其他使用者。

就目前受干擾限制的行動網路而言,這是相當吸引人的一點。如果大規模MIMO確實能提供上述效能,未來的5G網路就會變得更快、可容納更多使用者,提供更出色的穩定性和能源效率。

由於大規模MIMO的天線元件數量很多,也帶來了目前網路所沒有的系統難題。舉例來說,就目前採用LTE或LTE-Advanced的進階資料網路而言,導引訊號負載(Pilot Overhead)必須和天線數量成比例。

大規模MIMO會透過通道互惠在上行和下行鏈路之間使用分時雙工(TDD),藉此管理大量天線的負載。有了通道互惠,即可把上行導引訊號的通道狀態資訊用於下行預先編碼器。實踐大規模MIMO的困難之處還包含了擴充十倍的資料匯流排和介面,或是在大量的獨立射頻(RF)收發器之間達到更多也更分散的同步化效能。

正因為這些時序、處理和資料收集難題,所以原型製作便顯得更重要。如果研究人員要檢驗理論內容,就得從理論研究轉向測試台。只要在實際情境中使用實際波形,研究人員即可開發原型,判斷大規模MIMO的可行性和商用價值。就像所有的全新無線標準或技術一樣,從概念轉移至原型確實會影響實際的部署和商品化程序。

SDR搭配系統設計軟體 MIMO系統架構彈性大躍進

完整的大規模MIMO系統應用架構須包含必備的軟硬體,藉此打造出多功能、可擴充及靈活有彈性的大規模MIMO測試台,以便透過重點頻帶與頻寬提供即時的雙向通訊效能給研究社群。

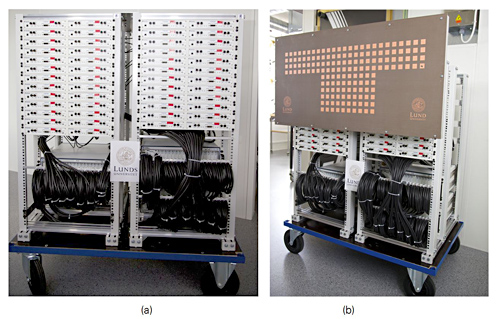

|

| 圖1 瑞典隆德大學的大規模MIMO測試台採用了USRP RIO(a)和客制化的交叉極化平面天線陣列(b)。 |

藉由SDR和系統設計軟體,就可以發揮MIMO系統的模組化特性,把數個節點擴充為一百二十八支天線的大規模MIMO系統。透過靈活有彈性的硬體,即可隨著無線研究需求變化而重新部署至其他設定,比如說做為分散式節點部署於隨建即連(Ad-hoc)網路,也可做為多細胞協調網路。

瑞典隆德大學(Lund University)Ove Edfors和Fredrik Tufvesson教授採用大規模MIMO應用架構,與美商國家儀器(NI)合作開發出全球最大的MIMO系統(圖1)。該系統用了五十個SDR,打造出一百支天線的大規模MIMO BTS設定,如表1所示。

NI和隆德大學的研究團隊根據SDR的概念,使用類似LTE的實體層和TDD開發出系統軟體和實體層,藉此提供行動存取功能。這次合作所開發出來的軟體已成為大規模MIMO應用架構的軟體元件。

就像其他的通訊網路一樣,大規模MIMO系統包含BTS和用戶端設備(UE)或行動使用者。事實上,大規模MIMO主要是為了行動應用而設計的,包含BTS、UE或行動使用者。然而,大規模MIMO和傳統的拓撲很不一樣,主要差別在於配置大量的BTS天線,能夠同時和多個UE通訊。

就NI和隆德大學合作開發的系統而言,BTS的系統設計針對每個UE提供十個基地台天線元件,可供十個使用者以完整頻寬同時存取一百個天線基地台。經過證實,每個UE有十個基地台天線的設計有助於提高理想增益。

大規模MIMO系統內有一組UE會同時把一組正交導引訊號傳輸至BTS。接著就可以使用收到的上行導引訊號來評估通道矩陣,在下行時槽內,這項通道評估會用於計算下行訊號的預先編碼器。

理論上,每個行動使用者即可透過無干擾的通道接收專屬於自己的訊息。預先編碼器設定是一種開放的研究領域,可針對不同的系統設計目標加以設計,舉例來說,預先編碼器可設計為對其他使用者零干擾、盡可能降低輻射功率,也可減少所傳輸射頻訊號的峰均功率比。

透過上述設計,大規模MIMO應用架構可支援高達20MHz的瞬間即時頻寬,並從六十四支天線擴充為一百二十八支,還能夠提供給多個獨立UE使用。表1是在此環境下,部署類似LTE協定的參數狀態,其中採用一個2,048個點的快速傅立葉轉換(FFT)和0.5毫秒的時槽。0.5毫秒的時槽可確保合適的通道和諧狀態,提高行動測試情境(也就是UE移動中)的通道互惠效能。

大規模MIMO系統的四大設計關鍵如下。

理論上,這些關鍵項目可針對不同的研究需求快速完成客製化。本文的應用架構集結了SDR、時脈分配模組、高輸出率PXI系統和LabVIEW,提供穩健又精確的原型製作平台,進一步滿足研究需求。其中,SDR透過一個半寬1U、機架安裝式的機殼,提供整合式2×2 MIMO收發器和高效能FPGA,有助於加速基頻處理作業(圖2)。此外,其可透過PCI Express×4連接至主機控制器和系統控制器,能夠以高達800Mbit/s的資料串流速度傳輸至桌上型或PXI Express主機電腦,或透過ExpressCard以200Mbit/s的速度傳輸至筆記型電腦。

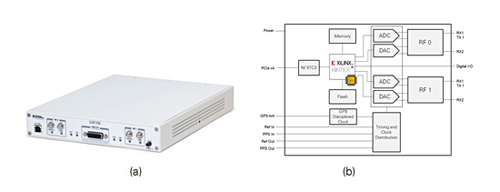

|

| 圖2 USRP RIO硬體(a)和系統方塊圖(b) |

上述的SDR硬體名為USRP RIO,搭載LabVIEW可重設I/O(RIO)架構,其中結合開放式的系統設計軟體和高效能硬體,有助於大幅簡化開發作業。緊密的軟硬體整合能夠降低系統整合的難度,對於如此大規模的系統更是如此,可以讓研究人員致力於研究項目。

PXI Express機箱背板

大規模MIMO應用架構採用PXIe-1085這款進階的18槽式PXI機箱,其中每個插槽皆搭載PCI Express Generation 2技術,可達到高輸出、低延遲的應用效能。此機箱可提供4Gbit/s的單插槽頻寬、12Gbit/s的系統頻寬。

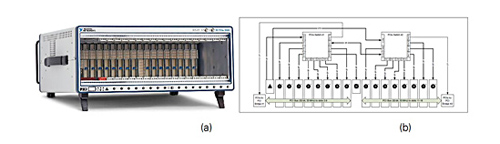

|

| 圖3 18槽式PXIe-1085機箱(a)和系統方塊圖(b) |

圖3為雙切換器背板架構。如要建置高通道數系統,可透過菊鏈方式把多個PXI機箱串聯在一起,也可放入星形設定。

高效能可重設FPGA處理模組

大規模MIMO應用架構採用FPGA模組如FlexRIO,在PXI機箱中加入靈活高效能的處理模組,透過LabVIEW FPGA Module即可設計程式。該FPGA模組可獨立使用,提供客製化的大型Xilinx Kintex-7 410T和PCI Express Generation 2×8連線功能給PXI Express背板。

八通道時脈同步化

另外,OctoClock時脈分配模組具有八個通道,可以八種方式透過長度匹配軌跡放大並分割一個外部10MHz參考和每秒脈波數(PPS)訊號,進一步提供頻率和時間同步化效能給最多八個USRP裝置。

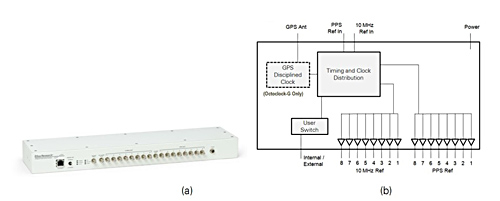

|

| 圖4 OctoClock-G模組(a)和系統方塊圖(b) |

OctoClock-G使用全球衛星定位系統(GPS)授時的振盪器(GPSDO),額外加入一個內部的時間與頻率參考,圖4為OctoClock-G系統簡圖。正面板的切換器可讓使用者選擇內部GPSDO和外部參考。

LabVIEW系統設計環境

LabVIEW具備整合式工具流,有助於管理系統層級的軟硬體細節;透過GUI顯示系統資訊;開發通用處理器(GPP)、Real-Time和FPGA程式碼;並且把程式碼部署至研究測試台。有了LabVIEW,使用者即可整合額外的程式設計語言,包含ANSI C/C++(透過呼叫庫節點)、VHDL(透過IP整合節點),甚至是.m檔案指令(透過LabVIEW MathScript RT Module)。這樣一來即可開發出高效能實作項目,兼顧出色的穩定性和客製化功能。大規模MIMO應用架構運用了LabVIEW的高生產力特性,以及可透過LabVIEW FPGA設計並控制I/O細節的功能。

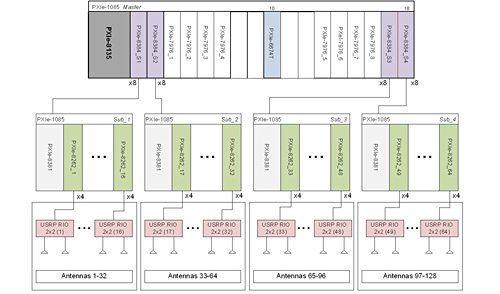

PXI機箱滿足大資料輸出需求

上述的軟硬體平台元素組合成一個測試台,可把數支天線擴充為超過一百二十八支同步化天線,該天線系統囊括了六十四個雙通道SDR裝置,連接至四個設為星形架構的PXI機箱。主機箱可彙整所有資料,以便透過FPGA處理器和搭載四核心英特爾(Intel)i7的PXI控制器集中處理這些資料。

|

| 圖5 PXIe-7976R FlexRIO模組(a)和系統方塊圖(b) |

如圖5所示,主機箱把PXIe-1085機箱做為主要的資料彙整節點和即時訊號處理引擎。PXI機箱提供了十七個開放式插槽可用於輸入/輸出裝置,此外還有時序與同步化、可即時處理訊號的FlexRIO FPGA機板、可連接至子機箱的擴充模組。

|

| 圖6 可擴充的大規模MIMO系統方塊圖結合PXI和USRP RIO。 |

一百二十八支天線的大規模MIMO BTS需要出色的資料輸出效能,才能夠彙整並處理I/Q樣本,進而透過一百二十八個通道即時完成收發作業;市面上的PXIe機箱如PXIe-1085則可確實滿足此需求,支援的PCI Generation 2×8資料路徑能夠達到最高3.2GB/s的輸出率(圖6)。

在主機箱的Slot 1內,PXIe-8135 RT控制器或嵌入式電腦可做為中央系統控制器。PXIe-8135 RT配備2.3GHz的四核心Intel Core i7處理器(單核心Turbo Boost模式可達3.3GHz)。

主機箱裝載了四個PXIe-8384(S1到S4)介面模組,可以把子機箱連接至主系統。機箱之間的通訊除了透過MXI之外,還仰賴了PCI Express Generation 2×8,可以在主機箱和其他子節點之間提供高達3.2GB/s的效能。

此系統還配備最多八個FPGA模組,可滿足大規模MIMO系統的即時訊號處理需求;插槽位置提供一個範例設定,其中的FPGA可以串聯起來,支援每個子節點的資料處理需求。每個FPGA模組都可以彼此透過背板接收或傳輸資料,甚至可以連接所有的SDR,延遲時間不到5微秒、輸出率高達3GB/s。

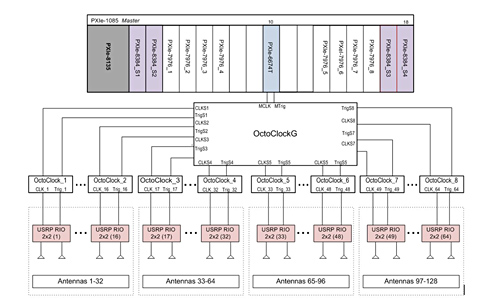

時序和同步化至關重要

如果系統要部署大量的無線電,時序和同步化都很重要,這都是大規模MIMO系統的關鍵。BTS系統共用一個10MHz參考時脈和一個數位觸發器,可啟動每個無線電的擷取或產生功能,確保整個系統的同步化效能(圖7)。

|

| 圖7 大規模MIMO 時脈分配方塊圖 |

PXIe-6674T時序和同步化模組配備OCXO,位於主機箱的Slot 10,可產生穩定又準確的10MHz參考時脈(50ppb準確度),並提供數位觸發器讓裝置與主要OctoClock-G時脈分配模組達成同步化。

接著OctoClock-G就會供應並緩衝10MHz參考(MCLK)和觸發器(MTrig)給OctoClock模組,從第一個到第八個依序完成,然後供應至SDR裝置,藉此確保每條天線都可以共用10MHz參考時脈和主機觸發器。此外,上述的控制架構可針對每個無線電/天線元件提供精確的控制功能。

基地台應用架構軟體是專門為了滿足表1所述的系統目標而設計的,OFDM實體層處理功能會分配至SDR裝置的FPGA內,MIMO實體層處理元件則會分配至PXI主機箱的FPGA。

更高階的MAC函式會在PXI控制器上、Intel為架構的通用處理器(GPP)上執行。此系統架構有助於處理大量資料,同時降低延遲以維持通道互惠效能預先編碼參數會直接從接收器傳送至傳輸器,藉此優化系統效能。

從天線開始,OFDM實體層處理會在FPGA上執行,這樣一來,需要最大量運算資源的處理作業就會在天線附近執行。這樣的運算結果就會在MIMO接收器IP結合起來,替每個使用者和每個子載波解析通道資訊。

算出來的通道參數會傳輸至MIMO TX區塊,預先編碼會在此套用,把能源集中在單一使用者的退回路徑。雖然MAC有些部分會實作於FPGA,大部分和其他較上層的處理都會實作於GPP。系統每個階段所使用的特定演算法也是相當活躍的研究領域。

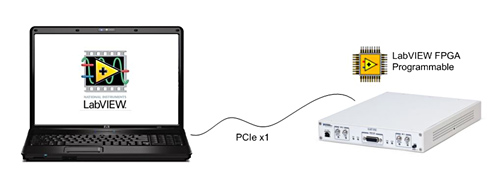

UE就是具有單一輸入單一輸出(SISO)或2×2 MIMO無線功能的手機,或其他無線裝置。UE原型可採用市面上的SDR,配備整合式GPSDO,使用接線PCI Express把筆記型電腦連接至ExpressCard(圖8)。

|

| 圖8 標準的UE設定,搭配筆記型電腦和USRP RIO |

事實上,GPSDO非常重要,因為它提供更出色的頻率準確度,還可提供同步化和地理位置功能,滿足未來的系統擴充需求。典型的測試台實作可能包含多個UE系統,其中每個SDR可能代表一或兩個UE裝置。

UE上的軟體實作方式就像BTS一樣,然而此軟體會做為單一天線系統而實作,把實體層放在SDR的FPGA,把MAC層放在主機PC。

PXI平台推進5G研究時程

透過LabVIEW系統設計軟體搭配USRP RIO和PXI平台,徹底改革了高階研究系統的原型製作方式。本文說明一個建置大規模MIMO系統的實用選項,有助於促進未來的5G研究。

把如此獨一無二的NI技術組合用於應用架構,即可針對大量的無線電同步化時間和頻率,PCI Express基礎架構也可滿足輸出需求,藉此以超過15.7GB/s的速度,在上行和下行傳輸並彙整I/Q樣本。FPGA的設計流程可簡化實體層和MAC層的高效能處理作業,滿足即時的時序需求。

(本文作者為美商國家儀器RF和SDR資深產品行銷經理)