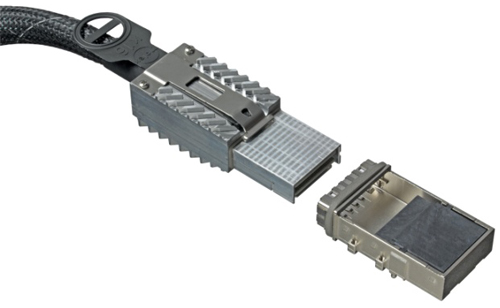

含有CDFP 1型銅纜的互連系統,能提供更高資料傳輸速度,讓電信與網路應用中的核心交換機、資料中心和路由器實現更高速度的互連效果。

如同NASCAR的賽車手一樣,當今的電子設備設計人員也在不斷追求更高速度。資源密集型的應用需要更高的資料傳輸速度,而連接器供應商則在開發可以滿足這類資料速率要求的各種系統。

舉例來說,2014年9月發布的CDFP 2.0可交互運作熱插拔互連模組之規範,可在十六條通道上實現25Gbit/s的資料速率,因此整體資料傳輸速度可達到400Gbit/s。

採PAM4編碼流程 新互連系統傳輸率超越400Gbit/s

400Gbit/s標準已是一項重大成就,但市場上最近卻出現了超出此一速度的開發成果,該解決方案整合安華高(Avago)的積體電路(IC)、Molex的CDFP連接器,以及一條1公尺長的被動電纜,設計目標是讓每條通道達到25Gbit/s,但Molex在運行時讓每通道達到32Gbit/s,因此整體輸送量達到512Gbit/s。

Avago是一家位於加州聖荷西的半導體製造商,其積體電路具有更豐富的訊號完整性管理能力,因此成為該解決方案的重要組成部分。據了解,該款積體電路與Avago其他積體電路之方法論,不但能夠提高資料速度,同時還可管理誤碼率。

透過極高速的串列互連系統來提高不歸零(NRZ)的資料速率,是一種提高資料速度的簡單方法,然而這種方法需要不同的連接器;另一種增進到25Gbit/s連接的方式,則是更新積體電路並使用4階脈衝振幅調變(PAM4)對資料進行編碼,使資料流中包含更多資訊。在理論上,使用PAM4可達到800Gbit/s的整體資料傳輸速率。

與傳統的二進位NRZ方法相比,雖然PAM4是比較複雜的流程,但能夠為資料速度帶來重大改進。在NRZ訊號傳導中,資料是以PAM2來傳輸,其中每個脈衝只有兩個數據編碼級:0或1。在PAM4中,每個脈衝則有四個編碼級:0、1、2或3,而在一整個位元組中將有兩個脈衝會被編碼,這意味著被傳輸的資料將會有8位元。

這樣一來,透過此一通道便可以發送更多資訊,毋須具有更高頻寬能力的新元件。當然,使用PAM4實現更高資料速度的缺點,是在傳輸前必須對資料編碼,然後再收到後解編碼(De-encode),因為這需要額外的處理能力。

然而,這功能可實現新技術,使電子產業可突破當前在連接器密度/速度方面的限制,相當值得對此進行投資及處理其所需的系統複雜性。超高速、高密度的連接器解決方案將有助對下一代介面中可實現的功能產生新的見解,這些新型連接器將使用更小尺寸組件,其困難之處在於如何將這些解決方案應用在新設備的設計中。

要達到更高的速度,也需要更加堅固耐用的線纜組件。例如在Molex的測試中,zQSFP+連接器和3公尺長的高速線纜組件在50Gbit/s的NRZ下運行。高速線纜有助於降低在特定頻率下發生插入損耗(能量耗散)的吸出(Suck-out)情況,且資料速度越高,這種情況就越容易發生。

設計人員須充分了解所有的新型元件,以及知道如何有效地利用它們,其中包括開發新的規範,為運行速度更高的互連系統提供可靠的指導原則。

打造高速連接器 掌握通道性能成關鍵門票

此外,業界必須對通道的整體性能具有更加精準的了解,而非只是各個獨立的元件。舉例來說,目前新款的連接器雖然已經被眾多的25Gbit/s規範所採用,但還未達到其應有的普及程度,因為業界對實施高速連接器的經驗法則相對較為保守,這意味著實現高出標準所允許的更高資料速率是可能的。

為了使用這類連接器達到極高的資料速度,在鏈路中的元件上使用額外緩衝區是不切實際的,且測試結果已證明設計良好的系統不一定需要這類額外緩衝區。

通道運行邊際(Channel Operating Margin, COM)分析是一個強大工具,讓設計人員能了解元件性能,以及這些元件是否能支援更高資料速率;並檢測實際而非理論的運行邊際,從而了解通道的運行表現。

COM分析可讓系統設計人員模擬連接器和線纜性能上的改變,進而實驗不同的元件組合,以確定真正的速度瓶頸所在。

為了實現這種速度,設計人員必須更深入了解主要系統元件的性能,並且確切地了解其對通道性能的影響。如此一來,才能夠超越當今過於保守的標準限制,進入高速資料傳輸的未來。

(本文作者任職於Molex)

|

| 開發人員正戮力打造具有更高資料傳輸率的高速傳輸系統,滿足市面上資源密集型的應用。 |