JESD204B為業界標準序列通訊連結,資料轉換器與現場可編程閘陣列(FPGA)、數位訊號處理器(DSP)、特定應用積體電路(ASIC)等裝置間的數位資料介面因此能化繁為簡,這項標準減少裝置間路由進而降低輸入/輸出及電路板面積需求,符合無線通訊、量測、國防、航太等應用所需。

一般選擇高速類比數位轉換器(ADC)時,ADC延遲高低大多並非重要設計因素或規格,最近新的JESD204B高速序列介面正迅速在全球普及,也逐漸成為數位介面首選,不過也因此為ADC延遲增加多個時脈週期,故有些系統設計師仍繼續沿用既有的低延遲介面,本文分析造成高速管線式ADC延遲的主因,並說明部分系統仍避免選用JESD204B的理由。

系統設計人員標示元件延遲時,通常以奈秒為單位,但管線式ADC延遲計算單位為時脈週期,意指從ADC採樣時脈捕捉到輸入訊號,至產生數位輸出的時間差,採樣率增加後,固定時脈週期的絕對延遲奈秒數減少。

傳輸延遲(TPD)代表時脈輸入、時脈輸出與資料的緩衝延遲,一般未納入延遲數據中,取決於緩衝使用量,以及個別緩衝擊在不同製程、電壓及溫度下的延遲變化,故傳輸延遲屬於變數,可能低於一個時脈週期,也可能達到數個時脈週期。

管線式ADC的產品說明書內,亦標明未納入延遲數據的孔隙延遲,意指從輸入採樣時脈的上升邊緣抵達ADC,到採樣實際發生之間的時間差。

分析管線式ADC延遲

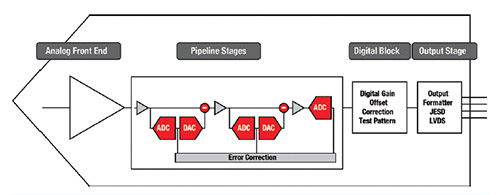

現代高速管線式ADC的延遲與設計大有關係,ADC可拆解為四項基本區塊:類比前端、管線級、數位區塊、輸出級(圖1),由於ADC設計師可決定各區塊配置情形,基於ADC採樣率、耗能、AC效能等考量因素,每一項設計都各有不同。

|

| 圖1 現代高速管線式ADC的基本區塊 |

類比前端內含採樣保持放大器,有時再加上類比輸入緩衝,協助抑制切換電容採樣電路的突波雜訊,這個區塊通常只需要半個到一個時脈週期。

管線區內含個別管線級,以及組成輸出資料的錯誤更正功能,每一管線級內含低解析度ADC、數位類比轉換器(DAC)及殘值放大器,由於各級間輪流使用時脈上升邊緣與下降邊緣,通常只需半個時脈週期,各級解析度也不需相同,解析度愈高,管線式整體延遲愈低,但也需要更多比較器、更高耗能、匹配更緊密、偏移更少,故設計愈複雜。依據各級數量多寡,管線式區塊延遲介於二到五個時脈週期,在不同使用情況下,錯誤更正功能可能外加一至二個時脈週期。

數位區塊延遲依架構內功能數量而定,多數管線式ADC介於三到十個時脈週期,終端用戶通常樂於擁有多功能,如數位增益管控、DC偏移更正、資料格式化(2s互補/偏移二進位或MSB/LSB First)等;然而內建多項功能卻也會增加ADC延遲的時脈週期,通常只要省略這些功能,延遲即可縮小,但即使是多工器也會增加延遲。

ADC採樣率也會衝擊延遲情況,隨著採樣率增加,基於製程限制,或為減少耗能,數位區塊可能得降低運作速度,如數位區塊運作速度減半,即可同時處理兩項樣本,故實質ADC速度不變,但並行與序列運作仍會消耗額外的時脈週期。

輸出級內含資料格式器與數位介面,在傳統低電壓差動訊號(LVDS)介面中,這個區塊只是移位暫存器,將數位資料置入LVDS輸出緩衝內,依據單倍、雙倍或四倍之別,只需一至二個時脈週期;而最新JESD204B介面在此區塊稍微複雜一些,加入8b/10b編碼、資料攪拌器、序列器。ADC採樣率與序列器資料傳輸速率提高後,可能需要更多內部並行處理,因此衝擊延遲,而在不同的設計、ADC採樣率與配置之下,JESD204B介面延遲可能介於四至二、三十個時脈週期。

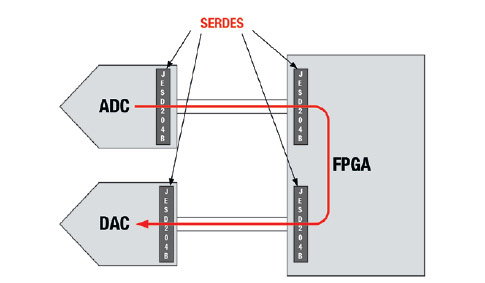

儘管多數系統設計人員樂於採用JESD204B介面,實現確定性延遲或印刷電路板路簡化,但有些應用卻無法應付額外延遲,如控制線路、電子反制,可接受的系統往返延遲極低。JESD204B介面可能增加諸多延遲,實際使用時更可能增加四倍。在接收路徑上,資料得先解序列,才能夠處理,傳輸側亦同,資料得先在處理器/FPGA排序後至DAC內再次解序列(圖2)。

|

| 圖2 系統內含JESD204B介面的接收與傳輸路徑範例。 |

考量到JESD204B未必適合所有應用,半導廠遂推出不同版本的高速資料轉換器,一者使用最新JESD204B介面,另一者維持傳統LVDS介面,方便系統設計師自由選擇,可運用JESD204B介面簡化電路板設計,亦可以LVDS介面縮短延遲。

(本文作者任職於德州儀器)