隨著網路技術與物聯網應用的發展,資料傳輸流量的需求也不斷的增長。在數據傳輸技術中,下一個重大轉變將是400Gb乙太網路(400GbE)技術的推展與普及,400Gb乙太網路技術預計將很快的會在各種雲端服務、電信公司、以及需要超高頻寬連接的應用環境中進行試用。數據傳輸技術朝向400Gbps速率發展的方向應該是主流的趨勢,但是400Gbps傳輸介面模組要採用何種型式的插拔外型,目前產業界仍有不少的討論,成本的考量會是技術轉型的思考重點。因此,400Gbps傳輸介面模組技術預計需要考量向下的相容性與向上的發展性,以降低發展過程的成本需求。

四路小型可插拔(Quad Small Form-factor Pluggable, QSFP)收發器是目前廣泛使用在光纖數據傳輸的一種緊湊型熱插拔收發器,在收發器介面具有四個發射與四個接收通道,可將網路通訊設備(如:伺服器和交換機)連接到光纖纜線。QSFP的外型和電氣介面由多源協定(Multi-Source Agreement, MSA)規定,是由許多網路組件供應商聯合開發和支持的產業格式,隨著網路傳輸流量增加的需求,QSFP模組操作速率也不斷的發展與演進,QSFP的操作速率為4×1Gbps;QSFP+的操作速率為4×10Gbps;QSFP28的操作速率為4×28Gbps,可使用於100Gbps網路的鏈結。

由於超大規模數據中心不斷增長的頻寬需求,使得光通訊的收發器模組急需能提高傳輸速率至200Gbps或400Gbps的解決方案,以降低頻寬成本。因此,MSA已提出QSFP-DD(Double Density)的模組標準,在標準的QSFP四通道接口,多增加一排四通道接口,成為具有八通道的光收發器,若採用非歸零(Non-return Zero, NRZ)資料格式,傳輸速率可達200Gbps;若採用四接脈波振幅調變(Four-level Pulse Amplitude Modulation, PAM-4)資料格式,每個通道傳輸速率可達50Gbps(或25Gbuad),可實現400Gbps的傳輸。QSFP-DD模組的結構可以支援QSFP+和QSFP28標準,讓使用QSFP-DD模組所設計的系統可以向下兼容,能與目前已在使用的40GbE和100GbE收發器共同操作,提供用戶和系統設計更靈活的系統規畫。思科也在OFC 2017中展示QSFP-DD模組,預期QSFP-DD將成為下一代400GbE可插拔光模組的主要標準之一。

著重模組整體結構設計 高速光收發器模組開發有訣竅

對於高速光收發器模組的開發,除了關鍵的高速光電元件、相關的驅動IC外,模組整體結構的設計與製作也是重要的一環,光收發器模組開發製作的流程依序為整體電路設計、印刷電路板疊構設計、印刷電路布局設計、印刷電路製作、電路元件焊接與電源測試、光電元件焊接與耦光測試、整體光收發器模組測試等步驟。

根據光收發模組的相關規範,選擇適當的元件、光源驅動IC、光接收IC、微控制器(MCU)、電源IC等建立物料清單,並依照模組的輸入、輸出端口及功能設計整體電路圖。

主要針對高頻訊號層,選擇適合的電路板材料,再根據相關規範設計電路板堆疊層數與結構,並計算高頻訊號走線寬度,以符合傳輸路徑之阻抗匹配。

根據電路板疊構與整體電路圖,設計高頻訊號走線、低速控制訊號與電源走線、接地面等電路板各層布局。

與電路板工廠製程工程師討論確認電路板設計與製程工法可以實現,則可依照電路板布局及疊構設計製作模組的電路板。

將電路板先焊接上電阻、電容等被動元件,以及電源相關IC,先進行電路板電源供應測試。

在電路板上焊接雷射二極體晶片、光二極體晶片、光源驅動IC、光接收IC、微控制器(MCU)等元件,將韌體寫入MCU控制相關IC,進一步調控光發射器與光接收器操作條件,接上透鏡與測試光纖,並微調透鏡位置以獲得最佳耦光效果。

將完成的光收發模組,透過其評估板,設定在多種操作條件下,進行發射與接收訊號眼圖品質、傳輸資料誤碼率等測試,確認訊號傳輸品質符合相關標準與規範。

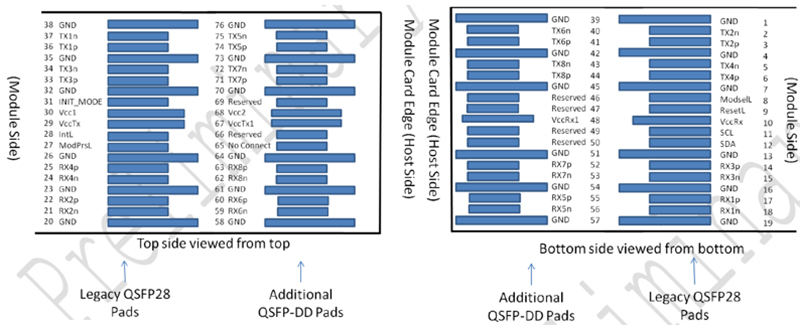

對於QSFP-DD光收發模組的開發,若採用NRZ資料格式操作,單一通道的傳輸速率為25Gbps,與適用於100GbE的QSPF-28模組速率相同,但是QSFP-DD的光發射與接收通道數由四增加至八通道,而電路板面積仍然相同,所以QSFP-DD的通道密度加倍。因此,QSFP-DD模組輸入輸出端口的金手指規範與其他QSFP模組不同,共有76個端口,而且排列成兩排,如圖1,除了八對高速訊號輸入端口將資料送入光發射器,八對高速訊號輸出端口將光接收器資料送出,以及各對高速訊號輸入輸出端口兩側的接地之外,還有五個電源供應端口,及八個功能控制使用的端口。

圖1 QSFP-DD模組輸入輸出端口金手指結構

圖1 QSFP-DD模組輸入輸出端口金手指結構

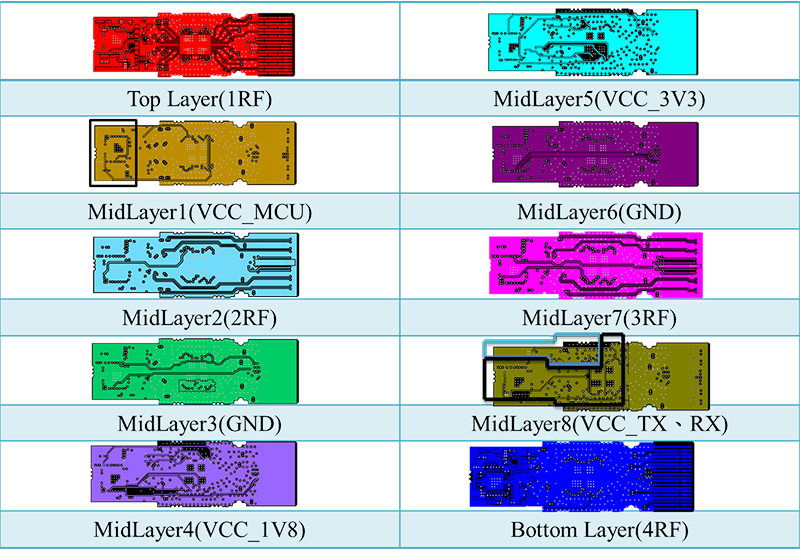

目前適用100GbE的QSPF-28模組,其電路板通常採用六層的疊構,最上與最下層為高速訊號走線層,依序往內有兩層接地層,及兩層低速控制訊號與電源供應層。但是QSFP-DD模組的通道數倍增,以原有QSFP模組的電路板面積,兩層高速訊號走線層將無法實現八通道光發射與八通道光接收的模組,因此QSFP-DD模組的電路板設計需要使用到十層電路板設計,讓高速訊號走線層增加為四層。因為QSFP-DD電路板的疊構增加為十層板,但是電路板總厚度仍需與QSFP模組相同,所以高速訊號走線層與接地層之間的厚度將會減小,如此將會使高速訊號走線的電容變大,降低傳輸頻寬。

因此,QSFP-DD高速訊號層的電路板材料必須採用更低介電係數的材料,來降低傳輸線電容,以符合所需的傳輸頻寬。高速訊號層電路板材料的選擇也是QSFP-DD模組電路板設計的關鍵之一,電路板高頻訊號線傳輸頻寬的設計必須與板材的介電係數、損耗係數、最小可製作厚度等條件之間進行設計取捨。

此外,由於使用四層高速訊號層,除了電路板最上與最下層外,高速訊號將會在電路板內層傳輸,勢必會出現高速訊號由外層進入內層或由內層送出外層的傳輸,此處的訊號完整度常因為走線的不連續或鑽孔連接而被破壞,無法達成良好的阻抗匹配,因此內、外層之間訊號的傳輸必須特別注意訊號完整度的模擬分析與設計。QSFP-DD模組十層電路板的設計範例,如圖2。

圖2 QSFP-DD模組十層電路板設計範例

圖2 QSFP-DD模組十層電路板設計範例

高速數據傳輸技術朝400Gbps發展的方向應是無庸置疑,而QSFP-DD光收發模組開發的目的就是要滿足400Gb乙太網路的市場需求與系統優化而產生,QSFP的模組的外型尺寸已經被設計使用超過十年,因此具有良好向下兼融的QSFP-DD模組在400Gbps發展初期,是一種低成本的解決方案。而未來高速數據傳輸光模組的發展,還需要考量操作速率是否具有向上的發展性、系統對模組的散熱機制、以及光學組件與模組間的配合度等問題。400Gb乙太網路整體的建構目前仍屬於實驗室建構與測試階段,公共部署與示範即將展開,在市場爆發前期,建立新一代高速數據傳輸光模組技術是刻不容緩的工作。