就如同許多半導體元件一樣,高速的類比數位轉換器(ADC)不會總是運作得很完美,儘管許多業界人士會這麼期待著。由於先天上的限制,使其偶爾發生超出正常功能之外的轉換誤差,但許多真實世界中的取樣系統(如測試與量測設備等)無法容許高速率ADC的轉換誤差。因此,有能力將高速類比轉數位轉換誤差率(CER)的頻率與強度量化是相當重要的,如此工程師才能夠以適當的性能期望值設計系統。

相對不常發生的高速與GSPS(Giga Sample Per Second,每秒10億次取樣)ADC的轉換誤差,不僅在偵測上極具挑戰性,同時也讓量測過程相當的費時。這個期間通常無法在數微秒(μs)或數毫秒(ms)內完成,而需要數小時、數日、數週、甚至數月的時間。為了減輕這種冗長測試的負擔,設計人員可以藉由確定性的信賴水準(CL)來逼近此誤差率,同時維持結果的品質。

區分BER與CER

CER就是轉換誤差數量除以取樣總數的比率,類似於其數位等效--位元誤差率(BER)在串列或並列數位資料傳輸中的特性。然而,在BER與CER之間有一些很明顯的差異。在數位資料串流中的BER測試會執行一個很長的虛擬隨機序列,可以在發射器內於傳輸的兩端使用一組共通的種子值來加以啟始。然後,接收器就會預期具有理想的傳輸。BER是透過對接收資料相較於理想狀態之差異的觀察而精密計算出來的。在介於兩端之虛擬隨機序列資料中的不匹配(以種子值為基準)就會被計算為位元誤差。

以CER來相互對照,其誤差的判定就不會像純粹的數位比較那麼直截了當。由於微小的非線性度總是會出現在ADC轉換程序當中(再加上系統雜訊與抖動),因此介於期望和實際資料之間的精確差異是無法一直都能加以判定的。取而代之的是,必須要建立一個誤差臨界值,用以判定轉換誤差以及具有可容忍,但為預期中雜訊的取樣之間的分界線。與數位BER相對照之下,被傳輸與接收的預期資料間並沒有一個精確的比較。但取而代之的是一個取樣的誤差強度,必須在將其考量為轉換誤差,或是轉換器與系統的預期非理想訊號之前,先加以量化。

ADC的後端數位介面須要具有比轉換器的核心CER更低的誤差率,因此不可忽視。若非如此,那麼資料輸出傳輸誤差就會淹沒CER,並且貢獻更大的誤差值。系統設計人員對於誤差是從ADC的哪個部分出現並不在意。然而,為了本文所討論的目的,這裡將會只專注在ADC轉換誤差率。

留意動態穩定性

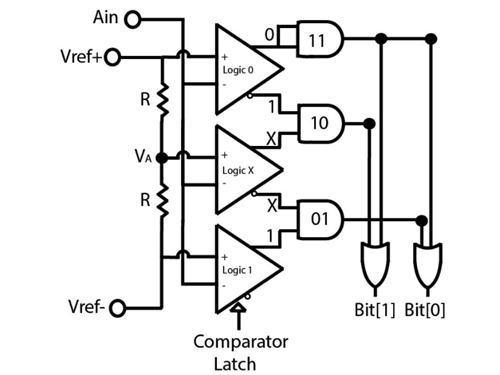

在高速ADC中轉換誤差的其中一項典型原因就是被稱為動態穩定性(Metastability)的現象。高速ADC通常會在從類比訊號到數位數值之轉換處理的不同級當中使用許多的階梯式比較器(圖1)。當比較器不能夠判定類比輸入是高於或是低於其參考點時,那就可能會產生出導致誤差編碼的動態穩定結果。當兩組比較器的輸入在強度上的差異非常小或者為零的時候,這種情況就可能會發生。隨著這個不正確的數值向下傳播到管線中,明顯的轉換誤差就可能會以ADC的輸出而呈現。

|

| 圖1 這個基礎的階梯式比較器設計顯示出在比較器判定點(動態穩定性)的轉換失敗的可能點。假設狀況是Ain = VA。中間比較器可能無法分辨在有限轉換時間內的穩定輸出,因此Bit[1]與Bit[0]可能會有許多可能的誤差組合。 |

當差動類比輸入是相對龐大的正或負時,比較器就能夠快速地解析差異並且做出清楚的判定。當差值非常的小或為零時,比較器判定的持續時間就會增長許多。假如比較器輸出在這個判定點之前就被鎖定的話,那麼動態穩定的結果就會因此產生。

幸好,有一些設計的補救方法能夠減輕這些問題的影響。第一種,同時也是最為明顯的方法就是設計比較器讓中間區域非常地小,如此一來比較器就會被迫針對類比輸入狀況的最大可能範圍做出精確的判定。這可能會需要很多的電路功率與設計空間。

第二種方法就是延遲比較器的取樣時間,直到可能的最後一刻,這會提供類比輸入最大量的時間穩定至已知的比較器輸出值。然而,這種方法是有其限制的,因為延遲最長只能夠達到目前取樣的時間到達以前,而且比較器必須轉而解析下一個取樣。

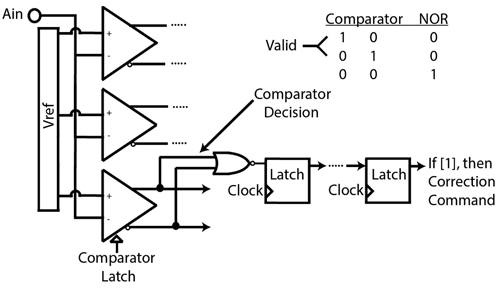

第三種方法則是使用智慧型誤差偵測與校正演算法則,能夠針對位於高速ADC轉換程序後級中的比較器所出現的無法判定情況,以數位方式加以補償。在最大允許時間期間內比較器沒有做出判定時,其不足之處就會以邏輯方式加以偵測。接著,此項資訊就會被附加到有問題的取樣當中,以做為未來的內部調整之用。當這個警示被加以辨認後,就可以利用後處理步驟,在取樣從轉換器輸出前針對誤差進行修正,這可以在圖2當中看到,使用亞德諾(ADI)新近發表的12b、2.0 GSPS ADC的AD 9625。

|

| 圖2 比較器的無法判定狀況能夠在亞德諾AD 9625的類比數位轉換程序中被加以辨認。在它從轉換器輸出之前,可以在後續的步驟當中執行修正指令,以誤差來修正取樣。 |

認識信賴水準

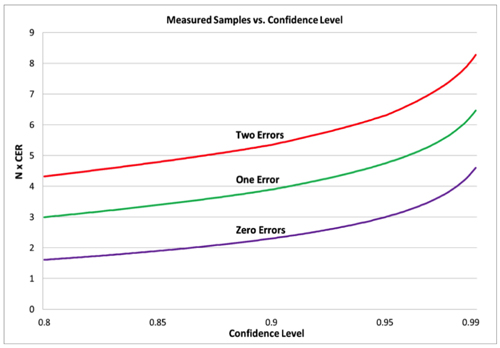

CER信賴水準是一項對未來誤差的外推期望值,儘管沒有量測到一定的失敗率。這使得針對特定CER所進行取樣的總數量下降,但會獲得低於100%的確定性。要達到絕對100%的確定性,在數學上需要無限期間的取樣。因此,業界的基本規則是95%的信賴水準,也就是與一已知數值相對的足夠接近,介於些許不確定性與實際量測時間之間。

有時候,會誤以為一旦誤差在測試期間被偵測到時,程序就此結束,而最終的轉換誤差率就已經得出了,如此將既不精確也不完整。具有相關聯信賴水準的轉換誤差率,能夠在處理過程中以有誤差與沒有誤差的方式進行測試。然而,假如誤差是針對特定信賴水準進行偵測的話,那麼相較於沒有誤差的取樣數量而言,量測取樣的量就必須要增加,這種衝擊可以在圖3當中看到。

|

| 圖3 N x CER vs.信賴水準與誤差偵測數量的圖表。注意到CER測試能夠在一個測得誤差發生之後持續進行,但是只需要增加一定數量的量測取樣,以便達到相同的信賴水準。 |

對於信賴水準的自然對數關係、誤差率以及取樣數量,能夠藉由公式1以數學方法予以呈現:

......................................................公式1

N=量測取樣數量

CER=轉換誤差率

CL=信賴水準

E=偵測到的誤差數量

當未偵測到誤差時,該方程式會變得更為簡單,因為右邊的項目會等於零,而結果只能夠依據左邊項目來決定。對於沒有量測誤差的95%信賴水準而言,必須採取只有大約三倍的取樣數量做為逆預期CER。量測到100%信賴水準時,對於任何CER值的CL=1.0,以數學方法取得無限量的取樣(N)as-ln(0)→無窮大。

N×CER=-ln(1-0.95)=-ln(0.05)= 2.996

觀察誤差臨界值

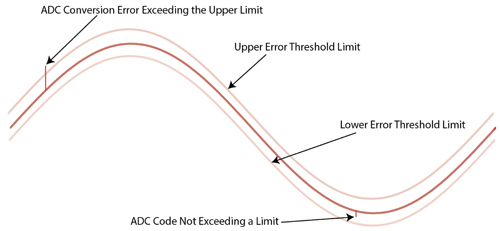

在高速ADC內,所有轉換誤差的產生都不是均等的。誤差的強度相當的重要,因為某些誤差絕對遠比其他誤差重要。舉例來說,一個或兩個最低有效位元(LSB)誤差可能會在系統的期望雜訊層內,而且可能甚至不會衝擊到即時性能。然而,一個最高有效位元(MSB)誤差,或者甚至是一個滿刻度誤差,都有可能潛在地導致系統故障的事件。因此,CER測試必須要具有一個機制或是臨界值,藉以對轉換中發生誤差的嚴重程度進行評等(圖4)。

|

| 圖4 來自於ADC取樣的重建正弦波,可以看到其具有上方與下方臨界值限制的界線。當編碼超過了限制,它就會被判定為轉換誤差。仍然位於臨界值之內的良性線性離群取樣不會被視為轉換誤差。 |

對於轉換的誤差臨界值,應該要包含已知的ADC線性度缺點,以及時脈抖動和其他超出轉換器能力之外的系統雜訊。此通常會累計加總到4或5個LSB,或是14位元ADC的16-32個碼,針對任何特定的取樣。其可能或多或少必須要依據ADC的解析度、系統性能以及應用裝置的誤差率需求而定。當這個誤差波段被用來與理想值做比較時,超越此限制的取樣就會被計算為轉換誤差。在傳統的視訊ADC當中,這種誤差被稱為閃光碼(Sparkle Code),因為它會在視訊螢幕上產生一個明亮的白色像素閃光。

可接受的轉換器誤差率將會大幅地依據訊號處理系統的需求以及系統對於誤差的容錯度而定。舉例來說,一個在後院使用行動藍牙喇叭系統的使用者可能可以容忍每小時數個誤差,而且甚至完全不會注意到。一個搭載於太空衛星內的任務重大的感測器可能需要最小的轉換器不明確度,否則衛星也許會從天空中掉落下來。也許並不會那麼嚴重,但是很糟的狀況可能會發生,例如不良的電視收訊。

以往所測得的GSPS ADC轉換誤差率通常不會優於1e-14。對於1e-12的誤差率而言,此意味著轉換器不能在1e12(1兆)次的取樣中產生轉換器誤差。1e-15的誤差率所代表的是轉換器不能在1e15(1千兆)次的取樣中產生轉換器誤差。藉由目前最先進之轉換器技術的高取樣速率,這可能似乎相當龐大,但是仍然能夠予以處理後做為CER之測試。

然而,對於具有8奈秒(ns)取樣速率的125MSPS轉換器來說,1兆次的取樣需要800秒(1e12×8ns)或是大約13分鐘。1千兆次取樣則需要800,000秒(1e15×8ns)或是9.24天。對於在這些誤差率中的95%信賴水準,必須分別將這些取樣期間乘以2.996(圖5)。

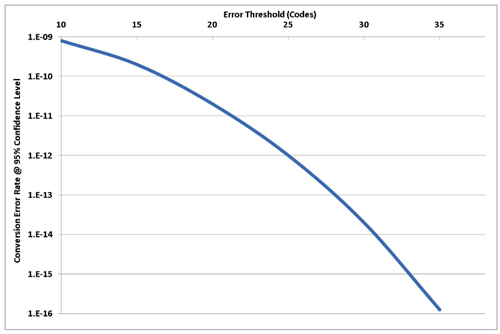

|

| 圖5 CER vs. 誤差強度臨界值的圖表。位於測試上的誤差臨界值限制(以ADC編碼)將會在特定信賴水準下對CER造成衝擊。 |

針對CER進行測試

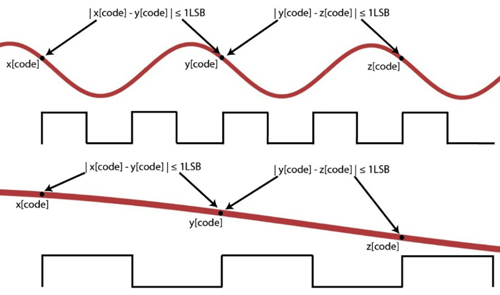

圖6是一張極為簡單的方塊圖,說明了內部ADC核心如何能夠針對其CER進行測試。相對較慢的頻率正弦曲線可以用來做為類比輸入,而以恰好或是接近ADC最大編碼速率進行取樣。類比輸入訊號是被計畫好的,因為如此一來從一個取樣到下一個取樣的預期絕對差異,就能夠很理想的不會超過1LSB編碼(忽略系統雜訊)。在理想狀態下,類比輸入訊號會略為大於滿刻度,因此所有ADC的編碼都會被加以運用。類比輸入以及編碼取樣速率應該要予以計算,如此較長週期的連貫性才能加以建立,而ADC就不會以相同的編碼位準持續地取樣。

|

| 圖6 兩個針對CER測試的取樣狀況。上方所示的取樣為只有比Fs/2稍微快一點的類比訊號,其中只有每隔一個取樣進行比較。兩組連續取樣的差異很理想的沒有超過一個LSB編碼。下方所示為相對較慢的類比輸入超取樣,如此兩組相鄰取樣的差異也不會超過一個LSB編碼。 |

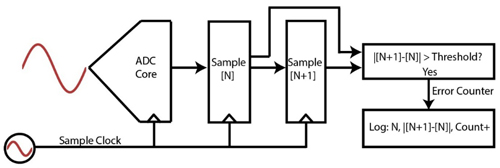

當時間超過臨界限制時,使用計數器來追蹤兩組相鄰取樣之間強度差異的情況,將此情況視為轉換誤差。計數器必須在整個測試期間內維持累積總誤差。為了確保系統能夠如預期般運作,誤差的強度與理想狀況應當也要加以記錄。測試所需要的時間將會依據取樣速率、所希望的測試轉換誤差率,以及所欲達成的信賴水準而定(圖7)。

|

| 圖7 CER測試比較兩組連續ADC取樣至預先定義好的誤差臨界值。計數器會記錄誤差的發生、強度、以及取樣位置識別符。 |

分辨量測與模擬狀況

在挑選具有低CER的ADC時,系統工程師應該要有能力分辨能夠被實際加以測試,與那些只有以設計模擬狀況做為依據之表列規格間的差異並加以比較。舉例來說,使用1GSPS ADC而要求具有95%信賴水準、1e-18的CER並且沒有誤差,必定是只有依據電路的模擬或是幾近一個世紀之久的持續量測。簡單的計算能夠協助證明此論點。要量測達到95%信賴水準的1e-18的CER,對於即使是具有1奈秒取樣速率的相對快速的1GSPS ADC,都將須要消耗29.96億秒(2.996×1e18×1ns)或是大約95年。

雖然與數位位元誤差測試在概念上有所差異,但即使是GSPS ADC的轉換誤差率測試要精確量測時也會相當的冗長。使用於CER測試的信賴水準必須要低於100%,因為無止盡的量測是不可行的。ADC取樣在判定其意義為一個真實轉換誤差前必須與臨界值比較。即時測試系統會比較相鄰取樣,找出已經超過臨界值的顯著偏離。雖然典型的轉換器架構可以實現某些系統能夠接受的量測轉換誤差率,但是新的設計與誤差偵測演算法則正在推動其限制,以期能夠有更好的表現。

(本文作者為亞德諾特約技術專家)