隨著經濟從紙張型往數位資訊管理型方向發展,用於資料處理、儲存和網路的資料中心在商業、學術和政府體系等領域都發揮著重要的作用。不過,資料中心的供電和冷卻成本也隨之不斷攀升。更高的系統效率和功率密度已成為現代資料與電訊電源系統的核心重點,因為小型而高效率的電源系統可以節省空間和電費成本。

|

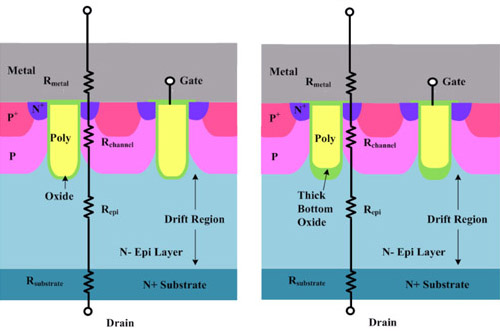

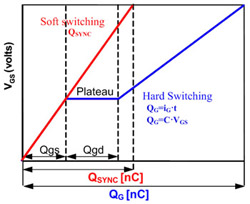

| 圖1 二極體整流與同步整流 |

從拓撲的角度來看,同步整流器的傳導損耗和開關損耗都更低,能夠提高這些轉換級的效率,所以開關電源次級側的基本構建模組,在伺服器電源或電訊整流器等低電壓及高電流應用中非常流行。同步整流器取代蕭特基整流器後,可讓電壓降變得更小(圖1)。

從元件角度來看,功率金屬氧化物半導體場效電晶體(MOSFET)在過去10年間出現長足的進展,催生出新穎的拓撲和高功率密度的電源。二十世紀早期平面技術(Planar Technology)問世後,中低電壓MOSFET迅速被開發出來,利用溝槽式閘極技術以大幅提高性能。溝槽式閘極MOSFET是中低電壓電源應用的首選功率元件,它把一個閘極結構嵌入在經小心蝕刻在元件結構上的溝槽區域中。這種新技術可以提高溝槽密度,並且無需場效電晶體(FET)阻抗元件,因此能夠使特徵導通阻抗降低約30%左右。當MOSFET的導通阻抗與洩極電流的乘積小於二極體正向電壓降時,同步整流的能量損耗便會降低。

不過,在同步整流方面,低導通阻抗並非電源開關的唯一要求。為了降低驅動損耗,這些元件的閘極電荷也應該很小。軟寄生二極體的反向恢復特性有助於削弱電流突波的峰值,從而降低緩衝電路損耗。另外,還有輸出電荷QOSS和反向恢復電荷Qrr造成的開關損耗。因此,中低電壓MOSFET的關鍵參數如RDS(on)、QG、QOSS、Qrr和反向恢復特性,直接影響到同步整流系統的效率。被稱為PowerTrench MOSFET的新型中壓功率MOSFET,則針對同步整流進行高度最佳化,可為伺服器電源或電訊整流器提供更高的效率和功率密度。

針對同步整流進行最佳化

在開關模式電源中,RDS(on)×QG FOM(品質因數)一般被視為衡量MOSFET性能的唯一最重要的指標。因此,已經開發出數項提高RDS(on)×QG FOM的新技術。雖然這些年來MOSFET技術和單元結構經歷了巨大的革新,但MOSFET垂直單元結構大致仍可分為平面型、溝槽型和橫向型等三類。在這三類結構中,溝槽式閘極MOSFET已成為BVDSS<200V的高性能分立式功率MOSFET的主流。這主要是因為這種元件不僅特徵導通阻抗特別低,而且能夠在BVDSS範圍內獲得出色的RDS(on)×QG品質因數(FOM)。

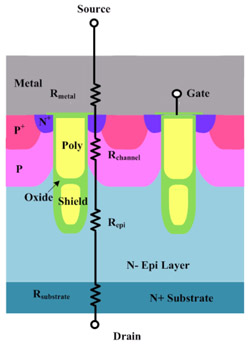

溝槽式閘極結構可以大幅減低溝槽阻抗(Rchannel)和JFET阻抗(RJFET),而對低電壓MOSFET(BVDSS<200V)來說,JFET阻抗正是造成導通阻抗的主要原因。溝槽結構能夠提供最短的洩極-源極電流路徑(垂直),以此降低RDS(on),利用這種出色的優勢,無需任何JFET夾斷效應(Pinch-off Effect)即可提高單元密度。每個區域的相關阻抗所占的百分比差異很大,視具體的設計與BVDSS而定。儘管降低傳導損耗必須降低RDS(on),但同時必須考慮到更高的FOM,對現有最佳化結構的溝槽深度和寬度進行權衡折衷。標準溝槽單元常常有一些設計上的變更,以保持低阻抗,同時提高FOM。圖2所示的傳統溝槽式閘極結構透過增加溝槽寬度與長度的比率來獲得更低的導通阻抗。為了提高開關性能,增大CGS/CGD比,隨之業界又開發出在溝槽底部生長一層厚氧化層的技術(圖3)。

|

| 圖2 傳統溝槽式閘極MOSFET 圖3 底部生長厚氧化層的溝槽MOSFET |

這種方案不僅有助於減小閘極-洩極疊加電容CGD,還能增大漂移區阻抗。此外,它也有利於降低導通阻抗與閘極電荷,因為現在可以一方面通過薄閘極氧化層來獲得更低的Vth與導通阻抗,同時還可以在溝槽底部採用加厚氧化層以獲得最低的CGD。

|

| 圖4 增加遮罩電極的溝槽MOSFET |

除此之外,還有一種技術是採用電荷平衡或超接面元件結構。其最初是針對高電壓元件開發的,現在也可用於低電壓元件。利用電荷平衡方案,可以在漂移區獲得二維電荷耦合,因而能夠在漂移區採用更高的摻雜濃度,最終降低漂移阻抗。快捷(Fairchild)最新的中電壓功率MOSFET就是採用這種遮罩閘極架構,其中遮罩電極與源極連接(圖4)。遮罩電極與電極和漂移區間的厚氧化層能夠讓漂移區的電荷平衡。相較於前一代技術,這種新型中電壓功率MOSFET不僅在特徵阻抗方面有大幅度改進,同時也進一步提高其原本已相當出色的開關特性。

除了RDS(on)和OG,外,同步整流結構中的其他參數如寄生二極體反向恢復、內部閘極阻抗及MOSFET的輸出電荷(QOSS,),現在也變得更具相關性。在開關頻率和輸出電流較高時,這些損耗元件的重要性就更為明顯。快捷的中壓MOSFET產品目前開始針對二極體反向恢復及輸出電容的最小化進行最佳化。

留意同步整流時產生之功耗

電源開關的主要功耗是傳導損耗和開關損耗,此外還有輸出電容引起的電容性損耗、洩極電流造成的關斷狀態(Off-state)損耗、反向恢復損耗和驅動損耗。在高電壓的大功率應用中,這些損耗常常被忽略。而對於數瓦(V)的應用,眾所周知,電容性損耗可能高達整體功耗的50%以上。必須注意的一點是,洩極電流超標的不合格元件可能導致散熱故障,尤其是在環境溫度高的情況下,然而這種狀況極為常見。

在低電壓應用中,驅動損耗可占總功耗的極大部分,因為相對於高電壓開關,低電壓開關的傳導損耗非常小。在輕負載條件下,傳導損耗極小,驅動損耗更為重要。隨著電腦節能拯救氣候行動(Climate Savers Computing Initiative)等新的效率規範的推出,驅動損耗成為輕載效率的關鍵因素。驅動損耗可透過下列的公式計算出來。

Pdrive = Qg.Vgs.fs ...................................(1)

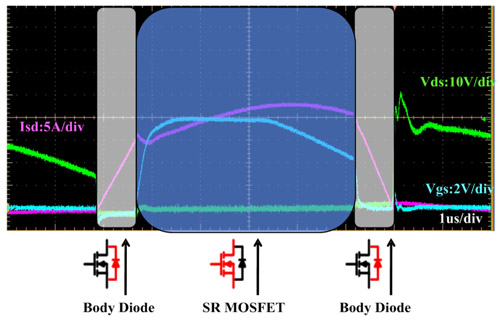

開關頻率和閘極驅動電壓屬於設計參數,而閘極電荷值則由資料手冊提供。同步整流與二極體整流器的一個不同處是,MOSFET是一種雙向元件。圖5顯示在一般情況下,在傳導期間從源極到洩極流經MOSFET溝槽的電流,以及在死區時間內流經寄生二極體的電流。由於同步整流中,寄生二極體的導通先於閘極導通,所以同步開關可採用零電壓切換(Zero Voltage Switching)技術。由於同步整流中,軟開關在開關導通和關斷瞬間工作,dVds/vt為零。因此,CGD(因dVds/dt)的電容性電流也為零。

|

| 圖5 同步整流中功率MOSFET的波形 |

|

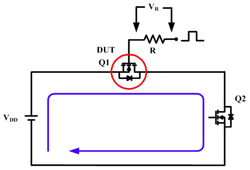

| 圖6 QSYNC的測量 |

有鑑於這種順序,應該謹慎選擇公式1中的閘極電荷值。由於導通瞬間同步開關上無電壓,此刻不會發生米勒效應(Miller Effect)。因此,得到的閘極電荷值近似等於總閘極電荷QG減去閘極電荷的閘洩極部分QGD。不過,這仍然是對驅動損耗的樂觀估計,而在實際情況下,同步開關的閘極電荷值並不等於簡單的QG-QGD估算值,這是因為在同步整流中,洩極和源極間存在一個負偏壓,而資料手冊中的QG和QG是利用正偏壓測得的。而且Vth以下的QSYNC曲線類似於Vth以上的斜線,因為同步整流中,在零電壓切換期間這兩個區域的洩極-源極電壓都為零。同步整流的閘極電荷QSYNC可利用圖6的簡單電路,並在Q1和Q2上載入適當的驅動訊號來進行測量。

|

| 圖7 QSYNC的定義 |

利用已知的電阻值,可透過公式2計算出QSYNC,這樣就可以更準確地估算出閘極驅動功耗。同步整流中,QSYNC較小,元件的性能也較好。如圖7所示,同步整流的功率MOSFFET的閘極-源極電壓上無平坦區。

..............................(2)

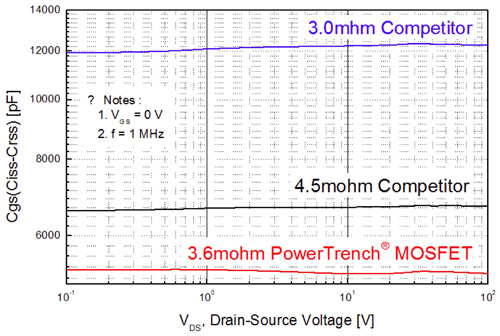

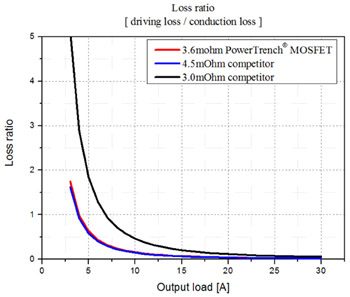

在同步整流中,要降低QSYNC,CGS(Ciss-Crss)是更為關鍵的因數。如圖8所示,由於設計獲得最佳化,相較4.5毫歐姆(mΩ)的競爭產品,3.6毫歐姆PowerTrench MOSFET的CGS大幅度減小。與競爭對手的4.5毫歐姆和3.0毫歐姆元件相比,3.6毫歐姆PowerTrench MOSFET的QSYNC分別降低22%和59%(表1)。圖9對閘極驅動電壓為10伏特(V)、開關頻率為100kHz的27伏特同步整流級的驅動損耗和傳導損耗之比進行計算和比較。此處有兩個同步開關,在10%的負載條件下,競爭對手的3.0毫歐姆產品的驅動損耗是傳導損耗的兩倍。

|

| 圖8 100伏特閘極-源極電容/3.6毫歐姆PowerTrench MOSFET與競爭對手產品的比較 |

|

| 圖9 不同輸出負載條件下,損耗比(驅動損耗/傳導損耗)的比較。 |

資料手冊上規定的二極體反向恢復時間(Trr)與反向恢復電荷(Qrr),一般用於正向開關損耗的計算。利用資料手冊上的Qrr值來計算損耗時,須注意寄生二極體的反向恢復電流是許多參數的函數,比如正向電流IF、反向恢復diF/dt、DC匯流排電壓和接面溫度Tj,其中任何一個參數的增加都會導致Qrr的提高。資料手冊上的條件通常比典型的轉換器工作條件低。由於開關轉換器須盡可能快地對功率MOSFET進行轉換,邊緣速率如diF/dt可能比資料手冊上的條件快十倍之多,從而使同步整流的Qrr大幅增加。

輸出電荷Qoss和反向恢復電荷Qrr在關斷開關的同時也造成損耗。因此,Coss和Qrr產生的功耗可透過下列的公式計算出來。

Pcoss = 0.5Qoss.Vds.fs ..............................(3)

PQrr = Qrr.Vds.fs ....................................(4)

設法降低電流突波危害

把有害電流突波降至最小的一般原則是,採用短而厚的電路板和最小的電流迴路。然而,由於尺寸和成本的限制,這麼做難度頗高。有時設計人員必須考慮到機械結構的問題如散熱器和風扇,有時鑑於成本限制因素,不得不使用單面印製電路板。緩衝電路可作為一種可行的另類方案,用來在最大額定洩極-源極電壓範圍內管理電流突波。在這種情況下,額外的功耗是無法避免的。此外,輕載下緩衝電路本身產生的功耗也不可忽視。

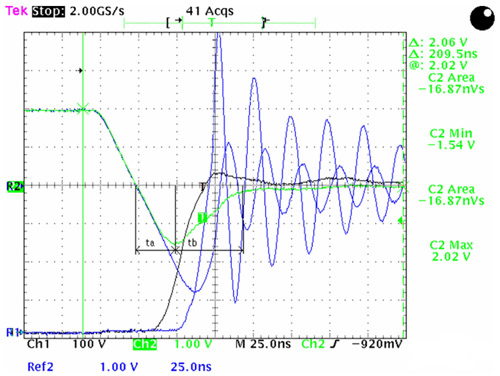

除了電路板參數外,元件的特性也對電流突波程度有所影響。在同步整流中,一個主要的元件相關參數是反向恢復期間的寄生二極體軟度因數(Softness)。基本上,二極體的反向恢復特性是由設計決定的。有好幾個控制輸入對反向恢復產生影響如接面溫度、di/dt和正向電流水平。但是,當條件固定時,二極體總是表現出相同的行為。因此,元件的電壓估算結果對評測系統的運作情況非常有用。圖10所示為兩個不同元件(但有極其相似的額定值)的反向恢復波形。

|

| 圖10 不同軟度因數的反向恢復波形 |

在反向恢復電流波形中,從零到峰值反向電流的這段時間被稱為ta。tb則定義為從峰值回到零的時間。軟度因數定義為tb/ta。一個軟元件的軟度因數大於1,而當其軟度因數小於1時,該元件被認為是「活躍」(Snappy)的。從圖10可看出,反向恢復期間Snappy二極體的峰值電壓較大。當所有條件都相同時,Snappy二極體的電流突波總是比較高,因此會在緩衝電路中造成額外的損耗。在輕載條件下,這一點可能比把導通阻抗RDS(on)減小1毫歐姆還要來得重要。

圖11所示為諧振頻率為400kHz的500瓦(W)相移式全橋(PSFB)直流對直流(DC-DC)轉換器中軟元件與Snappy元件的工作波形。軟元件的峰值電壓比Snappy元件的小10%,從而可讓緩衝電路的功耗降低30%,系統效率提高0.5%。儘管軟元件的RDS(on)比Snappy元件的要高25%,但在20%負載條件下,兩者的效率分別為94.81%與94.29%。在滿載下,兩個元件的效率相同。

|

| 圖11 500瓦PSFB直流電-直流電轉換器中功率MOSFET的峰值洩極-源極電壓,左為軟元件,右為Snappy元件。 |

軟寄生二極體的另一個優點是能夠使用額定崩潰電壓較低的元件。由於單位面積的導通阻抗與崩潰電壓成比例,所以還能降低傳導損耗。

關鍵在於降低傳導損耗

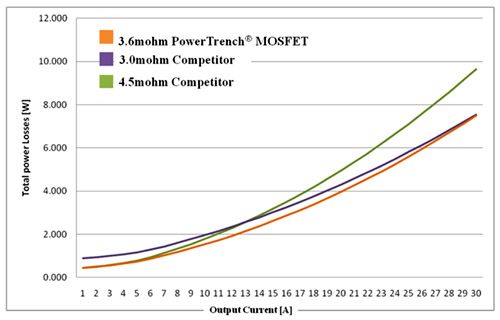

為同步整流建立更高效率的電源開關,低RDS(on)不是唯一的要求。隨著輕載效率的重要性增強,閘極驅動損耗和緩衝電路損耗變成是十分重要的損耗因素。因此,低QSYNC和軟寄生二極體成為獲得更高同步整流效率時非常重要的特性。不過,RDS(on)仍然是應用的關鍵參數。圖12所示為帶同步整流的800瓦PSFB中,在不同負載和不同元件條件下,不同元件的相關功耗。由於在10%負載條件下的驅動損耗和輸出電容性損耗更低,3.6毫歐姆PowerTrench MOSFET的總功耗比3.0毫歐姆競爭產品低43%。

|

| 圖12 800瓦同步整流電路的損耗分析 |

此外,3.6毫歐姆PowerTrench MOSFET的功耗主要源於滿負載條件下的傳導損耗,因此其功耗比4.7毫歐姆競爭產品的更低。從圖12總結的損耗分析可明顯看出,3.6毫歐姆PowerTrench MOSFET由於採用最佳化設計,因此可以大幅降低滿載和輕載條件下的功耗。

快捷半導體已推出新的PowerTrench功率MOSFET系列。這些元件兼具更小的QSYNC和軟反向恢復固有寄生二極體性能及快速開關等優勢,旨在讓整流應用提供更高的效率。由於閘極電荷和輸出電容所儲存的能量減少,開關效率得以提高,驅動和輸出電容性損耗得以降低。

(本文作者皆任職於快捷)