現今的數位邏輯設計者通常用微處理器、現場可編程閘陣列(FPGA)和網路互連建構極為複雜的電子系統。微處理器和FPGA的優點是能夠下載新資料來更新設計,而把系統連接到傳輸控制協定/網際網路協定(TCP/IP)乙太網路便能從遠端下載資料。

不幸的是,TCP/IP乙太網路並不是全無壞處。舉例來說,當系統連接到全球通訊網路--例如網際網路(Internet)時,任何其他電腦用戶也都可以存取這個系統。雖然網路上大多數用戶對存取別人的電子系統不感興趣。但仍有少數用戶喜歡通過網路的連接來存取多個用戶,而且更有部分人士有興趣的是如何破壞電子系統、達到個人目的。

事實上,很多駭客花很多時間在試圖獲得未經許可的網路電腦資源。有些駭客這樣做只是為了能夠自吹自擂、有些僅是為了查證系統的安全性與否,當然還有一些是想透過這些系統進行存取與控制,而最壞的情況,則是企圖破壞網路資源以獲取不法利益。

矛盾的是,系統必須具有毋需技術人員即能自動更新的功能,因此,為了進行遠距離管理,網路連接是顯而易見的選擇。但從另一方面來看,由於駭客不斷攻擊連接網路的系統,因而系統設計者勢必開發更高難度的設計。

嵌入式系統架構影響資訊安全甚鉅

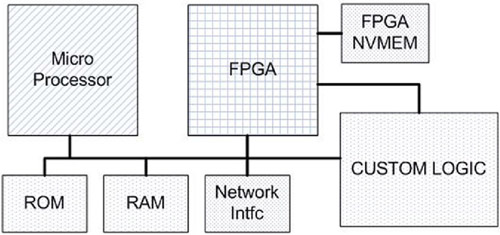

圖1為網際網路的嵌入式系統。從圖中可以看到系統有一個微處理器,用於儲存微處理器運算機器碼(Opcodes)的揮發性(Volatile)和非揮發性(Non-volatile)記憶體,連接基於TCP/IP網路的介面和存取至少一個FPGA,以及用來差異化產品的客製化邏輯。

|

| 圖1 互連網路的嵌入式系統 |

大多數FPGA元件是基於靜態隨機存取記憶體(Static Random Access Memory, SRAM)的揮發性記憶體元件。基於SRAM的FPGA需要額外的非揮發性記憶體,以在關閉電源或失去系統電源時用來配置元件的資料。

對駭客來說,圖1中的系統有潛在的弱點,而讓他們可用幾種方法存取嵌入式系統。最受歡迎的方法之一是攻擊網路介面。

因為攻擊目標的價值高低不同,對某些駭客而言,也許會放棄決定攻擊網路介面,但對具有決心的駭客來說,對系統進行實體存取攻擊雖然會耗費大量的時間和精力,卻仍舊意志堅定。

另一個攻擊點則是微處理器,特別是系統設計者慣用的微處理器。由於受到大規模的採用,因此熟悉x86、安謀國際(ARM)、美普思(MIPS)或其他常用處理器架構的駭客將具有優勢。駭客可能從觀察非揮發性記憶體讀取的運算機器碼中得到線索,以擊潰網路介面的防禦。當然,駭客也會明白如何為微處理器的執行添加新的指令集,並予以操縱。

此外,駭客也許會選擇攻擊作業系統或者應用程式。尤其行動電話、印表機、網路硬碟(NAS)驅動器和其他常見的應用,往往使用普通的作業系統或應用程式。而對作業系統和嵌入式系統應用程式的理解將會幫助駭客發動攻擊。有時這些攻擊會引起嵌入式元件不能正常工作;有時會讓系統允許未經授權者進行存取。

駭客的另外一個攻擊點則是FPGA的非揮發性配置記憶體。攻擊這裡的原因,大多是因為駭客決定對FPGA進行改寫再編程。而特別是如果FPGA的非揮發性配置記憶體在系統中是一個弱點,自然會被利用。

正如人們所知,大多數FPGA是基於SRAM的元件。而用於配置FPGA的資料多源於非揮發性記憶體。既然部分駭客擁有為FPGA產生新功能的技術,因此只要駭客有能力存取用來儲存FPGA設定資料的非揮發性記憶體,自然可以存放新的FPGA設定。在阻絕服務攻擊(Denial of Service, DoS)案例中,駭客只要下載一個毫無作用的新配置即可達成目的;而更壞的情況則是企圖損壞FPGA。同樣地,取決於系統的價值,駭客也許會讓系統仍然完好地運作,也許會複製FPGA的功能,並為他們自己的私人目的建立「額外」的功能。

善用防禦策略避免惡意攻擊

接下來要探討的是各種攻擊系統的情況,還有防禦攻擊的策略。但是無論如何,現實生活中的網路系統,本來就存在著風險。這也是為何設計者不得不花費許多時間來防止侵入和破壞系統。這樣的處理稱為固化(Hardening)。當然,固化的目標就是要在用戶易於存取、系統更新與防禦入侵之間尋找最佳平衡點。在這樣的前提下,防禦入侵策略自然也是相當多樣化的。

最容易的防禦策略之一,是使用非典型的TCP/IP埠。正常的情況下,每個IP資料封包都有相關傳送資料的埠。如電子郵件的埠數是25、超連結語法(http)是80、42則是名稱服務(Name Services)等。不過,雖然埠數可以從1~65,535,但網際網路位址指派機構(The Internet Assigned Numbers Authority, IANA)並沒有對大於49,151的埠數發行註冊。

在管理方法上,若在上述正常使用的埠上放置一個管理介面,將有助於遮掩系統本身。不過,這是極為基礎的保護措施,在沒有其他的防護層時並不建議使用。

而今日也已經有更加高級的防禦方法可以應用到TCP/IP上。例如嵌入式系統的管理介面通道可以對發送和接收的資料封包加密。常用的加密方法包括對稱密碼系統(Symmetric Cipher System)。再細分對稱密碼系統,則包括TwoFish、BlowFish、三重資料加密標準(Triple Data Encryption Standard, TDES)和先進加密標準(Advanced Encryption Standard, AES)等。加解密雙方用已知的金鑰對資料加密和解密。金鑰可以是單個共用(Single Shared),或者也可以是針對不同系統的特殊金鑰。

然而這兩種方法都有問題。在單個共用金鑰的情況下,解密一個系統就能訪問共用這個金鑰的所有系統;但當系統不是共用一個金鑰時,問題變成如何管理每個系統的金鑰。對一般人來說,如何管理大量金鑰是個大難題。

今日較佳的另一種選擇,則是用公共/私有(Public/Private)金鑰進行加密,或是熟知的非對稱加密(Asymmetric Encryption)。這個方法用兩個金鑰進行加密和解密。每個系統必須儲存一個公共/私金鑰。每個系統儲存一個公共金鑰並用於發送資料,而發送方用私有金鑰和接收器的公共鑰加密負載(Payload)。遠端系統用發送方的公共金鑰和自己的私金鑰解碼資料,如此一來兩個系統就能安全對話,當然,前提是要金鑰足夠複雜以防止猛烈攻擊。

不過,若用計算時間和頻寬來衡量,資料加密負擔頗大。因為很多情況下,系統設計者須要對從嵌入式系統進出的每一個資料進行加密。但事實上,其實只要加密某些關鍵的資料即可,這樣一來還可以適度緩解處理器負擔和網路頻寬。

同樣地,對更新的負載加密也許是不必要的,對設計人員來說,只要知道資料沒有被篡改就足夠了。有些加密演算法,例如安全數列演算法(Secure Hash Algorithm, SHA),允許標頭(Header)和頁尾(Footer)添加至未加密的資料。SHA資料就像複雜的校驗和演算,嵌入式系統送出校驗和資料,並執行校驗和演算法。如果校驗和資料與收到來自遠端系統的資訊相匹配,表示資料未被修改,可以用來對系統再編程。

所有這些方法都是眾所周知的,且已應用在許多系統之中。然而,系統設計者也許還沒有考慮用FPGA來改進系統安全性的方法。

新型態FPGA改善系統安全

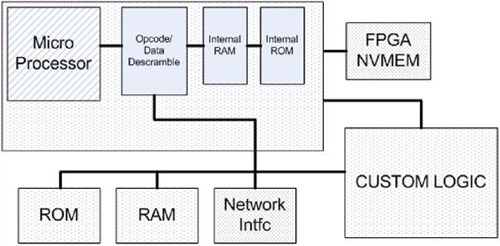

FPGA可以為嵌入式系統帶來額外的功能。圖2為修改後的嵌入式系統,而更新的系統把一些外部的元件功能併入了FPGA,例如外部的微處理器就放入了FPGA內部。

|

| 圖2 基於軟微處理器的嵌入式系統 |

對很多人來說,軟微處理器(Soft Microprocessor)是一個新名詞。確實,與現有的產品相較,軟微處理器產品很少。但正因如此,如果駭客不了解軟微處理器,他們惡意入侵的目的就難以得逞。畢竟在軟微處理器中,駭客只能看到二進位資料,而不能獲取原始機器碼和除錯符號(Debugging Symbols)。有些軟微處理器甚至看不到運算機器碼,因為它們存放在FPGA的內部記憶體中。因此,除非更新過程遭到破壞,否則駭客根本得不到任何關於嵌入式系統控制處理器的資訊。

駭客使用的另外一種方法,是在軟微處理器之前增加專屬運算機器碼或資料解碼器。但現在即使駭客得知使用了哪種微處理器,他們仍必須確定運算機器碼與資料是如何被加密編碼(Scrambled)的,而這些用現成的微處理器是無法實現的。當然這個方法的優點是使用原始機器碼,而針對微處理器產生碼的工具正在討論之中。目前市面上已有軟微處理器編譯器和鏈結器為開放原始代碼,使得添加運算機器碼加密編碼器成為可能。對於缺少原始碼的編譯器和鏈結器,必須鏈結唯讀記憶體(ROM)後實施加密編碼。

軟微處理器另外的優勢在於,假設處理器運行的運算機器碼對駭客是可見的,亦即他們已經確定微處理器的種類,則軟微處理器可以執行客製化運算機器碼(Custom Opcodes),讓駭客不得其門而入。這些運算機器碼可以用來模糊微處理器操作,迫使駭客耗費更多精力在確定微處理器所執行的功能上。

當然,儘管沒有使用運算機器碼、資料解碼技術或客製化運算機器碼,基於FPGA的軟微處理器在系統安全性方面仍具有優勢。大多數FPGA都有內部RAM和ROM。在配置元件時,這些區塊必然能夠載入資料,這意味著儲存在這些記憶體中的資料有很高的透明度,因此駭客只能通過非常內行的專家對進入FPGA的配置位元流進行解碼,才能確定在這些記憶體中的內容。

破解人員不僅必須是專家,他們還要判斷元件中的記憶體是如何組織。典型的FPGA中雖僅有數百個記憶體區塊,但事實上是不可能確定配置位元流中運算機器碼和資料是如何安排的。因此,這些記憶體顯而易見地成為儲存關鍵演算法--私有金鑰的地方。

值得注意的是,最近開發的基於SRAM的FPGA能夠把加密演算法加到配置位元流。而具有AES-128金鑰的FPGA更讓確定配置位元流的內容變成不可能。

可編程邏輯元件提高防禦等級

無論設計者選擇哪種方法來鞏固嵌入式系統,最終系統接收的負載資料仍須通過編程方式存入非揮發性元件。非揮發性元件可能是記憶體、FPGA配置記憶體,或可編程邏輯元件(CPLD)。微處理器負責對這些元件編程和抹除。在並行快閃記憶體的情況下,演算法編制成文字檔,讓硬體工程師可以很容易地照著做。而附屬FPGA的記憶體和CPLD通常需要更多的演算法。

對於CPLD和FPGA配置記憶體來說,最好使用元件製造者提供的原始代碼。因為製造者的非揮發性PLD元件編程演算法相當多元,甚至同一製造商開發的元件也不相同,而可編程原始代碼和應用這些演算法的資料由於顧及每個元件的差異,使得編程更加容易。

FPGA配置記憶體還可能須由特定製造者編程代碼來處理。事實上,根據非揮發性記憶體依附FPGA的方式,對非揮發性串列記憶體再編程似乎是件簡單的事。但是,為了給設計者留出更多的輸入/輸出介面(I/O),FPGA供應商須把特殊的電路放入元件中,讓串列記憶體可使用配置FPGA的相同I/O接腳進行再編程的工作。因為附加的電路複雜化編程任務,因此須要用元件製造者開發的原始代碼進行最佳處理。這個方法的另一個優點是具有控制軟體重置(Soft-reset)功能。更新非揮發性記憶體後,可以選擇從新的鏡像(Image)再載入FPGA。

針對多個元件編程,已有業者提供資料文字檔格式和原始碼框架。然而,不管框架的性質如何,超出設計者控制的事情仍然會發生,並不確保更新非揮發性記憶體一定成功。

可能有一些原因導致對非揮發性記憶體抹除和再編程失敗,這些原因可能是顯而易見的電源故障或極為細節的編程演算法故障。

在這些情況下,基於軟微處理器的嵌入式系統有潛在的優勢。現有的處理器,破壞初始化機器碼使系統不能通過遠端訪問來恢復,而技術人員必須到場維修這個故障系統。

新的FPGA則具有安全的方法初始化記憶體--它們從主要載入區讀取配置資料。如果FPGA未能合適地配置,它可以切換到第二個初始化鏡像區域。第二個初始化鏡像區域不是常規,基於軟處理器的FPGA有較高的從災難事件中恢復的可能性。軟微處理器系統,具有不須依賴讀取易損壞的非揮發性記憶體的開機和編程韌體設計,能夠使遠距離的恢復策略可行。

使用軟微處理器和前面所述的技術,元件的物理安全性可得到大幅提升。當然,駭客仍然能夠接觸系統的網路部分。系統設計者仍須評估要花多少努力和資源來鞏固網路介面。針對未授權的更新,選擇FPGA加密配置位元流的設計者改進了嵌入式系統的安全性。毋需任何TCP/IP提示,加密的FPGA配置資料改進了系統的安全性。這是防止駭客破壞系統關鍵部分。

(本文作者任職於萊迪思)