USB 3.1將開創下一個行動介面王朝。USB 3.1融合10Gbit/s、USB PD和Type-C連接器規範,可望滿足各式資料/影音傳輸應用;其中,USB PD和Type-C搭上行動裝置輕薄、快充設計熱潮,已吸引IP、晶片商和品牌廠競相布局,率先在市場上走紅。

尤其蘋果(Apple)和Google搶先在商用筆電中導入Type-C連接器後,這股熱潮正迅速蔓延至整個業界,並催化筆電接口功能外移的極簡設計風,帶動周邊集線器(Hub)、擴充基座(Docking),以及新型小體積、中大功率電源供應器開發需求,將為介面和電源晶片商捎來龐大商機。

增添三大新功能亮點 Type-C商機晶片商按讚

|

| 圖1 創惟科技技術長室資深技術�行銷經理魏駿雄強調,Type-C連接器係讓筆電接口功能外移的關鍵推手。 |

創惟科技技術長室資深技術行銷經理魏駿雄(圖1)表示,在MacBook系列、Ultrabook產品的輕薄設計帶動下,筆電「海岸線」空間不斷微縮,以致牽動高速傳輸介面和連接器規格改良需求,因此,英特爾(Intel)、蘋果等大廠遂聯手在USB-IF催生Type-C的全新標準,將小尺寸、正反可插、支援大電流和高速率等多種功能特性集於一身。

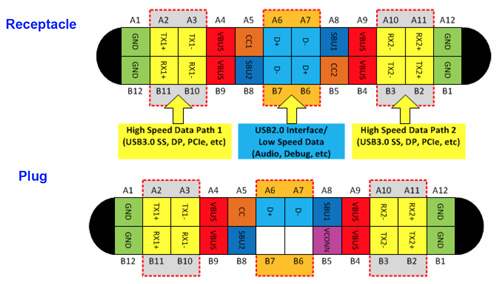

相較於傳統僅五接腳的USB Micro-B接口,Type-C接腳數一舉擴充至二十四支,以上下各十二支對應接腳的架構排列,進而縮減占位空間,實現10Gbit/s傳輸率且正反皆可插拔的使用模式(圖2)。同時,Type-C更定義全新的配置專用通道(Configuration Channel, CC),除可用於母座(Receptacle)偵測正反面插入、裝置為來源端或接收端,以啟動連結功能外,還可對應到公頭(Plug)的Vconn接腳提供纜線電力,同時支援USB PD 2.0版的雙相標記編碼(Bi-phase Mark Coding, BMC),以預留未來將充電功率推上100瓦(W)的空間。

Type-C一次亮出高速、高功率、正反可插的三大功能,已成業界鎂光燈焦點,儘管初期以筆電導入為主,但蘋果、三星和中國大陸手機廠亦正馬不停蹄展開設計,可望在今年下半年到明年推出內建Type-C的旗艦機種。

|

圖片來源:USB-IF,立錡整理

圖2 USB Type-C連接器架構圖 |

通用序列匯流排(USB)3.1亮出三大規格王牌,躍居行動介面市場新寵。2014年11月,USB-IF正式提出USB 3.1 Gen 2、傳輸速率高達10Gbit/s的新標準,同時也揭櫫USB電力傳輸(PD)2.0方案,將充電功率提升至20伏特(V)×5安培(A)的高規格,以及支援前述兩項標準並可正反插拔的Type-C連接器與纜線規範,促進USB介面聲勢衝上前所未見的高點。

魏駿雄指出,Type-C功能將驅動新的晶片設計與導入商機;首先,介面晶片商要由USB 3.1 Gen 1的5Gbit/s跨入Gen 2的10Gbit/s規格,必須將製程節點從既有的0.13?0.11微米一口氣推進至5x奈米,以符合更高頻率和傳輸速率的設計需求,而5x奈米在光罩、前段CAD設計/模擬工具和後段封測機台皆是一筆新投資,將促進整個產業更加活絡。

與此同時,Type-C助長筆電接口功能外移的風潮,將刺激擴充基座中的USB集線器控制器、訊號轉換晶片需求;再搭配USB PD 2.0的100瓦供電方案,更可望打破現今筆電電源轉換器各家規格壁壘分明的局面,甚至挺進顯示器電源等應用領域,為相關集線器晶片商、電源IC廠創造新契機。

突破高瓦數充電限制 高整合USB PD晶片上陣

Type-C雖已原生支援5V3A的行動快充功率規格,但對於筆電、顯示器等更大功率的電源需求仍稍嫌不足,因此未來Type-C結合USB PD 2.0,達成100瓦供電的設計勢將有助其應用版圖再下一城;此類方案也成為許多筆電和周邊裝置製造商下半年的產品布局焦點。

立錡科技AC-DC事業處行銷一處副處長詹振輝(圖3)表示,USB 3.1通訊協定和Type-C連接器標準的終極目標是One Cable for All,包括乙太網路(Ethernet)鏈結、電源、高速資料與影音傳輸均是其計畫攻占的應用;為滿足各種不同使用情境,更大功率的供電源遂變得至關重要,因此USB PD也應運而生,成為延展USB勢力的利器。

|

| 圖3 立錡科技AC-DC事業處行銷�一處副處長詹振輝認為,Type-C結合USB PD方案須同時考量數位和類比製程設計。 |

事實上,第一波內建Type-C的筆電僅能支援2.5A電流,甚至還達不到Type-C制定的5V3A功率規格,遑論USB PD 2.0最高20V5A標準,癥結就在於電磁干擾(EMI)與安全性方面仍有疑慮。因此,介面和電源晶片業者正積極開發符合CC接腳和USB PD協定的控制器,以及相關金屬氧化物半導體場效電晶體(MOSFET)、Power-path Switch等電源管理方案,以盡早突破Type-C連接器的功率限制。

詹振輝也強調,負責電源訊號通訊的CC接腳屬於數位邏輯運算設計,而USB PD電源管理晶片(PMIC)及周邊功率元件則偏向高壓類比製程,故現階段業界大多採用雙晶片方案,但也伴隨著成本增加的問題;因此立錡遂統整旗下微控制器(MCU)和PMIC技術,近期已順利採用30V高壓製程,打造整合CC控制和USB PD電源管理的系統單晶片(SoC),並攜手創惟開發USB PD的集線器、擴充基座參考設計,將有助Type-C連接器達成更高功率供電。

確保大電流纜線品質 E-Marker晶片需求看漲

威鋒電子產品經理Terrance Shih(圖4)表示。在USB PD設計方面,系統廠除須導入關鍵的控制器外,還須在Type-C纜線端加裝電子標記(Electronic Marker, E-Marker)晶片,以支援3A以上的大電流,並記錄訊號衰減情形進一步補償,確保纜線的傳輸品質。

|

| 圖4 威鋒電子產品經理Terrance Shih說明,Type-C屬於連接器規範,不等於USB 3.1 Gen 2的通訊協定標準。 |

換句話說,E-Marker晶片將是實現USB PD的關鍵推手。Shih進一步指出,許多USB連接器和纜線開發商正密切關注此一新興元件,相繼釋出導入計畫,以快速滿足USB Type-C筆電、多功能擴充基座和顯示器設計需求;因此威鋒近來也積極布局E-Marker晶片,並於近期通過USB-IF認證,且在甫落幕的2015年台北國際電腦展(Computex)秀出大量支援Type-C/USB PD的終端產品原型。

衝上10Gbit/s超高速 中繼器/MUX晶片需求湧現

Shih透露,由於USB 3.1 Gen 2速率為10Gbit/s,並向下相容Gen 1和USB 2.0規格,預料EMI與訊號完整性挑戰將更加艱難,引發如訊號中繼器(Repeater)、Retimer和多工器(MUX)等周邊配置晶片的搭載需求。

事實上,連接器邁向高速率、高功率將產生嚴重的EMI問題,影響USB傳輸和充電功能;這也是三星(Samsung)在Galaxy Note 3搶先導入USB 3.0(USB 3.1 Gen 1、5Gbit/s)連接器卻在下一代產品移除的最主要考量。

祥碩科技產品行銷經理張欽俞(圖5)表示,每一代高速傳輸介面標準提升傳輸速率是必然的趨勢,但也會帶來更多技術挑戰;舉例來說,在USB 3.0標準問世前,業界幾乎不討論Repeater、Retimer等元件,因為效益不明顯;然而,USB 3.0進入Gbit/s領域後,訊號抖動(Jitter)、衰減的情形明顯加劇,且整個傳輸路徑中,訊號每通過一個元件抖動影響就會再放大,故須增強或重組訊號,才能達成該有的訊號品質。

|

| 圖5 祥碩科技產品行銷經理張欽俞�表示,USB影音傳輸功能不足的桎梏,可望由更高頻寬的USB 3.1克服。 |

至於MUX晶片則負責判斷高低速訊號切換的任務。張欽俞指出,Type-C連接器將支援USB 2.0、3.0和3.1 Gen 2,甚至能透過Alt Mode相容DisplayPort、行動高畫質鏈結(MHL)訊號,因此須利用MUX機制偵測來源端和接收端訊號,讓主控端晶片了解所需速率和協定格式。

針對上述需求,祥碩除打造符合USB 3.1 Gen 2的主控端晶片外,亦搭配開發多款Repeater和MUX解決方案,從而協助系統廠實現10Gbit/s訊號鏈設計,並達成距離較長的PCB電路布局,以及與其他介面標準互通的Alt Mode模式。張欽俞透露,今年下半年該公司USB 3.1系列晶片將陸續通過USB-IF認證,只須進行軟體調校就能邁入大量出貨階段。

多協定IP子系統登場 Type-C Alt Mode速成形

事實上,Type-C出發點是為了滿足行動裝置輕薄外型又能持續推升傳輸速度的需求,以突破現有USB Micro-B的瓶頸,以及USB 3.0接口須額外擴增兩路高速通道,致使連接器寬度遽增的窘境;該規範出爐後,DisplayPort、MHL,甚至英特爾獨家的Thunderbolt等介面技術陣營也相繼發布Type-C Alt Mode相容標準,足見其影響力遍及整個介面應用領域。

尤其這也點出一個重要的產業變化,亦即行動裝置已成為半導體和電子科技產業技術革命的中心,無論PC或消費性電子供應鏈皆難以忽視這股浪潮,促使介面標準由PC端引領發展,翻轉為行動裝置領軍的新樣貌,從蘋果新款MacBook捨Thunderbolt轉投Type-C,從而醞釀旗下PC、平板和手機接口全面互通設計,更可應證此一趨勢。

益華電腦(Cadence)IP首席應用工程師李志勇(圖6)表示,對處理器廠商而言,Type-C支援多種協定和傳輸速率,不僅造成SoC內部IP設計複雜度激增,亦加重實體層(PHY)通訊協定設計負擔,進而影響晶片上市時程和成本。尤其處理器業者正集中資源推動16奈米鰭式電晶體(FinFET)先進製程,加上Type-C、DisplayPort、MHL等標準規範動輒上千頁,皆讓業者對自行投入研發IP並進行整合的方式紛紛打起退堂鼓,轉向採納介面IP供應商的解決方案。

|

| 圖6 益華電腦(Cadence)IP首席應用工程師李志勇指出,介面IP子系統可有效縮短SoC開發時程。 |

瞄準業界需求,李志勇指出,Cadence已開發一套融合USB 3.1 Gen 2、Type-C、PCIe、行動產業處理器介面(MIPI)、DisplayPort/eDP、SATA和乙太網實體層通訊協定的IP子系統,可協助晶片商快速且低成本的導入最新介面標準設計,進而實現Type-C連接器多協定相容設計。

李志勇更透露,DisplayPort/Type-C Alt Mode極具未來應用發展潛力,因此Cadence也特別開發Multi-protocol訊號鏈架構,以雙管線(Lane)分別支援USB 3.1、DisplayPort訊號的方式,省去外掛一顆MUX晶片做訊號切換的需求,進而節省物料成本,加速拱大Type-C連接器商用規模。

CTS明年亮相 Type-C引動量測新商機

Type-C熱潮不斷滾出新商機,未來相關量測需求亦是業界關注重點。據悉,USB-IF預定在2016年確定Type-C/USB PD 2.0版的相容性測試規格(CTS),以及量測儀器、治具、軟體和測試實作方法(MOI),屆時可望為儀器商挹注營收成長動能。

太克科技(Tektronix)資深應用工程師黃芳川(圖7)表示,為確保高速訊號傳輸品質,USB 3.1 Gen 2的測試將特別注重接收端的接收能力,因此儀器商須開發能模擬極差訊號抖動狀況的訊號產生器,以及支援更高頻率和採樣率的示波器,協助晶片和系統廠驗證產品性能。

|

| 圖7 太克科技資深應用工程師黃芳川指出,2016年USB 3.1相關測試規範底定後,該公司將全力卡位測試商機。 |

黃芳川指出,未來USB 3.1 Gen 2、Type-C和USB PD規格皆須納入設計考量,將大幅提高晶片商、系統廠測試成本和時間的負擔,因此完整的軟硬體自動化測試方案將顯得非常重要;目前太克已提供誤碼率測試(BERT)、抖動容忍度(Jitter Tolerance)測試平台,以及MOI等USB 3.1實體層設計自動化驗證工具,可望加速業界研發步調。

另外,宜特科技訊號測試處協理余天華表示,DisplayPort或MHL的Type-C Alt Mode將是儀器商和驗證實驗室下階段布局重點。其中,MHL/Type-C Alt Mode可實現4K行動影音串流,而下一代superMHL更將推上8K解析度規格,遂吸引業界較多關注。

余天華指出,MHL聯盟正與USB-IF密切合作,最快將在下半年到明年發布Type-C來源端和接收端的Alt Mode CTS規範,並將列入高頻寬數位內容保護(HDCP)測試方案,以加速Type-C從USB以往專注資料傳輸的架構,順利接軌影音串流設計,將帶動前所未見的USB設計與產品測試需求。此外,下一代superMHL標準亦可望延續兼容Type-C連接器的策略,屆時更將掀起一波8K影音串流設計驗證商機。

力抗EMI/RFI挑戰 無露孔連接器受矚目

無庸置疑,USB 3.1 Gen 2、USB PD和Type-C已成業界新寵;而上述標準規格得以進入行動裝置領域的時間點更是引人注目。

廣迎工業連接事業處處長鍾軒禾(圖8)表示,USB 3.0受限於EMI、射頻干擾(RFI)問題,在行動裝置上的發展顯然不順;為避免Type-C未來面臨同樣問題,並達成USB-IF要求的插拔一萬次耐久度,廣迎已率先提出無露孔的連接器公頭機構專利,將有效抑制EMI和RFI情形。

|

| 圖8 廣迎工業連接事業處處長鍾軒禾認為,Type-C連接器必須克服RFI問題,才能順利在手機市場崛起。 |

鍾軒禾解釋,RFI現象是從裝置端到主控端,高頻特性不連續而無法匹配所造成,重點在於降低連接器的串音(Crosstalk)干擾、插入與回授損失,並提高訊號對稱性與縮短延遲,同時以特徵阻抗達成連續匹配。這些概念必須透過在連接器機構上實施接地隔離,以防止RFI產生,並須注意高頻訊號四周參考層的電位差,以免引發共模和差模效應,致使RFI在系統間瀰漫。

也因此,廣迎開發無露孔架構,並已於各國申請專利。該方案在高頻訊號上下兩層與左右兩側均以接地處理,可完全做到電磁屏蔽(EMC Shielding),消除大部分RFI。同時,該公司在連接器高頻差分訊號接腳兩側利用邊對稱處理,採用V+/S+/S-/V-四個一組排列,顯著改善接觸阻抗(Mated Impedance)、插入損耗(Insertion Loss)和差動共模效應,更進一步抑制RFI。

鍾軒禾強調,一旦Type-C克服RFI、EMI問題,就能快速攻進智慧手機市場,為相關供應鏈業者帶來新一波商機。