隨著摩爾定律開始遭遇瓶頸,半導體產業對於該定律的發展亦產生質疑,催生3D IC的興起。尤其高昂的先進製程成本,已讓SoC功能整合不再符合經濟效益,因此,利用立體堆疊的3D IC,將成為延續摩爾定律的重要關鍵。

|

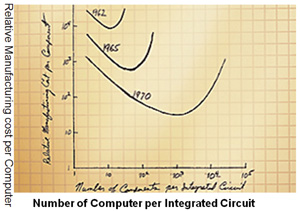

| 圖1 最早的摩爾定律 |

英特爾(Intel)創辦人之一的摩爾(Gordon Moore)在1965年預測單一矽晶片的電晶體數目,每隔18月將會增加一倍(圖1),這就是著名摩爾定律(Moore's Law)的原由。幾10年來,全世界半導體的發展大致都不脫摩爾定律的預測,但製程技術改進已近極限,如何維持定律中的成長速率,或許答案就在三維晶片(3D IC)。

摩爾經濟學風行數十年

摩爾定律在半導體領域已經形成一個所謂的摩爾經濟學。這個經濟學不僅使其成了英特爾的發展方針,也是全世界半導體領域很自然的追求目標。即便全球半導體技術藍圖(International Technology Roadmap for Semiconductors, ITRS)也一直都是跟隨著摩爾定律。此外,台灣的產、官、學、研也都是以摩爾定律為半導體相關領域研究與政策制定的圭臬。

摩爾定律改變半導體業界,也改變資訊科技(IT)產業。光是在Google Search裡面可以至少發現三百四十八萬筆摩爾定律的資料。其實,摩爾定律只是一個發現,也不是一個科學定理,至少摩爾當初在他的文章內並沒有說這是一個定律。

摩爾定律最初也只指出元件數目會每18個月增加一倍,但並沒有說頻率和效能也會增加一倍。有趣的是,摩爾一開始是說12個月會有一個半導體新世代,到了1975年他自己把時間延到24個月,18個月是其他人幫他改的。最後,摩爾的文章根本也沒有談到微處理器的變化這件事。儘管如此,摩爾定律仍神奇地靈驗了40多年。

摩爾定律雖然應驗了40年,但至少在20年前,就有學者開始計算或是討論它的死亡日期。1980年代,從光學微影(Optical Lithography)的角度來看,摩爾定律應該在400奈米(nm),也就是0.4微米(μm)左右就要停止,這是因為當初所使用的曝光機台的光波長約是436奈米(G-line),所以根據物理的基本概念,特徵尺寸(Critical Dimension)在400奈米就應該停止。

當然,最簡便的方式就是提升機台效能,使用更小的波長到365奈米、248奈米與193奈米。這讓摩爾定律得以再繼續存活20年。但是,從表1中可以看到,曝光機台的光波長自2003年就沒有再進步,雖然目前有加入所謂的水浸潤式微影(Water Immersion Lithography)技術,但已經快使用光所有可以用的製程技術。

摩爾定律促成SoC蓬勃發展

摩爾定律的發展推升系統單晶片(System on a Chip, SoC)的出現,回過頭檢視系統單晶片的優點,過去以來都認為它可以降低成本、執行效能增加、降低耗電量、體積縮小以及增加可靠度。當然,因為要達到一個IC具有所有系統的功能,就必須在布局(Layout)、時序(Timing)與訊號整合度(Signal Integrity)上付出時間(人力)與金錢(EDA工具)的龐大代價。

但是,系統單晶片早在2003年的國際固態電子電路會議(ISSCC)中也已經被英特爾的一位架構(Architecture)主管Jay Heeb宣告死刑,從那時候開始,大家才開始認真的討論到底摩爾定律還可以存活多久?何時會中止?因此,各家市場分析公司與學者開始從技術與經濟的觀點上嚴肅的討論摩爾定律的終點。

從表2可以看得出來,若是從技術的觀點來看,大約是在2014~2018年間,若是從經濟的觀點來看,大約是在2020年。有學者認為,若是量子力學可以用在積體電路,到時候電子是一個電晶體的最小單元,那麼摩爾定律可以撐到2035年。著名的市場分析公司則認為,2009年英特爾的凌動(Atom)晶片是最後一顆符合摩爾定律下的晶片。

|

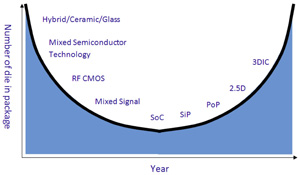

資料來源:Xie Yuan

圖2 系統單晶片是封裝技術的轉捩點 |

圖2是賓州大學教授謝源(Xie Yuan)所提出的半導體發展微笑曲線。可以看到系統單晶片之前,都是透過離散元件將射頻(RF)、混合訊號(Mixed Signal)、Ceramic/Glass等元件以一到數個IC整合在一起,直到系統單晶片出現,似乎有了一統江湖的味道。因為,夢想中的單一晶片似乎可以將所有的半導體技術整合在一個晶粒當中。

這的確是一個夢想,也很難達到。主要的原因是光罩與製程的價格實在太高,除非是財力雄厚的公司,否則根本玩不起系統單晶片。這個曲線似乎也在呼應宏碁董事長施振榮於1992年所提出的獲利微笑曲線,系統單晶片看來並不是可以獲利的最好技術,可能是最差的技術。別忘了摩爾第二定律--Rock's Law,也就是雖然元件增加兩倍,晶圓價格並不會增加兩倍,相對的晶圓製造費用可能是兩倍。所以,英特爾在2003年便提出SO3D--System-in-3D-Package的概念,至此,系統單晶片就已經不是IC設計市場上的主角,取而代之的是系統級封裝(System in Package, SiP)、PoP(Package on Package)等所謂的三維(3D)堆疊系統。

當摩爾定律遇到3D IC

就如同前面所說的,摩爾定律不只是技術問題,它是半導體經濟問題,所以牽扯到太多的供應鏈、公司,乃至國家的穩定問題,所以設備或是材料商都會投入更多的資源來開發更多的技術,讓這個推動能力可以繼續存在。

由於傳統的193奈米光源早已經大於關鍵尺寸(Critical Dimension, CD),也就是超過物理極限,若是要繼續微縮,就必須要在光源、曝光技巧或光罩準備上做出努力。表3是設備商KLA-Tencor針對各個產品若是要達到可以延續摩爾定律,該公司所認為應有的搭配技術。

可以看出,在2010年,動態隨機存取記憶體(DRAM)產品雖然進入了3x奈米的製程,也最早引進3D IC的必備技術--矽穿孔(Through Silicon Via, TSV)。這是因為DRAM要求的容量太大,雖然微顯影技術可以做出尺寸,但面積太大導致良率下降,所以不得不使用TSV。

相對地,NAND因為本身儲存單元可以朝著立體化進行,也就是由浮動閘極(FG)進入到電荷捕捉記憶體(Charge Trapping Memory, CTM),所以可讓摩爾定律在不依賴TSV的情形下繼續存在。

在微處理器(MPU)產品的部分,因為可以認定是邏輯含記憶體的產品,所以微影製程的微縮可以撐得比較久一點。但是,到了22奈米,除了加上高介電質金屬閘極(HKMG)外,TSV也是必備的。單純的邏輯製程,也是在22奈米必須要用到TSV。總之,到15奈米左右,TSV應該是摩爾定律維持有效必備的技術之一。

|

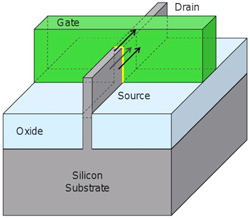

資料來源:英特爾

圖3 英特爾的22奈米3D電晶體 |

2011年,英特爾為了延續摩爾定律,推出所謂的三閘極(Tri-gate)的3D電晶體(圖3)。對於這個製程,英特爾早就在2002年就已經發展,意味著將完全擺脫二維(2D)平面電晶體結構,這是因為閘極有三個面。但是,這個三個面的電晶體結構並不是3D IC,頂多只是3D電晶體。

很清楚地,摩爾定律雖然受到挑戰,但畢竟它是經濟層面的問題。當人類溫飽問題已經解決,過去的電子科技也不符合需求,那麼人類的需求更不會只是在摩爾定律,而是希望擁有更多摩爾定律,或者希望超越摩爾定律,要達到這個目標,就必須要發展3D IC的技術。

其實,3D IC在90年代被稱之為VIC(Vertically Integrated Circuits),或CUBIC(Cumulatively Bonded IC),或是所謂的3D Integration。從堆疊這個名詞來看,至少可以有下列不同的堆疊方式:

| ‧ |

|

| |

電晶體堆疊(Transistor Stacking)是將電晶體做成非平面(Non-planar)的電晶體。例如平面式雙閘極電晶體(Planar Double Gate Transistors)、Flexfet、鰭式場效電晶體(FinFET)、英特爾的三閘極電晶體及Gate-all-around(GAA)FET等等。 |

| ‧ |

|

| |

封裝層次的堆疊(Package Stacking)將不同形式的封裝,再以另一個封裝堆疊起來,例如系統封裝、SoP(System on Package)、PiP(Package in Package)、SCSP(Stacked Chip Scale Package)、CoC(Chip on Chip)、內藏元件(Embedded Device)等。 |

| ‧ |

|

| |

裸晶堆疊/晶圓片堆疊(Die Stacking/Wafer Stacking)將不同的晶粒或晶圓片針對Die-to-Die、Die-to-Wafer或Wafer-to-Wafer用鍵合(Bonding)的方式接合。這其中又包含了一種稱之為無接觸型3D IC(Contactless 3D IC)。 |

利用晶片層的堆疊來減輕IC中擁擠的程度,早就不是什麼新的構想,這種想法在業界至少已經有30年的時間。但是,過去一直可以在平面製程或設計工具上努力,達到摩爾定律的需求。

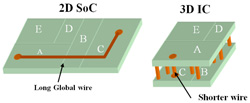

|

| 圖4 二維系統單晶片與3D IC架構示意 |

目前,逐漸有人考慮到利用第三維來創造3D IC。如圖4所示,也就是透過高度的堆疊來整合不同的IC。不同於3D封裝裡面的元件是離散的,都是在元件的周邊利用打線(Bonding Wire)相接,3D IC則是一個獨立的IC,透過垂直與水平整合來大量提高整合密度。

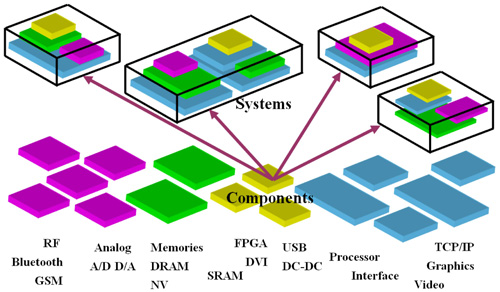

除此之外,3D IC因為多了一度的自由空間,因此,不管是在電路的合成階段,或在系統整合階段,3D IC可以讓電路的呈現更為彈性,可以讓矽智財(IP)的再使用性更大為提升(圖5)。

|

| 圖5 利用3D IC的矽智財再利用概念 |

透過TSV技術讓摩爾定律持續有效,也就是讓摩爾經濟可以持續創造價值,是未來幾年內會看到的。這樣的結合讓更多的創意產品可以產生,不管是智慧型手機或平板電腦都可以添加更多的功能。

(本文作者為南台科技大學電子系教授)