現階段無論是消費性電子或工業用儀器,甚至醫療電子,對於影像資料的傳輸需求越來越高,也讓影像傳輸介面得逐漸提升其傳輸速度,各種高速傳輸介面中,DisplayPort由VESA提出,為順利讓廠商利用FPGA完成DisplayPort設計架構,各式DisplayPort應用設計說明書,將不可或缺。

在2010年1月舉辦的美國國際消費性電子展(Consumer Electronics Show, CES)上,數家業界主要的平板電視及顯示技術公司紛紛宣布推出高畫質(HD)三維(3D)電視和令人驚豔的4K×2K液晶顯示器(LCD),進而將用戶家中、車內或行動設備上的電視、顯示器及其他電子設備之間須要交換的資料傳輸量,顯著提升至前所未有的水準。在這些最新的電視上,體育迷們可歡欣鼓舞地體驗到眾多優異效能,如176度的超廣視界、1,200︰1的超高對比度及450nit的亮度,即使連最陰暗的洞穴也可一目了然。

不過,對於開發這些電視或連接至這些電視的電子產品設計工程師來說,所有這些最新特性都意味著需要非常高的頻寬。如一部具備八百萬畫素的四聲道4K×2K高畫質電視(可為家庭提供數位電影院效果)所需頻寬是當前頂級電視和顯示器在理想工作狀態下的四倍,這意味著在機上盒與高畫質電視之間存在巨大的資料傳輸量。

這種對更高頻寬的需求並不單單來自消費性產品市場,也可能為了滿足核磁共振造影掃描儀(MRI)和電腦斷層(CT)掃描、命令與控制、雛菊鏈顯示、電子布告牌與DNA 3D表現、航空器、天氣及人體構造等眾多應用領域的顯示需要,此外,廣播設備、數位顯示、科研及醫療市場也在不斷加大對頻寬的要求。

傳輸資料龐大驅動 DisplayPort應運而生

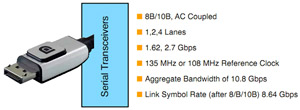

為在控制成本的同時還能有助於滿足這種頻寬需求,2007年視訊電子標準協會(Video Electronics Standards Association, VESA)針對市場推出DisplayPort,隨後並積極與合作夥伴展開合作,為DisplayPort進行最佳化。如今,VESA DisplayPort 1.1a已能在單條線纜內支援多達四個通道且每通道最高達2.7Gbit/s的資料傳輸率,而DisplayPort 1.2又將可支援的資料傳輸率加倍,達到5.4Gbit/s,足以在單顯示器應用中支援3,840×2,400畫素(60Hz),或四台顯示器應用中的1,920×1,200畫素,或2,560×1,600畫素的3D顯示(120Hz)。DisplayPort可同時支援兩種嵌入式顯示,如筆記型電腦的顯示器,以及視訊「來源」設備,如機上盒(STB)、DVD播放機、個人電腦(PC)繪圖卡及筆記型電腦和獨立顯示設備,如高畫質多媒體介面(HDMI)與DisplayPort標準文檔中所稱的「接收端」設備間的盒對盒連接(Box-to-box Connection)。

|

| 圖1 TED Spartan-6 FPGA消費性視訊套件 |

目前有些晶片製造商已針對上述應用推出現成的標準發送器和接收機,而賽靈思(Xilinx)則推出LogiCORE DisplayPort v1.1的靈活可編程VESA DisplayPort v.1.1a解決方案,v1.2將在IDS 12.1中配套提供,此IP可隨時提供給客戶,但在用戶展開設計前,建議先了解與該標準部分關鍵功能有關的其他背景資訊,如Policy Maker及如何使用廠商將推出的應用指南--「使用MicroBlaze嵌入式系統建置DisplayPort Source Policy Maker Controller System Reference Design」,並在Tokyo Electron Devices(TED)提供的Spartan-6消費性視訊套件(圖1)上完成建置工作。

Policy Maker為關鍵性差異

對於顯示市場來說,DisplayPort協定代表連接技術的重大變革。這次轉型意義不亞於在英特爾(Intel)主導的個人電腦市場上,從並行PCI匯流排升級至串列PCI Express(PCIe)。在顯示市場上,VESA透過DisplayPort引領從VGA、DVI及HDMI等協定成功升級至高速串列收發器、以封包為基礎的層架構協議。與並行協定不同的是,串列分組協定在達成和維持連接或鏈路方面要多一層複雜性,在VESA DisplayPort 1.1a規範中,控制功能被劃分為鏈結決策者(Link Policy Maker)和串流決策者(Stream Policy Maker)。Link Policy Maker可管理鏈路,並負責保持鏈路同步。其任務包括發現鏈路、對鏈路進行初始化和維護;Stream Policy Maker可管理傳輸初始化,並透過底層硬體對行動序列施加控制維護同步串流。

Policy Maker的上述要素須根據特定的建置決定,且可在作業系統、軟體驅動程式、韌體或FPGA邏輯中進行組態。為簡化使用,許多商用DisplayPort IC針對設計人員將Link和Stream Policy Maker隱藏起來,若用戶的顯示要求恰與套裝的DisplayPort特殊應用標準產品(ASSP)相匹配,則其價格和易用性的確毋須爭辯,但是,想要讓產品在競爭中脫穎而出的設計人員則傾向於採用FPGA。

廠商推出的DisplayPort Source Policy Maker Controller System Reference Design應用手冊採用MicroBlaze嵌入式系統建置,以及商用套裝DisplayPort晶片類似的功能,且具備可進行原始碼定製的額外優勢。透過使用Source Policy Maker Controller System Reference Design的應用手冊,用戶不必對Policy Maker進行詳細了解即可順利啟動設計工作,僅須簡單地將範例設計連接起來。

除上述原始碼設計外,DisplayPort的傳輸(Tx)或源端核心也配套提供用於達成有限狀態機器(FSM)控制器的額外範例設計。DisplayPort Tx FSM控制器範例設計(其頂級檔案名為dport_tx_fsm_cntrl)配套提供DisplayPort LogiCORE源端設計範例。該款簡單的概念驗證設計內含以RTL為基礎的有限狀態機器,以建置可展示正確啟動流程的簡單Policy Maker。與其他範例設計相比,dport_tx_fsm_cntrl設計範例的優勢在於可顯著縮短模擬時間。 Source Policy Maker Controller System Reference Design採用日前推出的MicroBlaze嵌入式系統XAPP,其頂級ISE項目名稱為dport_source_ref_design.xise。該設計使用戶能夠根據自己的需要對Source Policy Maker Controller的原始碼進行修改。此外,其還能夠與DisplayPort LogicCORE v1.2(IDS 12.1)版和Spartan-6 TED消費性視訊套件共同運作。上述兩種範例設計都包含可達成核心設置及鏈路和流維護的基本流程。

透過原始碼完成來源端設計

來源端、接收端/視訊規範都會採用Policy Maker,但在DisplayPort LogiCORE中,FPGA廠商對其進行差別建置。與來源(發送)端的Policy Maker功能相比,接收端的Policy Maker功能要簡單得多。廠商在LogiCORE內建置大部分接收端Policy Maker功能,而基於RTL的接收端控制器可提供剩餘部分的功能,由於來源端Policy Maker的功能複雜得多,因而可採用原始碼參考設計的方式提供。

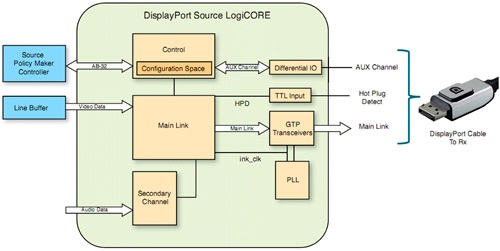

來源端Policy Maker使設計人員能最大限度地提高功能靈活性與建置靈活性。頂級範例設計包含核心的兩個高階組件範例,包括XAPP使用MicroBlaze嵌入式系統建置DisplayPort Source Policy Maker Controller System Reference Design,以及DisplayPort核心源端(發送)設計。廠商將核心的建置分成原子鏈路功能,分別稱為主鏈路(Main Link)、二級通道(Secondary Channel)及AUX通道協議。主鏈路可達成主視訊流的交付;二級通道可在消隱期內將音訊資訊的交付整合到主鏈路中。FPGA廠商將在未來發布的核心中提供二級通道,同時,AUX通道可為接收端通訊通道建立專用來源端(圖2)。

|

| 圖2 DisplayPort Source Policy Maker Controller System Reference Design與LogiCORE來源端高階結構圖 |

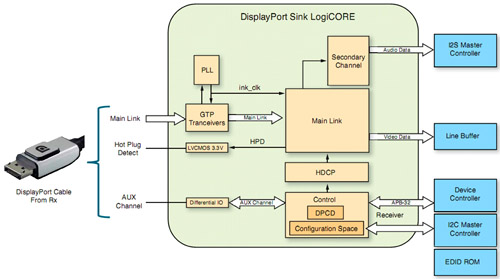

廠商為用戶資料介面新增線路暫存器,使用戶能在FPGA中便捷建置範例設計。圖3中接收端的Policy Maker與Device Controller都是內核生成器(CORE Generator)所提供接收端設計範例的組成部分。

處理器發揮核心作用

廠商推出的Source Policy Maker Controller可與核心配合使用,其功能在很大程度上和ASSP DisplayPort來源端設備相同,建議使用MicroBlaze嵌入式或外部處理器正確初始化和維持該鏈路。XAPP包含的Policy Maker Reference Design預組態版本在FPGA內的MicroBlaze處理器中建置,可幫助用戶立刻將設計方案轉換成硬體,且正式供貨時的參考設計將包含設計人員可以修改的原始碼。

Source Policy Maker Controller設計的邏輯部分位於MicroBlaze處理器上,並使用I2C命令來控制鏈路、資料流程及組態空間。該C語言代碼可建置Policy Maker的指令控制、頂級示例檔案及嵌入式開發套件(EDK)。同時廠商還提供軟體發展套件(SDK)專案檔,可為設計人員最大限度地提高建置靈活性,還可為使用現有控制平台處理器的應用提供C語言原始碼。設計人員可將該原始碼添加至FPGA內外的現有控制軟體中,根據執照協定,只要代碼能夠同核心配合使用,控制器即可在FPGA外部建置,即在外部處理器中建置。

設計人員可以使用支援Platform Studio(EDK)的嵌 入式硬體設計套件或具有SDK的嵌入式軟體設計套件,對XAPP設計進行修改,通常情況下,FPGA設計人員使用EDK,而軟體發展人員則使用SDK。EDK流會產生一個中間網路檔(NGC),可在建置設計前,將其整合在頂級ISE專案中,NGC檔包含構成區塊隨機存取記憶體(BRAM)初始化一部分的MicroBlaze代碼。

若用戶修改過軟體,EDK流通常會占用較長時間,不過,用戶一旦產生網路列表,就不再需要EDK或SDK;SDK流可修改FPGA位元串流,因此僅須更新BRAM中的MicroBlaze代碼內容,該SDK流能為軟體修改提供更快轉換時間,但在這種情況下,用戶每產生一個位元串流就須使用一次SDK,有關本專題的XAPP白皮書包括如何使用FPGA嵌入式軟體發展套件去運作該設計的詳盡說明。此外,用戶可將該設計與從TED Spartan-6 FPGA消費性視訊套件中下載的完整版或評估版DisplayPort LogiCORE及DisplayPort FPGA Mezzanine Card卡配合使用。

來源端的Policy Maker內含一個狀態機器,可透過AMBA周邊設備匯流排(APB)埠或採用AMBA至PLB橋(Bridge)的32位元PLBv46匯流排連接至處理器介面。廠商在BRAM中儲存用戶可修改的指令集。用來調訓(Train)該鏈路的C++代碼不但採用GNU C++編譯器編譯,並且還在採用EDK Platform Studio處理器設計套件的FPGA內部建置軟式MicroBlaze處理器上,進行全面測試。參考設計包含完整的SDK專案。範例測試台可將一個135MHz的時脈連接至VID時脈,並將一個100MHz的時脈連接至APB時脈,廠商會對所有輸入是否連接正確進行檢查。此外,頂級模組還提供重新設定功能。

DisplayPort擴展顯示識別

DisplayPort一個特別重要特性是,能透過VESA的延伸顯示能力識別(EDID)結構與不同的設備進行介面相連。EDID並不是什麼新事物,實際上,多年以來設計人員一直在使用各種視訊介面讀取EDID的接收端設備參數,從而與設備進行介面連接。不過這些早期的EDID及相關介面技術通常不包含精密的可組態通訊通道,如今借助DisplayPort,VESA可為系統增加智慧性,不但能在來源端如機上盒、DVD播放器或個人電腦繪圖卡與接收端設備如顯示監控器間進行功能協調,而且還可最佳化通訊參數。DisplayPort v1.1a可協調變數包括通道數量1、2或4、每通道資料傳輸速率1.62Gbit/s或2.7Gbit/s、電壓擺幅0.2、0.6、0.8、1.2伏特(V)、四個級別的通道預增強及鏈路時脈向下擴散。

由CORE Generator產生,並與LogiCORE一起提供的接收接收端範例設計可提供範例EDID(圖3),以便滿足EDID來源端設備的讀取需求,確保用戶的最佳視覺體驗。接收端範例設計在FPGA內部的BRAM中建置EDID資料結構,DisplayPort的原始碼可透過AUX通道達成I2C協議。圖3和圖4顯示連接至來源端的DisplayPort接收端框架圖,接收端的Link與Stream Policy Maker屬於接收端核心的組成部分,不過來源端的Link Policy Maker具有更高複雜性,將作為原始碼隨參考設計提供。EDID透過I2C介面與接受接收端進行介面連接。

|

| 圖3 DisplayPort接收端高階框架圖 |

I2C協定非常適合針對EDID資料結構的連接,並常常用於此種類型的應用。I2C控制器負責定位與管理在EDID中發現的資料,並透過串列介面與I2C介面協定(透過AUX通道)將資料傳輸至接收端核心。在工作模式下,用戶毋須知曉EDID是否正被訪問,可透過檢測I2C匯流排來監控唯讀儲存記憶體(ROM)的內容。在調試模式下,用戶能修改I2C控制器,覆蓋EDID ROM提供的3位元內容,而I2C提供控制訊號,在與適當的集極開路輸出相連時,可提供I2C主介面。

|

| 圖4 VESA DisplayPort v1.1a主鏈路 |

接收端內含名為DisplayPort組態資料(DPCD)的資料結構,可以儲存組態資料並作為接收端與來源端都可讀寫的通訊郵箱使用。來源端一般使用跨AUX通道的DPCD內容,可參考圖3、4。

鏈路調訓最佳化DisplayPort鏈路速度

在DisplayPort鏈路上建立通訊的過程稱為「鏈路調訓」。在鏈路調訓過程中,核心在通訊啟動時,會在降低錯誤的同時,最佳化鏈路速度與功耗,若在資料傳輸中出現問題,核心將自動重複鏈路調訓,以適應不斷變化的條件。來源端與接收端資訊封包間的通訊透過雙向半雙工1Mbit/s AUX通道進行,視訊與音訊資料透過主鏈路通道1、2或4進行傳輸,其是從來源端到接收端的高速Gigabit級收發器通道。

核心的鏈路調訓工作分兩步執行,包括時脈恢復、通道均衡、符號鎖定(Symbol Lock)與通道間對準。步驟一,接收器的PLL鎖定至進入的訊號,並恢復鏈路時脈,步驟二,系統對通道均衡與通道間對準進行最佳化。以下是源端與接收端的Policy Makers的典型工作順序:

首先,Tx Link Policy Maker可監控熱拔插檢測情況,若檢測到有熱拔插,則向Stream Source Policy Maker發送通知。Stream Source Policy Maker透過AUC通道讀取接收端EDID。再者,Tx Link Policy Maker透過AUX通道讀取來自接收端的DisplayPort組態資料。根據來源端與接收端的功能組態情況,可為接收端DPCD的鏈路組態欄位編寫組態參數,並透過寫入到接收端DPCD的「TRAINING_PATTERN_SET」位元組啟動鏈路調訓,隨即對調訓模式發送進行初始化。

第三為Tx Link Policy Maker根據來自Rx Link Policy Maker的回饋,透過調節電壓擺幅及在必要時調節位元率,控制時脈恢復順序,一旦核心完成時脈恢復,鏈路調訓就進入通道均衡階段,在該階段,若調用Rx Link Policy Maker,即對預增強進行調節。此外,接收器還將在本階段完成符號鎖定與通道間的對準。最後,一旦核心透過鏈路調訓,即系統完成位元鎖定與符號鎖定,就會在DPCD中予以提示。Tx Link Policy Maker可向Tx Stream Policy Maker報告調訓狀況,以在進行串流屬性資料傳輸的同時達成同步串流。

Policy Maker附加功能多元

除參與鏈路調訓外,Tx Link Policy Maker還可利用來自接收器的IRQ HPD訊號監控接收端事件通知,並可檢查DPCD的鏈路狀態欄位,了解中斷的原因。若Tx Link Policy Maker檢測到鏈路失去鎖定,就須重新調訓鏈路;若接收器調用,還可重新組態鏈路,增加或減少主鏈路通道數。

此外,Link Policy Maker還可決定多個AUX請求事物處理的順序,因每個事物處理將結束於另一個事物處理開始前。由於接收端的答覆可是NACK或DEFER,Policy Maker必須決定針對這兩種情況的後續工作,AUX事物處理僅限於16位元組的資料,因此Policy Maker必須將較大的事務處理分成多個不超過16位元組的事物處理。

由於DisplayPort能協商和最佳化鏈路設置,因而能在不斷變動條件下達成最佳結果。Link與Stream Policy Maker是進行流程協調的控制功能,能達成現代高速視訊與音訊的傳輸。廠商經過精心設計的Source Policy Maker Controller系統參考設計採用MicroBlaze嵌入式系統,可幫助工程師充分發揮這些全新功能的所有優勢,以針對市場推出功能豐富的顯示產品。DisplayPort LogiCORE可提供高靈活的來源端與接收端解決方案,具有可下載到TED Spartan-6消費性視訊套件中的範例EDID及原始碼,並免費提供該IP的評估版本。

(本文作者依序為賽靈思資深產品行銷經理、Quantum Data市場行銷經理)