過去幾年來,現場可編程閘陣列(FPGA)組件的結構發生很大的變化。這些變化,從隨機存取記憶體(RAM)和數位訊號處理器(DSP)等硬體模組開始,現在FPGA還整合收發器和硬核IP,如乙太網和PCI Express(PCIe)。

有這些新的功能模組,FPGA設計人員現在可以實現非常複雜的設計。然而,有時這些複雜的設計會將目標FPGA組件的成本、功耗和性能規範逼近極限。

舉例來說,在消費電子/行動通訊應用中,低功耗和低成本是很重要的指標,設計師試圖滿足這些具有挑戰性的功耗和成本目標時,可能須要嘗試設置不同的工具,如花更多精力進行布局或布線,提高性能或減少電路板面積。有時可能須改變設計,如選擇內嵌RAM模組替代分散式RAM,以提高性能。甚至更改設計結構,如選擇並行的協定替代串列協定。

然而,通常這些設計方法都須按順序依次進行,也因此增加整體編譯時間,對工作進度造成重大的影響。一直以來,設計師,尤其是消費電子產品設計工程師,在時間進度上承受許多壓力,要擊敗競爭對手,就必須將自己的產品率先推向市場。因此,設計師需要在最短的時間內完成FPGA設計,同時滿足那些極具挑戰性的設計規範。

為在最短時間內滿足設計規範要求,設計人員會希望花費最少的時間,利用FPGA設計軟體探測多種設計的導入作業或更改設計結構。

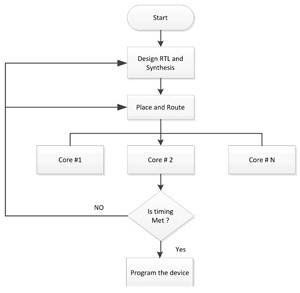

傳統FPGA設計流程耗時

|

| 圖1 設定管理器架構 |

採用傳統的設計流程,FPGA設計者往往很難在不影響開發進度和產品發布的時間狀況下,滿足目標設計的規範要求。主要原因是,傳統的設計流程從根本上來看是按照順序進行的,每次使用者變更設計後,就須要重新進行編譯以評估變化造成的影響。這個過程將會反覆進行,直到滿足設計規範為止。這樣一連串、反覆進行的FPGA設計流程可能延遲進度,對於提高競爭力而言,這是不可被接受的。在這樣的情況下,需要有一個解決方案能夠減少整個設計流程中的編譯時間。

FPGA設計軟體擁有一個叫做「設定管理器」的工具,幫助設計者在面對工作進度壓力的情況下實現他們的目標(或設計規格)。這個工具允許設計師選擇優化的設定,例如在整個設計中進行時序重整或控制,並保存所有資料結果,如在不同的設定中所做的操作、保存所有操作的結果,或是選擇性地保存最佳的運行結果。

|

| 圖2 並行處理仍須花費較長設計時間 |

設計師還可設定一些更高階的目標,如「低功耗設計」或「縮小設計尺寸」,讓工具自動選擇對應的設定,對整個設計進行探測(圖1)。雖然設定管理器具有更先進的功能滿足設計目標,但並不能完全解決工作進度的壓力,因為任何設計變動仍會導致使用者須要再次啟動該工具,並經歷一個漫長的編譯過程。

利用現在的多核中央處理器(CPU)電腦架構是另一個創新方法。FPGA設計軟體雖然可以使用任意數量的CPU來減少編譯時間,但是多更改一次設計,仍然須多做一次編譯,即使縮短一次設計變更的編譯時間,整體的時間花費還是會大幅增加(圖2)。

|

| 圖3 增量設計架構 |

FPGA設計軟體新增的另一特性是參考特定應用積體電路(ASIC)的設計方法,並引入增量(Incremental)設計流程(圖3)。在此流程中,使用者可以邏輯層次為基礎,將設計分塊,從而減少執行時間並保持時序效果。使用這種技術,使用者可以在邏輯層次中分出可能須進行設計變更和重新編譯的地方。因此,當在進行局部變更時,就不會影響整個設計。

Incremental設計流程可縮短整體的編譯時間,同時保留其餘設計的性能。這是往正確方向前進的重要一步;然而,這種做法仍然無法改變設計流程須依照順序進行的事實。用戶在某一特定時間內只能導入一個有效的設計,還須分別等待兩次編譯執行結束後,才能得到比較的結果。

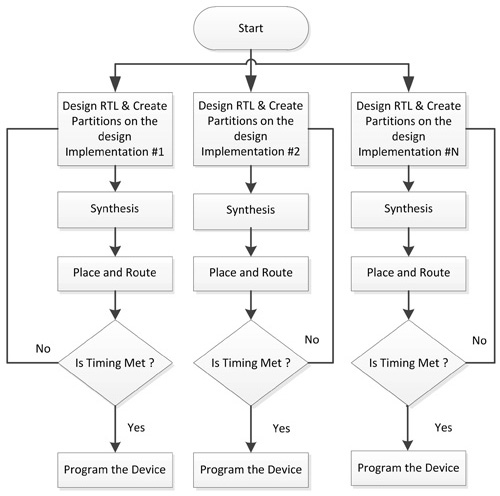

改用並行作業 縮減編譯時間

在FPGA設計流程中,需要的是根本上的改變,讓使用者可並行編譯多個導入作業,並用一次編譯時間就能比較兩種導入作業的結果,而不須要按照順序進行兩次編譯,並且快速接受或拒絕變更,盡可能地減少對工作進度造成的影響。

舉一個設計實例來說明,假設使用者要更改導入的設計作業,使用分散式RAM代替內嵌RAM塊來節省內嵌RAM塊的使用。這樣以DSP為中心的設計,須內嵌RAM塊儲存操作係數。內嵌RAM是這類操作的理想選擇,因為比分散式RAM提供更高的傳輸量。

如果使用者要做出這樣的改變,就須要連續進行兩次操作,才能知道這一重大設計變更的影響。然而,透過並行運行多個導入作業的方式,用戶可以減少執行時間,只需要一次完整的運行,就能迅速地評估設計變更造成的影響。

另一個展現並行運行價值的例子是,當用戶希望更改設計架構時,一個典型的例子是在高速行動電子應用中,為進行資料管理,須要將串列改為並行作業,這種改變對這類設計而言是很常見的。採用傳統的設計流程,須要兩次編譯來評估變化的影響;但在可實現並行設計的設計流程中,僅需一次運行即可獲得結果,可進而節省一次執行時間。

對於FPGA設計流程進行這樣的改變後,用戶可以加快他們的設計進度,或者至少可以減緩進度帶來的壓力並提高生產力。

萊迪思(Lattice)Diamond FPGA設計軟體是實現當代設計流程的一個例子,專門針對低功耗和成本敏感的應用進行優化,如MachXO/XO2和LatticeECP組件系列。

加快設計探測 優化FPGA

Diamond FPGA軟體包含一個稱為運行管理器(Run Manager)的功能,對於一個設計可以產生兩個RTL檔作為兩種導入作業,並對這兩個導入作業進行並行運行。與傳統的設計流程相比,使用運行管理器,用戶可縮短編譯時間,並快速比較兩種導入作業的結果。

若對結果滿意,用戶還可透過選擇較佳的導入結果,立即對組件進行程式設計,如果用戶對兩個導入結果都不滿意,則可再建立新的導入作業,再次運行來比較結果。使用者一次可運行的導入作業數量並沒有限制(圖4)。

|

| 圖4 運行管理器架構圖 |

執行時間大幅縮短

考慮兩個在兩款不同組件上使用運行管理器的例子。例一為使用LatticeECP3-95EA1156-8 FPGA以DSP為中心的設計,在此例子中,有兩個導入作業透過四核、4GB記憶體、Windows作業系統的機器來執行。兩個導入作業的連續編譯時間為13分鐘,而這兩個導入作業使用運行管理器並行編譯的時間為8分鐘,總體來說減少近40%的編譯時間。

例二為使用LatticeECP3-35EA484-6 FPGA的通訊量管理器設計。這個例子同樣使用四核、4GB記憶體、Windows作業系統的機器來運行兩個導入作業。兩個導入作業的連續編譯時間近3個小時,而使用運行管理器進行並行編譯的時間為1.5小時,節省50%的編譯時間。

在瞬息萬變的應用市場中,滿足產品上市時間是重要的關鍵,且設計師們常常面臨著須要更快交付設計的壓力。因此,設計師們希望FPGA設計軟體工具能盡可能減少編譯時間。運行管理可為設計師提供競爭優勢,充分利用電腦體系結構,以及類似Lattice Diamond中的獨特功能,同一設計的多個導入作業,以及對應的RTL檔可以幫助設計師迅速比較結果並提高生產力。

(本文作者為萊迪思資深產品行銷經理)