縱觀世界一流的製造商推出的最新一代智慧型手機,可以很容易得出結論:設計工程師正透過不斷創新來實現更高層次的智慧化系統。目前有兩個因素正引領著當今的創新趨勢,其一是低成本感測器的大量湧現,微機電系統(MEMS)製造商正幫助市場降低感測器的成本和尺寸,引領市場顯著的進步。其二是智慧型手機設計師正在開發新的「環境感知」子系統,使得行動設備能夠在沒有使用者干預的情況下進行預先且有利於指令的決策。

這場革新始於領先的手機製造商開始使用嵌入式接近感測器來延長電池壽命,以及使用加速度計、陀螺儀和磁力計支援基於定位的服務。而現今基於感測器的環境感知子系統的功能與之前相比已經大大提升,在許多領域都能模擬人類對所處的環境進行分析。

舉例來說,高解析圖像感測器和環境光感測器在環境發生改變時能夠提升圖像清晰度並改善顯示幕的顯示效果。化學分析器能夠模擬人類的嗅覺。壓力、溫度、化學和紅外線感測器則能夠監測智慧型手機使用者的健康狀況並評估健康風險。更多基於感測器的「環境感知」應用正逐漸實現中。在不遠的將來,當智慧型手機擁有心臟監測儀和汗水偵測器來追蹤用戶的健康狀況、興奮程度和情緒時,千萬不要感到驚訝。

感測器基本要求 快速且低功耗

為了充分利用所有感測器資料並且優化決策過程,現今的行動系統必須以最快的速度整合並分析多種資料流程。感測器收集資料並處理為可用資訊的速度越快,系統對於即時環境狀況做出的反應就更精確。不過,由於基於感測器的「環境感知」子系統必須能常時運作,因此對系統功耗的要求也十分驚人。由此可見,從系統功耗上來看,必須最高效能地處理這些指令。

有三種設計架構可供行動系統設計師選擇來解決這個問題。首先,可以使用系統核心應用處理器來管理感測器資料。或者,使用獨立的微控制器(MCU)進行管理,進而分擔處理器的指令。

再者,也可以採用一個超低密度(ULD)現場可編程設計閘陣列(FPGA)建構一個整合的感測器中心,以同樣的方式協助應用處理器。

每種方案都有其優勢與不足。設計工程師將每個感測器直接連接至應用處理器,採用經過驗證的架構好好地利用現有系統的資源。但是由於感測器的數量持續增加,設計工程師不可避免地會遇到通用輸入輸出(GPIO)資源的瓶頸。長期受此約束,設計工程師將無法實現許多重要的新功能。同時,所有MCU都存在介面限制,影響到設計彈性的問題。每一個感測器都會帶來特定的介面要求。有些指定工業標準介面,有些又需要專屬的解決方案。只使用單一應用處理器或MCU來滿足今後所有的感測器介面需求將大大增加設計複雜性,甚至延長產品開發週期。

最嚴重的問題是,基於典型的中斷驅動應用處理器上的多感測器架構,帶來了更高的功耗需求,特別是考慮到現有環境感知感測器子系統的常時運作要求。越來越多的感測器連續收集時間敏感的資料,迫使應用處理器須運行更長時間,這在系統功耗預算已經十分吃緊的行動上施加更多的需求。

在許多新興的常時運作、環境感知應用中,採用為行動應用特別優化的超低密度(ULD)FPGA無疑是更好的選擇。不同於傳統的大尺寸且昂貴的FPGA,這種新的低門數元件採用高度緊密的晶片級封裝(CSP)。該類元件提供支援感測器管理和預處理功能所需的邏輯資源,並可大批量生產以實現規模效益。

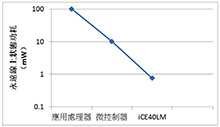

對於這些必須常時運作的環境感知應用,此種設計方案特別受到系統工程師的青睞,因為該方案可以減少功耗相對較大的中斷驅動應用處理器的執行時間。設計工程師可使用ULD FPGA以遠低於傳統應用處理器和MCU的時脈速率,同時並且即時地收集多個感測器的資料。這些IC的功耗小於1毫瓦(mW),相比傳統方案功耗大大地降低,並且以零延遲收集每個感測器的資料,針對不斷變化的環境狀況提供更精確的系統回應。同時,該方案可進一步延長應用處理器處於休眠模式的時間,如果有需要的話,也支援週期性地喚醒並可在低功耗狀態下工作。這個方案將講求時效的感測器功能交給ULD FPGA,改善了整體功耗及感測器系統精度(圖1)。

|

| 圖1 三種不同的感測器管理中心的相對應功耗 |

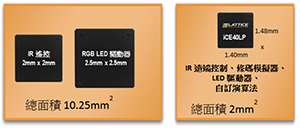

此外,由於行動設備系統中的感測器數量持續增長,基於ULD FPGA的解決方案在設計尺寸方面的優勢正變得越來越有吸引力。以下描述的紅外線(IR)子系統是一個絕佳的佐證。左邊的獨立的解決方案結合了2毫米(mm)×2毫米大小的IR遠端控制IC和一個2.5毫米×2.5毫米大小的RGB發光二極體(LED)驅動器。該解決方案總共需要10.25平方毫米(mm2)的面積。設計工程師也可以使用一塊超低密度的iCE40LP FPGA來實現相同功能的子系統,只需1.40毫米×1.48毫米(大約2平方毫米)的面積。可編程設計的解決方案透過結合IR遠端控制模組、條碼模擬器、LED驅動和自訂演算法提供了更多的功能,減少了大約80%的電路板面積(圖2)。

|

| 圖2 分立元件與可程式設計的IR子系統佔用面積比較 |

處理器與ULD FPGA功耗比較

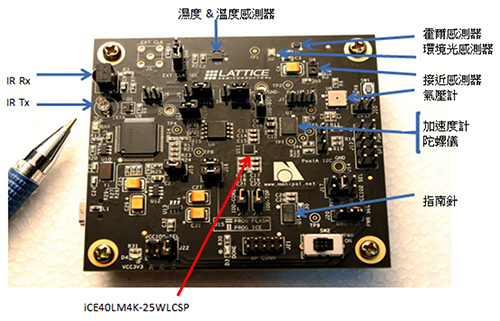

為了測量和量化功耗差異,最近萊迪思(Lattice)的工程師使用iCE40LM 4K ULD FPGA搭建一個計步器感測器管理演示系統。該演示系統包含帶有一塊智慧型手機顯示幕的高通(Qualcomm)驍龍(Snapdragon)評估板和軟體開發套件(SDK)。為了呈現一個多感測器、電池供電的行動應用,演示系統加入了由萊迪思開發的感測器子卡。

|

| 圖3 作為演示系統的一部分,這塊高度整合的子卡擁有多達十個感測器以及一塊iCE40LM 4K ULD FPGA。 |

圖3展示緊湊、高度整合的子卡。電路板上靠近中心位置的是採用小尺寸25WLCSP封裝的iCE40LM 4K ULD FPGA。該FPGA擁有4K邏輯門數、多個嵌入式IP硬核,包括兩個SPI主/從、兩個I2C主/從、一個PLL、一個kHz工作頻率的低功耗選通訊號發生器以及一個MHz工作頻率的高頻選通訊號發生器。該FPGA同時帶有RGB/LED驅動器。正如圖3所展示的緊湊型子卡,其擁有許多感測器,包括濕度、溫度、霍爾感測器(Hall Effect)、環境光和接近感測器,以及氣壓計、加速度計、陀螺儀、指南針、IR接收器和發送器。

|

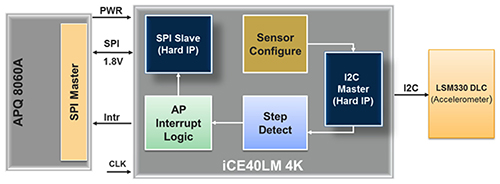

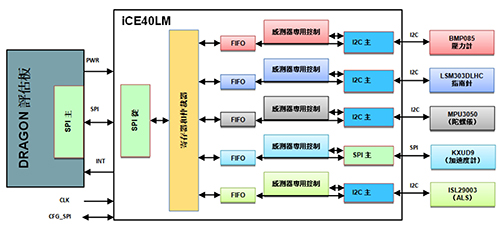

| 圖4 使用iCE40LM ULD FPGA的計步器應用 |

為了簡化iCE40LM的感測器管理功能的演示,工程師選了一個使用單個感測器LSM330 DLC加速度計的計步器應用來進行測試。透過圖4的方塊圖可以看到,FPGA的嵌入式IP硬核大大簡化了系統設計。LSM330 DLC加速度計透過FPGA的嵌入式I2C主控模組連接到iCE40LM。該FPGA同時包含感測器專用配置邏輯、步數偵測功能邏輯以及應用處理器中斷邏輯。該應用中這些邏輯將決定多長時間或者多少步之後FPGA將喚醒應用處理器並上傳資訊。該FPGA透過兩個嵌入式、固定功能的SPI主/從介面之一連接至應用處理器。

|

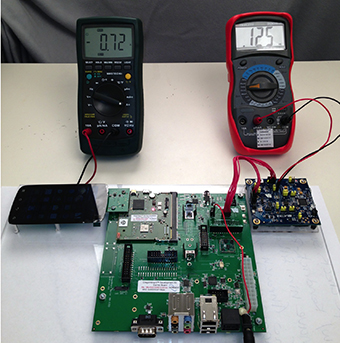

| 圖5 全系統一覽 |

圖5展示了整個系統。左側的儀表用於監測電流,追蹤整個系統的電流。當顯示幕開啟,應用處理器處於喚醒狀態時,儀表讀數為0.720安培(A),亦即720毫安培(mA)。

下一步,工程師將應用處理器設置為休眠狀態,此時系統顯示計步器讀數為0。系統電流降至0.52安培,系統功耗為160毫瓦。

IAPQ8060=720mA–520mA=200mA

PAPQ8060=200mA×0.8V=0.160W

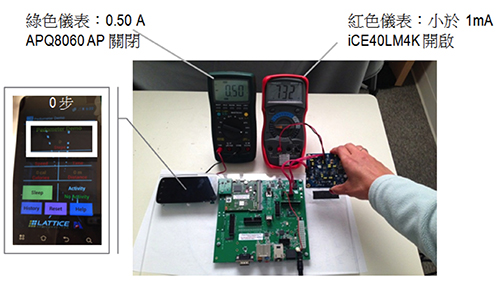

須要注意的一點是,環境感知感測器應用必須保持常時運作的狀態,所以計步器讀數為0時,右側的紅色儀表檢測到iCE40LM感測器管理器的電流為732微安培(μA),此時應用處理器處於休眠模式(圖6)。

|

| 圖6 計步器系統演示 |

為了模擬計步器監測人們走路的過程,工程師前後搖晃iCE40LM感測器子卡。iCE40LM FPGA透過I2C埠獲取加速度計收集到的資料,並透過FPGA感測器專用控制進行處理。

做為此過程的一部分,感測器管理和預處理功能分析位元流資料,評估如何解析資料、將感測器獲得的資料轉化為步數。最後,資訊將被載入到加速度計的先進先出(FIFO)為再次喚醒應用處理器和顯示幕做準備。這個過程中,右側的紅色儀表檢測到iCE40LM FPGA電流的最高讀數為737微安培。

|

| 圖7 按下喚醒中斷初始化應用處理器和系統顯示幕 |

此時工程師給系統上電,按下喚醒中斷初始化應用處理器和系統顯示幕(圖7)。

隨著系統電流上升,應用處理器被喚醒,讀取iCE40LM的FIFO,獲取加速度計記錄的步數。應用處理器透過獲取的資料計算出行動距離、卡路里消耗,並且將結果透過系統顯示幕顯示(圖8)。

|

| 圖8 加速度計收集到資料後,透過I2C埠傳送,經過加速度計感測器專用控制處理後載入到FIFO,為應用處理器喚醒和顯示結果做準備。 |

從計步器應用演示的結果可以清晰地看到,基於ULD FPGA的感測器管理子系統能夠顯著地節約功耗。在計步器演示中,iCE40LM的最大功耗為0.737毫安培×1.2伏特(V),即0.88毫瓦。可以很明顯地看到處理相同的指令時,iCE40LM大約只消耗了應用處理器功耗(160毫瓦)的一百八十分之一。考慮到環境感知感測器應用永遠線上的特性,採用基於ULD FPGA的感測器管理系統的功耗小於1毫瓦,特別是實現多感測器的應用時可明顯提升行動系統電池壽命。

此外,基於iCE40LM的感測器管理系統占用不到1.7毫米×1.7毫米的面積,節約的電路板面積相比其他設計方案對於設計師的吸引力是很大的。其次,不像中斷驅動的應用處理器或微處理器,其零延遲即時收集感測器資料的能力增強了資料完整性和系統即時性。

最後,設計工程師透過可編程設計解決方案可重新配置輸入/輸出(I/O)和協定,同時優化每個感測器FIFO、暫存器和仲裁器的大小、配置和效能,獲得其他設計方案無法提供的設計彈性。

即時反應速度 ULD FPGA優於MCU

接下來,工程師團隊將比較獨立的MCU感測器管理系統與基於ULD FPGA的系統間之效能和功耗。從在iCE40LM 4K FPGA上實現行動應用中廣泛使用的16位元精簡指令集運算器(RISC)MCU架構開始。按照常用的測試基準,16位元MCU與iCE40LM 4K FPGA都要經過I2C輪詢測試,這是「常時運作」感測器中心的常見功能。

兩個元件都設置為使用最少的邏輯,以20Hz頻率來配置和讀取加速度計的資料。在I2C輪詢功能測試中,iCE40LM 4K的功耗為0.538毫瓦。當處理計步器應用時功耗更是降低至418微瓦(μW)。在I2C輪詢測試過程中,在工作模式和低功耗模式間切換的MCU解決方案的功耗約為iCE40LM的三倍。

ULD FPGA工作功耗:

0.348μA×1.2v=418μW

這個測試同樣揭示了這兩個解決方案監測感測器資料變化的能力。基於iCE40LM4K的解決方案工作頻率低至6MHz,而I2C介面的頻率為400kHz,可以獲取50個取樣/秒的加速度計數據。16位元MCU的工作頻率高於8MHz,而I2C介面的頻率僅為110kHz,只能進行25個/秒的取樣(前者的一半)。iCE40KM4K解決方案運行時延遲極低,支援系統更好地監測感測器的變化,同時做出更快的反應。最後,近乎即時的反應速度帶來更好的使用者體驗。

觀察以上各項測試案例可知,在行動系統設計中整合各種感測器無疑只是剛剛開始。各類低成本、小尺寸的感測器將把令人興奮的環境感知應用加入行動系統中,適用於醫療、工業、科研和商業等諸多應用領域。行動系統設計師若想要實現這些新功能,首先面臨挑戰就是如何才能最高效地處理感測器收集到的資料。

(本文作者為萊迪思超低密度產品資深產品線經理)