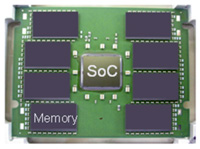

在談從手持式(Handheld)產品看系統級封裝(SiP)的必然性與必要性之前,先來看看幾個目前熱門產品使用SiP的情形。智慧型手機(Smart Phone)是手持式產品要求輕薄短小、攜帶方便的極致。處理器使用封裝層疊(PoP)封裝,連記憶體(Memory)都整合進去(圖1)。

|

| 圖1 智慧手機的處理器採用PoP封裝。 |

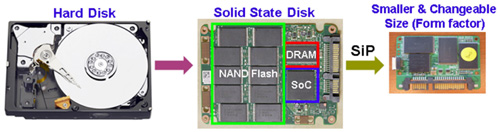

固態硬碟(Solid State Disk)較傳統硬碟小很多,又防震耐摔,適合各式隨身攜帶型電子產品(圖2)。

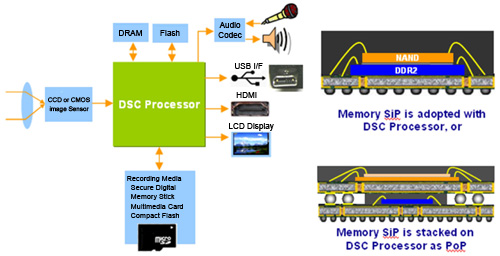

數位相機(Digital Still Camera)也需要大容量記憶體來處理影像,SiP記憶體一般都會被使用到(圖3)。

|

資料來源:英特爾、威騰

圖2 固態硬碟防震耐摔,適合隨身攜帶型電子產品。 |

|

| 圖3 數位相機需要大容量記憶體以處理影像,SiP記憶體可以派上用場。 |

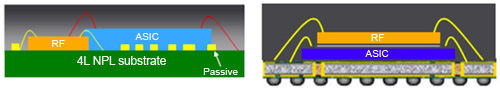

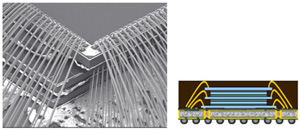

另一個例子是行動電視(Mobile TV)的射頻解調器(RF Demodulator)。異質整合(Heterogeneous Integration)是SiP的優點之一,採用堆疊(Stack)或Side-by-Side的封裝方式皆可(圖4)。

|

| 圖4 Side-by-Side(左)與Stack(右)封裝 |

|

| 圖5 高解析電視解調器使用SiP可提升系統功能。 |

以上使用SiP的例子,基本上是手持式(Handheld)的電子產品。這類應用要求輕薄短小、攜帶方便,SiP將數個獨立的IC整合在一個封裝(Package)內,微型化(Miniaturization)是其第一個可以看到的優點,因此也是上述的電子產品會採用SiP的考量點。

|

| 圖6 封裝好的IC也可用SiP Side-by-Side技術整合,除了尺寸(Form Factor)可變小,效能也可提升。 |

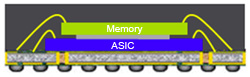

但SiP優勢並非只有微型化,即使產品本身體積相對較大,微型化的需求相對較小,也可使用SiP技術提升IC的效能。例如,高解析電視解調器(High Definitions TV Demodulator)若使用SiP可提升系統功能(圖5),以及高效能網路(Networking)方面的應用(圖6)。這些應用讓系統有更寬的頻寬(Bandwidth)、更小的功耗(Power Consumption),以及更低的電磁干擾(EMI),而這也是SiP能發揮其功效的地方。

最能感受到SiP所帶來上述好處的廠商,應是系統商(System House)和次系統商(Sub-System)。一般而言,電子廠商在開發新產品時所必須考量的重點,包含產品的成本是否具競爭力、功能是否滿足消費者需求,以及創新與上市時程是否符合市場潮流。

從圖7的雷達圖(Radar)可以看出SiP技術相對於傳統印刷電路板(PCB)與系統單晶片(SoC),在開發與系統板成本、上市時間(Time-to-Market),異質可整合性與記憶體容量方面都略勝一籌。

|

資料來源:Gartner、Morgan Stanley、GUC

圖7 SiP相對於傳統印刷電路板與系統單晶片的優劣比較圖 |

SiP增強產品競爭力

一般而言,SiP具有微型化、可異質整合、可降低系統板(System Board or PCB)成本、可縮短產品上市時間,可以提升產品效能等幾項優點,接著逐項說明。

| ‧ |

|

| |

|

| 圖8 SiP應用堆疊、縮小間距技術將數顆晶片整合在一起。 |

如圖8所示,SiP應用堆疊、縮小間距等技術,將數顆晶片整合,縮小所占面積。圖8左為電子顯微鏡(SEM)照片,顯示堆疊、接線(Bonding)等之精密封裝技術。

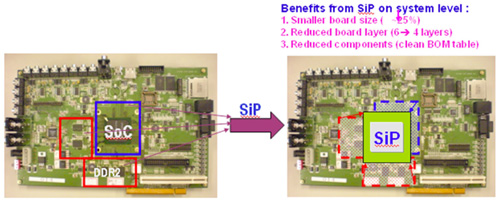

如圖9所示,系統板上原先有一個系統單晶片,或稱之為特殊應用積體電路(ASIC),四顆DDR2,以及一些被動元件(Passive Components)。

而SiP技術將上述原本各自獨立分開的積體電路與被動元件,整合成一顆SiP,將印刷電路板的面積縮小,甚至電路板層數亦得以縮減,使得產品能達到更輕、更薄、更短、更小的目標,這是SiP技術最容易被看到的優點。 |

|

| 圖9 系統板藉由SiP,達到微型化示意圖 |

| ‧ |

|

| |

異質整合也是SiP的優勢,所謂異質是指不同技術如互補式金屬氧化物半導體(CMOS)、類比(Analog)、射頻、微機電系統(MEMS)等,不同製程如90奈米(nm)、65奈米、40奈米、28奈米等,不同晶圓廠甚或不同尺寸如12吋、8吋等等的晶片整合在同一封裝內,使各種功能不同的晶片能選擇使用其最具成本效益的製程。 邏輯(Logic)CMOS製程已來到28奈米,將上述不同技術等整合在同一系統單晶片的困難度日益升高,成本、時間大幅增加,效益卻不見得可以提升,權衡得失,取捨之間,SiP可異質整合的特性,可提供一個相對好的選擇(圖10)。 |

|

| 圖10 不同技術、不同製程和不同晶圓廠的晶片可以SiP技術整合在一起。 |

| ‧ |

|

| |

雖然記憶體良裸晶(Known Good Die, KGD)不見得比封裝好的成品便宜,整合多顆IC的人工成本也會增加,因此SiP本身的成本可能增加,但上述印刷電路板面積及層數縮小,其省下的成本,通常可以超過SiP增加的成本,可以節省開發系統單晶片所需高額的研發成本,與較短的開發時程。這也是為何最能感受到SiP所帶來上述好處的廠商是系統商和次系統商的原因所在。 |

| ‧ |

|

| |

經由前面所說的異質整合,SiP技術可使產品的上市時間(Time To Market)相對縮短,符合電子產品隨時代流行迅速變化的特性。例如,若要將類比與射頻晶片同時整合在標準邏輯晶片製程上,其設計與製造技術的開發時程與困難將遠比已經各自成熟的技術多很多,將嚴重影響電子產品最重視的上市時間與成本。 |

| ‧ |

|

| |

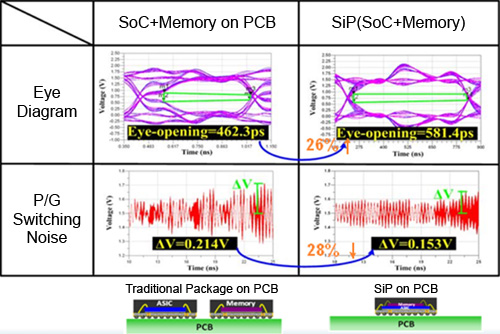

相對印刷電路板的模式,SiP技術可以縮短金屬線上的距離,進而降低其寄生阻抗(電阻/電感/電容),以提升傳輸速度、改善電磁干擾,並能減低功耗(Power Consumption)。圖11為比較SoC+Memory on PCB與SiP(SoC+Memory)對於抖動(Jitter)眼圖(Eye Diagram)與抗雜訊(Power/Ground Switching Noise)的能力,SiP比傳統印刷電路板好。 |

|

| 圖11 SiP技術對比於傳統技術在抖動眼圖與降低雜訊能力約有25~30%的改善。 |

SiP技術挑戰重重

儘管SiP有很多優點,但不可避免的,也碰到不少挑戰,其主要困難點包括下列數項︰

| ‧ |

|

| |

裸片的來源並不容易覓得,並不是擁有IC成品的供應商就能提供裸片,尤其對使用非CMOS技術的IC更為困難。另外裸片難免碰到製程轉換或停產問題,可能被迫在SiP產品週期的中途更換裸片,因此在選擇裸片之初必須考量其產品生命週期(Lifetime),甚至了解裸片供應商在規畫下一代產品的兼容性(Compatibility)與可替換性,這些默契都是必須與供應商長期策略合作方能達成。 |

| ‧ |

|

| |

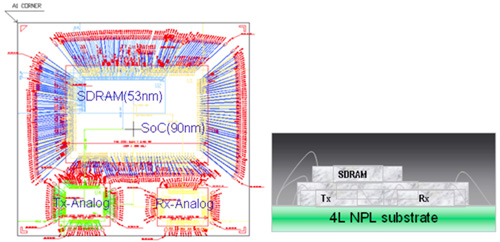

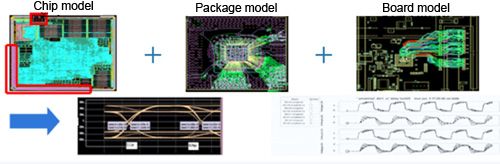

晶片、封裝與電路板的協同設計(Co-design)與協同模擬(Co-simulation)的技術複雜度,隨著SiP內異質功能的晶片越多與傳輸速度的提升也日益升高。SiP內每一種晶片可說是一個次系統,如何讓每一晶片都能在最佳狀態工作,協同設計與協同模擬在產品設計之初就變得相當重要(圖12)。 |

|

| 圖12 事先做好晶片/封裝/電路板的協同設計與協同模擬,可以省掉很多麻煩。 |

| ‧ |

|

| |

整合進來的裸片愈多,封裝內空間愈窄,散熱(Thermal Solution)問題愈不容易解決。因此必須經由熱模擬來選擇最適當的封裝以及選擇功耗低、耐熱品質高的裸片來解決散熱問題。裸片供應商在其產品本身的封裝所遭遇環境與散熱的條件必定與SiP廠商面臨的有所不同,如何確保其品質能夠滿足不同封裝環境的需求,也是一種關鍵技術。 |

| ‧ |

|

| |

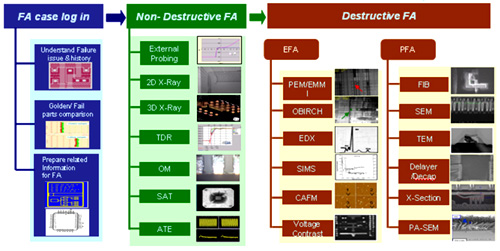

SiP整合進來的裸片愈多對於良率(Yield)的挑戰愈高,而且不良品分析(Failure Analysis)因為牽涉數種晶片而變得更複雜。最佳的情況是在設計剛開始就能考量各個晶片能夠在SiP封裝上獨立測試分析來層別失效問題,進而對症下藥來改善良率。否則,若須要破壞封裝將各個晶片取出分析,受限於取出過程中可能損害晶片本身或重新打線的問題,失效問題將不容易澄清解決(圖13)。 |

|

| 圖13 不良品分析流程示意圖 |

| ‧ |

|

| |

傳輸速度愈快,整合進來的晶片愈多,後端測試(Final Test)更形困難,尤其異質晶片的測試程序開發將考驗工程師的能力與經驗,也是達到高品質良率的一大障礙,因為客戶將可能因為任一晶片失效,整顆封裝也跟著失效,良率勢必降低,成本提升。 |

SiP與SoC 一加一大於二

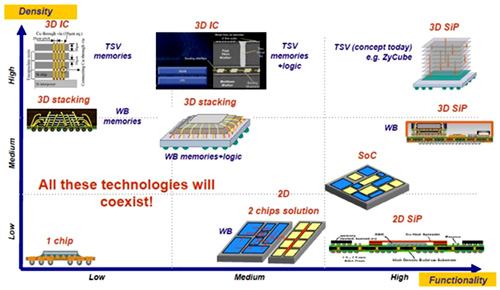

系統單晶片是很多電子產業首先想到的解決方案,但亦有其缺點和力有未逮之處,系統單晶片和SiP各有其優缺點,兩者相互搭配,可收一加一大於二的加乘功效。使用者應在了解各自優點和缺點,整體考量應用產品的特性與要求後,選擇一個最適合的技術來使用。

同樣地,SiP也有很多種類,有平面置放(Side-by-Side);有堆疊;有使用裸片,也有使用封裝好的IC堆疊而成的PoP;有將被動元件埋藏在基板內,也有將被動元件作成晶片型式的IPD(Integrated Passive Device),林林總總。每一樣也各有其優缺點,如同SiP與系統單晶片的搭配一樣,使用者應先了解各式SiP的優點和缺點,考量產品的特性與要求後,選擇一個最適合的SiP來使用。

更重要的是,找一個經驗豐富,值得信賴的SiP供應商,齊力合作,解決第三段中所提到的技術瓶頸,尋求一個最能提升產品競爭力的SiP應用方案,更是成功的關鍵(圖14)。

|

資料來源:Yole

圖14 針對不同功能、不同特性的產品,SiP解決方案亦將不同。 |

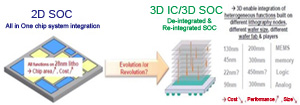

新一代3D IC TSV受矚目

儘管IC的發展日新月異,過去的30多年,幾乎每一年半到兩年,製程就會前進一個世代,但這還是無法滿足求新求變的需求,尤其在以下這幾個項目:更強功能,更多功能整合,持續微型化;更高頻寬,更快速度;以及更省電方面。

|

| 圖15 從平面到立體,TSV提供延續摩爾定律的平台與機會。 |

因此師法SiP堆疊的技術,將原先是平面(Planar)的IC結構朝向三維(3D)發展,而層與層之間以矽穿孔(Through Silicon Via, TSV)的方式相連接也就因應而生,各層可以同質(Homogeneous),也可以異質(圖15)。

TSV雖然已經談了好幾年,截至目前真正開始量產的只有CMOS影像感測器(CIS),主要原因應是成本考量。但幾乎全世界所有的整合元件製造商(IDM)及晶圓廠(Foundry)對TSV都有所著墨,相信在未來的一到一年半內,應可見到其他技術的產品開始量產。

(本文作者為創意電子SiP/3D IC專案營運處處長)