碳化矽(SiC)開關對於電源轉換器在尺寸、重量或效率的差異化方面越來越重要。SiC獨有的材料特性,可設計無少數載子的單極裝置,取代電荷調變IGBT裝置。因此,它可提供最高效率、更快的切換頻率、減少散熱及省空間等優勢,也可降低整體成本。

除了靜態和動態效能之外,還必須解決進一步的議題,才能充分應用於更高容量的變頻器。適當的可靠性,就如同足夠的閥值電壓和應用導向短路耐受性一樣必要。相容於以VGS=15V驅動導通的IGBT,將有助於簡化從IGBT變更為SiC MOSFET解決方案的流程。

阻斷電壓1,200V的SiC MOSFET在太陽能變頻器、UPS、電池充電器及工業驅動器等應用領域皆受到矚目。若能降低切換與傳導損耗,對這些應用都有助益;善加利用熱預算,有利於實現更高的開關頻率,且能縮小被動元件的實體尺寸,並大幅減少冷卻作業、重量及成本。

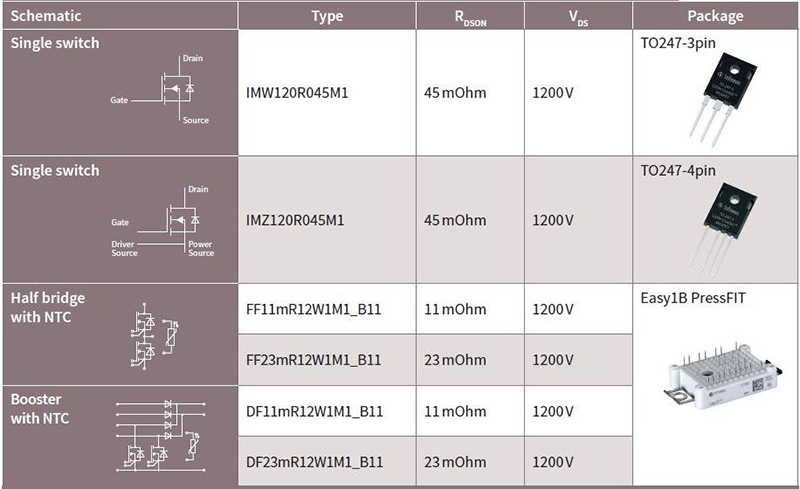

目前市面上已有SiC電晶體採用T-MOSFET設計,如英飛凌推出的SiC-MOSFET系列,其開發宗旨是限制導通和關斷狀態下的閘極氧化物電場。即使以穩定且可重現的方式進行量產,SiC-MOSFET也能提供並達到1,200V等級的特定導通電阻。僅VGS=15V的驅動電壓搭配超過4V的閘極源極電壓,造就極低的導通電阻,也成為SiC電晶體應用的全新標竿。圖1這些邊界條件是用於轉移品質保證方法的基準,而這些基準是矽功率半導體產業為了確保達到工業應用、甚至汽車應用所期待的FIT率而訂定。

圖1 SiC-MOSFET引腳概觀

圖1 SiC-MOSFET引腳概觀

想要獲得切換速度更快的IGBT和SiC電晶體,封裝設計同等重要。在現有的功率模組平台當中,有些封裝對於快速切換SiC裝置非常有利。雜散電感必須盡可能低,但同時也需要高度對稱的設計。相較於常見的具有底板的標準封裝,高度對稱、低電感設計的平台,更適合作為專為光電、非車載電動車充電及不斷電系統的SiC半橋及升壓解決方案。此外,彈性針腳網格可簡化PCB布局,並提供低於10nH的雜散電感。相較於現有解決方案,可大幅降壓70~80%。

SiC MOS裝置設計原則

SiC-MOSFET的開關損耗通常很低,特別是幾乎與溫度無關。先進設計活動聚焦於特定導通電阻,做為特定技術的主要基準參數。以4H-SiC為基礎的平面MOSFET,必須克服接近傳導帶的極高介面陷阱密度。其結果可促成極低的通道移動率,因此通道將為總導通電阻帶來極大的貢獻。高瑕疵密度反映在SiC-MOSFET裝置的各種特性之中。克服此兩難困境的觀察方法,是增加導通狀態下的氧化物電場,超過的值通常用於矽基MOSFET裝置。導通狀態下氧化物中如此高的電場可能會加速磨耗。這可以視為一項長期可靠性風險,特別是有關SiC基板的高瑕疵密度。

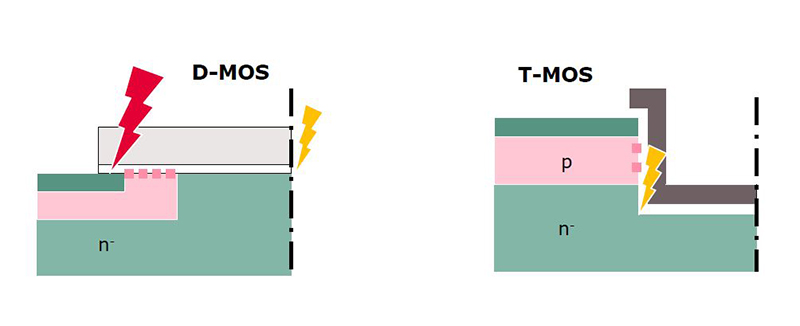

基於上述考量,如圖2左側部分所描繪,SiC的平面MOSFET裝置實際上有兩處與氧化物電場應力相關的敏感區域。左側部分,平面MOSFET的典型結構呈現與氧化物電場應力有關的兩個敏感區域;右側部分,溝槽式MOSFET典型結構的關鍵問題在於溝槽角落的氧化物電場應力。

圖2 平面MOSFET(左)與溝槽式MOSFET(右)的典型結構

圖2 平面MOSFET(左)與溝槽式MOSFET(右)的典型結構

首先,一般討論的反向模式中的應力是在漂移區域與柵極氧化物之間接近最高電場區域的應力,其次是在導通狀態下受到應力的柵極與源極之間的重疊部分。由於沒有裝置設計方法可降低導通狀態下的應力,因此一般認為導通狀態下的高電場更加危險。因此,整體目標是結合SiC的低RDSon潛能,以及提供運作模式,讓零件維持在經過充分調查且安全的氧化物電場強度條件。若要立刻在導通情況下達成此目標,可採取離開高瑕疵密度平面表面的作法,朝向其他更有利的表面方向發展。

閘極氧化物可靠性

SiC MOS裝置在閘極氧化物可靠性面臨的挑戰是,必須在特定的運作條件下,確保在預期的使用壽命中提供夠低的故障率,包括外部缺陷。典型的20年運作工業要求目標是<<100ppm。SiC MOS裝置閘極氧化物中的外部缺陷的根本原因,主要取決於基板材料的缺陷、晶膜製程,以及影響較小的其他製程鏈。商業MOSFET產品的測試結果,顯示此問題仍是應用於工業系統時的重大疑慮。

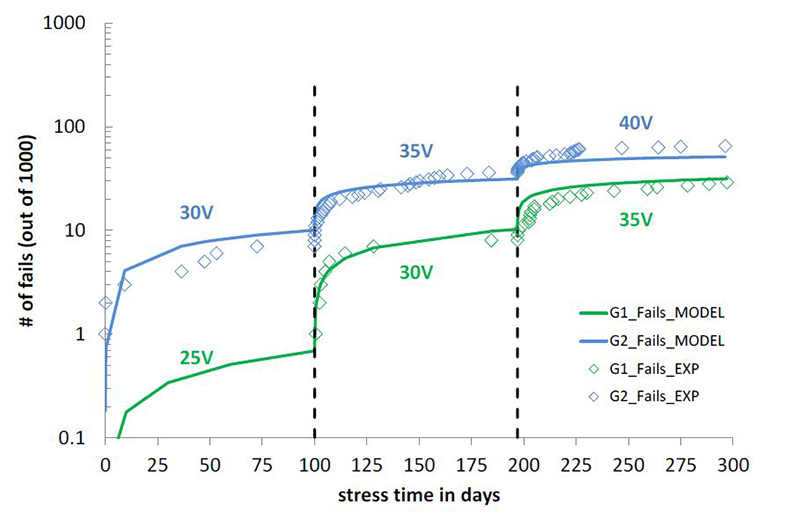

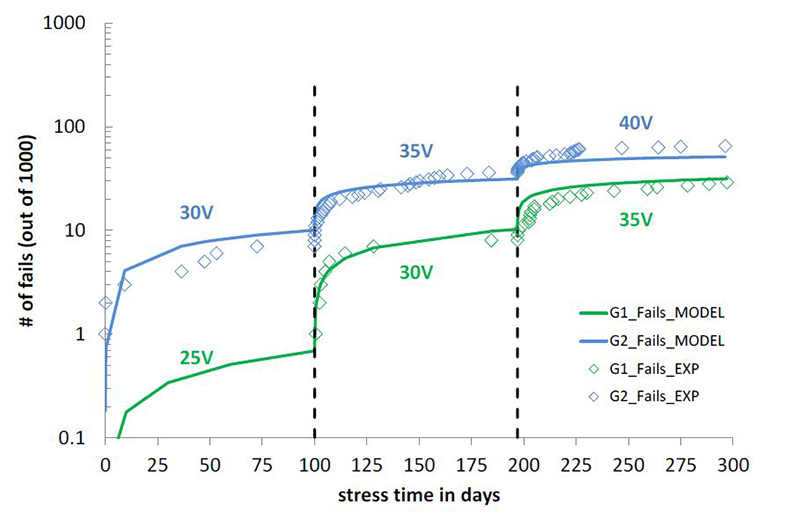

因此,英飛凌也對此進行長期測試,完成兩組各1,000個獨立元件的實驗,以調查SiC-MOSFET外部閘極氧化物故障率。實驗在恆定閘極偏壓應力下,以150℃執行三個為期100天的序列。圖3為長期測試結果,失敗次數繪製於施加應力的天數之上。總計2組各1,000個裝置,以150℃及顯示的恆定閘極電壓VGS進行測試。VGS每100天增加5V,每個點代表一次故障,實線表示線性E-Model的預測值。該圖總結了測試的結果,100天後閘極源極電壓增加+5V。將此結果外推至使用建議電壓20年的運作壽命,此模型預測故障率為0.2ppm,顯示閘極氧化物的可靠性類似於IGBT技術,並符合典型工業要求。

圖3 SiC MOS裝置外部閘極氧化物故障率長期測試結果。

圖3 SiC MOS裝置外部閘極氧化物故障率長期測試結果。

SiC-MOSFET動態效能

作為單極裝置,SiC-MOSFET的效能主要取決於它的電容。相較於輸入電容Ciss,此裝置具有較小的閘極-汲極反向電容Crss。在半橋組態中運作時,如此將有助於避免MOSFET產生寄生導通及複雜的閘極驅動電路。

圖4顯示半橋的典型開關損耗,它以單一裝置安裝於4-pin TO-247外殼中提供汲極電流的功能。斷開能量Eoff幾乎與負載電流完全無關,因為它由電容掌控,其導通能量Eon會隨著電流而線性增加。在電流20μA的應用中,總損耗Etot的總和為0.43mJ,可提供50~150kHz的切換頻率。

圖4 作為汲極電流ID功能時的典型切換能量。條件:VGS=15/-5V、RGext=4.5Ω、VDS=800V、Tvj=175℃、半橋組態的4腿TO-247

圖4 作為汲極電流ID功能時的典型切換能量。條件:VGS=15/-5V、RGext=4.5Ω、VDS=800V、Tvj=175℃、半橋組態的4腿TO-247

TO-247封裝的第4腳位可將閘極驅動器直接連接至源極腳位,避免因為源極雜散電感而導致來自負載電流的負回饋。因此,相較於3腿TO247半橋組態,在電流20A時約可節省100μJ總切換能量,這表示使用相同裸晶的封裝,僅須透過最佳化即可減少約30%。而圖5深入說明MOSFET藉由採用閘極電阻RG即可控制電壓斜率dv/dt。這對於驅動應用特別重要。但是降低電壓斜率dv/dt的代價是開關損耗的增加。

圖5 典型開關損耗(左軸)與最大dv/dt值(右軸)及RGext比較。條件:VDS=800V、ID=40A、VGS=15/-5V、Tvj=175℃、半橋組態的3腿TO-247

圖5 典型開關損耗(左軸)與最大dv/dt值(右軸)及RGext比較。條件:VDS=800V、ID=40A、VGS=15/-5V、Tvj=175℃、半橋組態的3腿TO-247

顯然在沒有dv/dt限制及增加切換頻率的應用中,可以減少更多損耗。這常見於DC-DC升壓或升/降壓拓撲,可提供更小、更輕及更低成本的磁鐵元件。各種研究已經證實,雖然使用更昂貴的功率開關,仍可在廣泛的應用之中減少物料成本。就中期而言,由於預期SiC元件成本將隨時間下降,應用數量將會增加。

SiC-MOSFET靜態效能

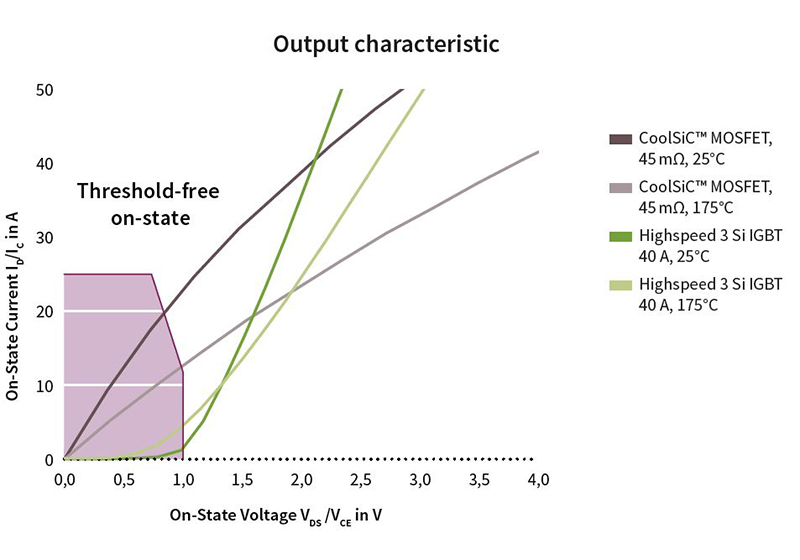

MOSFET靜態輸出特性的關鍵參數是總電阻RDS(ON)。新推出的裸晶在室溫、VGS=15V時具有45mΩ的典型導通電阻。導通電阻的正溫度係數使該裝置已預先設計用於並聯用途。圖6提供輸出特性並與先進的1,200V HighSpeed 3 IGBT直接比較。

圖6 典型SiC-MOSFET輸出特性與IGBT解決方案的比較

圖6 典型SiC-MOSFET輸出特性與IGBT解決方案的比較

由於膝節電壓的導通特性,特別在部分負載的情況下,可大幅降低傳導損耗。就系統層級而言,膝節電壓自由導通行為特性可望大幅降低損耗。許多系統在大半壽命期間皆於部分負載的狀況下運作,導通損耗遠低於競爭的標準IGBT技術。即使是在5kHz以下的極低切換頻率及未變更dv/dt斜率的情況下,仍然可以發現膝節電壓自由開關搭配整合式本體二極體(同步整流模式)相較於目前市面上的商用IGBT解決方案,有可能降低50%的總損耗。

相對於升壓級,典型變頻器應用須要定義完整的短路能力,特別是在現場發生故障的情況下。為反映這項重要需求,SiC-MOSFET相對於典型DMOS行為,傳輸特性(25℃/175℃)已揭示VGS=12V時的交叉點。高於12V時,電流隨溫度而降低,有利於在發生短路時限制飽和電流。

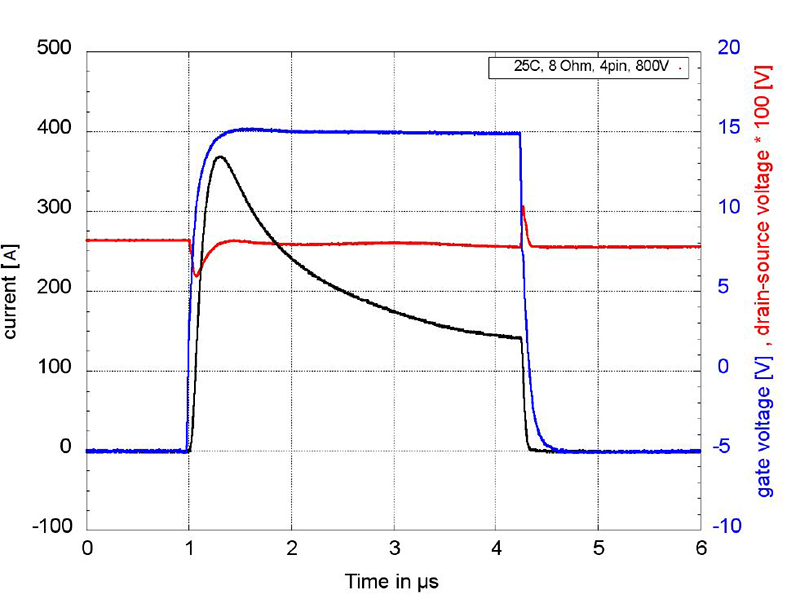

圖7表示最關鍵的所謂硬短路事件,並詳細分析在此特殊狀況下的行為與耐用性。具備短路規格的SiC MOSFET,相對於標準IGBT,短路電流比該裝置的標稱電流上升10倍。在第一次尖峰之後,由於上述依溫度變化的特性,飽和電流下降至相當低的程度。

圖7 具備短路規格的SiC MOSFET

圖7 具備短路規格的SiC MOSFET

SiC溝槽MOSFET結合低導通電阻和最佳化設計概念,可防止過高的柵極氧化物電場應力,提供類似IGBT的柵極氧化物可靠性。SiC溝槽MOSFET在切換行為與損耗方面具有良好的效能。

(本文作者任職於英飛凌)