由於LTE手機和穿戴式裝置引發更嚴峻的系統功耗、人機介面設計挑戰,因此製造商正加緊利用封包追蹤、DPD和FPGA等技術方案,延長電池使用壽命,同時研擬引入語音、手勢等新興人機介面,打造更具特色的新產品。

下世代行動裝置將為晶片商引來嶄新契機。從近期蘋果(Apple)全球開發者大會(WWDC)、Google I/O大會可窺見,行動裝置軟硬體技術演進正不斷加快腳步,而下一波穿戴式電子裝置的發展也正蓄勢待發。兩家大廠今年更特別注重使用者介面(UI)及人機介面的創新,相繼推出新一代行動作業系統,並加碼投資語音控制、手勢操作、眼球追蹤、多軸動作和3D深度感測等應用,皆為產業增添新亮點。

除了人機介面和軟體以外,長程演進計畫(LTE)也將為行動裝置晶片注入新活水,帶動新興射頻(RF)和省電技術研發需求;現階段,晶片商已將封包追蹤(Envelope Tracking, ET)和數位預失真(Digital Pre Distortion, DPD)方案,視為卡位4G戰場的重要武器,大舉投入研發。

改善LTE PA效率/線性度晶片商搶攻ET/DPD

因應LTE頻寬、速率大增,對手機功率放大器(PA)帶來的功耗和線性度設計挑戰,包括處理器、電源管理和RF晶片商皆加碼研發新一代封包追蹤和DPD晶片,以輔助PA動態調整電壓及增益值(Gain),大幅改善LTE手機RF子系統效率。

美商國家儀器(NI)自動化暨RF產品行銷經理潘建安(圖1)表示,雖然LTE為行動應用帶來更多發展空間,但也因技術規格躍升而引發諸多設計挑戰;其中,手機射頻子系統首當其衝,設計人員必須達成LTE高頻寬、高傳輸速率及多重輸入多重輸出(MIMO)天線的支援能力,同時有效控制PA功耗和線性度,因而掀起新一代封包追蹤、DPD技術導入需求。

|

| 圖1 NI自動化暨RF產品行銷經理潘建安認為,封包追蹤與DPD將逐漸成為LTE手機射頻子系統中不可或缺的功能。 |

事實上,封包追蹤和DPD早期係針對大型基地台設計,前者須具備封包偵測器(Envelope Detector)和電源調節器(Power Modulator),以因應不同的封包傳輸需求,動態調整PA供電壓,達到省電效果。至於後者則在數位訊號處理器(DSP)或現場可編程閘陣列(FPGA)中,內建查表式(LUT)或記憶多項式模型(Memory Polynomial Model)演算法,協助PA維持一定的線性度,以確保RF訊號品質。

隨著手機導入LTE、LTE-A需求湧現,行動晶片商和系統廠也開始聚焦這兩項技術,包括聯發科、高通(Qualcomm)和邁威爾(Marvell)等處理器業者,Nujira、RFMD、Skyworks、TriQuint與立積電子等射頻IP/晶片供應商,以及PMIC廠戴樂格(Dialog)皆大舉投入研發,揭開手機封包追蹤與DPD技術大戰的序曲。

其中,高通已率先在旗下RF360射頻解決方案中,新增封包追蹤晶片陣容,搭配其互補式金屬氧化物半導體(CMOS)PA,可因應LTE封包傳輸量需求動態調整PA驅動電壓,以節省電力;同時,聯發科則在旗下電源管理方案部門設立封包追蹤/DPD技術研發團隊,積極追趕高通的腳步。

Skyworks和TriQuint等射頻元件供應商,也透過向Nujira授權封包追蹤IP的策略,開發新款支援該功能的PA及周邊射頻元件;至於Dialog更醞釀在下一代PMIC中整合封包功率追蹤或DPD功能,以瓜分LTE設計新商機。

潘建安分析,一般認為手機最耗電的部分首推顯示器,其實射頻子系統耗電量也不分軒輊,而其中的PA就占高達50%以上功耗,遂成為影響手機續航力的元凶之一;尤其LTE與LTE-A將引進載波聚合(Carrier Aggregation)和MIMO等新技術,大幅增加射頻子系統複雜度,因此一線手機品牌廠遂開始要求晶片商提供封包追蹤與DPD方案,並規畫於明年上市的旗艦機種中正式導入這兩項功能。

近期封包追蹤、DPD測試驗證需求已顯著增溫,激勵儀器商競相卡位商機,其中,NI已搶先發布一套PXI模組化量測方案,並與相關晶片商陸續展開合作。

潘建安強調,封包追蹤和DPD測試須串連射頻訊號產生器/分析儀、電源供應器、任意波形產生器、高速數位I/O和示波器等多元儀器(圖2),並嚴格要求同步誤差低於100微微秒(ps),將為傳統以單機儀器為主的量測方案帶來嚴峻考驗;此將刺激晶片商和系統廠擴大改搭PXI模組化設備,以縮減設備占位空間、投資成本,並透過PXI通訊協定達成各個儀器模組間的精準同步,提供可靠的測試結果。

|

| 圖2 封包追蹤測試方案架構 |

繼手機之後,智慧眼鏡、智慧手表等穿戴式裝置可望將系統耗電規格推向新的里程碑,因而也刺激小封裝、低功耗的現場可編程閘陣列(FPGA)導入需求,以扮演顯示器、I/O和相機子系統與主處理器之間的橋梁,協助分擔耗電量較高的處理器運算量,進而降低系統功耗。

紓解處理器運算負擔 FPGA推升系統電源效率

|

| 圖3 萊迪思台灣區總經理李泰成指出,該公司已攜手多家穿戴式裝置開發商,共同研發基於FPGA架構的協同處理器。 |

萊迪思(Lattice)半導體台灣區總經理李泰成(圖3)表示,相較於採用數千毫安時(mAh)鋰電池的手機,穿戴式裝置在系統空間限制下,大多僅能搭載600mAh以下容量的鋰電池,但卻要提供數日以上的續航力,導致系統業者為如何「省電」這件事傷透腦筋。由於業者發現時脈較高的主處理器對穿戴式裝置功耗影響甚鉅,因此開始擴大導入微控制器(MCU)或FPGA等協同處理器,以減少主處理器開啟的頻率。

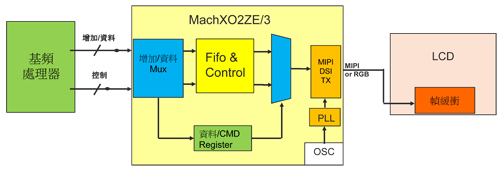

李泰成指出,基於協同處理器的設計概念,FPGA因具備大量平行運算及可編程特色,可應付顯示器、I/O和相機子系統等資料量較大的應用(圖4),相較於MCU更能突顯系統節能效益,正日益受到系統廠青睞。為進一步提高FPGA在穿戴式裝置市場的滲透率,萊迪思也積極耕耘更小型化的FPGA封裝技術,進而縮減晶片成本、耗能和占位空間。

|

| 圖4 FPGA於智慧手表顯示器設計範例 |

另一方面,FPGA亦可藉由軟體編程功能,幫助系統廠快速實現所需的創新功能,毋須耗時打造高成本的特定應用積體電路(ASIC)。李泰成認為,對穿戴式裝置設計而言,FPGA不僅能推升系統電源效率,亦是加速新功能商用的推手,可望逐漸在市場上嶄露鋒芒。

除了省電技術以外,穿戴式裝置亦掀動人機介面革新風潮,包括語音控制、手勢操作、眼球追蹤、3D深度感測、腦波和肌電感測技術,皆已成為作業系統和晶片大廠的布局焦點。

作業系統/晶片大廠力拱新人機介面進駐穿戴裝置

|

| 圖5 資策會智通所組長林敬文提到,繼動作和環境感測技術之後,生物感測將成為業界下一個熱門焦點。 |

資策會智通所組長林敬文(圖5)表示,穿戴式裝置與行動裝置連結應用,可望形成一個全新的智慧裝置生態體系,引爆龐大的感測器、無線聯網方案、人機介面,以及應用程式和雲端服務等軟硬體設計商機;相關市場研究單位更預估,穿戴式裝置的崛起,將在2018年帶動上兆美元的產值。

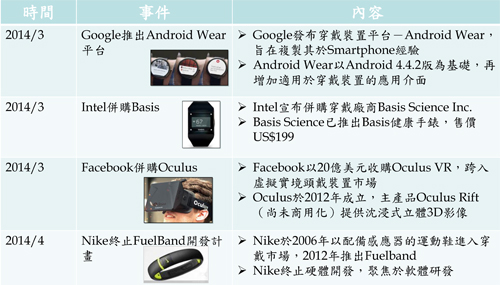

林敬文進一步指出,因應穿戴式裝置貼身、極致輕薄的設計,供應鏈業者已將如何實現簡單、直覺的顯示UI和人機介面視為布局重點(表1)。今年Google I/O大會中,Google即大動作揭櫫穿戴式專用平台--Android Wear、Google Glass GDK(Glass Development Kit),以及語音/手勢控制介面的開發成果;同時,三星(Samsung)、英特爾(Intel)及聯發科,近期也各自發表旗下的穿戴式裝置作業系統和開發平台的最新進展,足見市場熱度正快速上升。

|

| 表1 半導體與科技大廠投資穿戴式應用最新動態 |

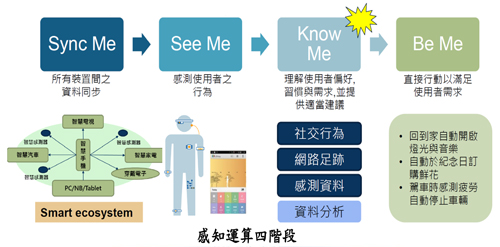

林敬文認為,新一代智慧型穿戴式裝置必須優化機器對使用者(M2H)、M2M互動功能,才能提高市場接受度,因此業界已歸納出四個穿戴式人機介面的發展階段(圖6),積極朝此方向邁進。首先是資料同步(Sync Me),穿戴裝置須透過無線技術無縫將資料傳遞至用戶的手機或平板等主要運算設備,接著為感測器驅動(See Me),穿戴裝置將透過感測器即時掌握用戶及環境變化資訊,協助使用者判斷。

|

| 圖6 人機介面實現感知運算功能的四個演進階段 |

至於第三和第四階段則跨入M2M領域,分別為資料分析與機器學習(Know Me)、人工智慧(Be Me),穿戴裝置將依據感測資訊,主動提醒或開啟相關應用,甚至能記錄用戶習慣,以人類的思考模式運用各種雲端服務。

林敬文強調,在科技大廠力拱下,智慧型穿戴式電子裝置正逐漸融入日常生活,目前雖然以搭配手機、平板等行動裝置,做為訊息提示的用途為主,但隨著創新人機介面的導入,穿戴式裝置的應用將出現更多想像空間,進而引爆下一波行動運算技術革命。