TSV用於3D IC架構的CIS中,可展現許多優勢,其中最重要的是成本較低,因而吸引國內外許多大廠紛紛投入研發,且也初步展現成果,產品陸續進入量產階段。若台灣廠商可掌握3D IC此一未來趨勢,並結合台灣鶴立雞群的IC產業鏈,將可研發領先全球的3D IC技術。

三維矽穿孔(3D TSV)的技術好處相當多,但是不同的互補式金屬氧化物影像感測器(CIS)特性影響結構甚鉅。如若不是採用晶元背後感光技術(Backside Illumination, BSI),則CIS的晶粒一定向上;TSV就必須根據球柵陣列(BGA)的落角設計。有關CIS設計(含TSV)技術的挑戰,包含光學設計、鏡片材料、量測、晶圓級封裝(WLP)與智財權的問題(Legal Aspects),以下一一介紹:

| ‧ |

|

| |

即使做到晶圓級相機模組,更須要有相當特殊的方法處理光學記號及迷光(Stray Light)問題,目前很少有光學設計者有此經驗。

除此之外,自動對焦用到的致動器(Actuator),機械方式的縮放、快門等方面的整合趨勢是必然的,但目前仍不太可能達到。 |

| ‧ |

|

| |

鏡片材料必須是可具有高產量、適合轉印微影術、可紫外線固化(UV-curable)、可在260℃回火(Reflowable),而且必須在嚴酷環境具有長時間的高穩定度。若是將玻璃基板與高分子異質(晶圓)整合,由於熱膨脹係數(CTE)的不匹配,所以在晶圓整合過程中就會產生翹曲(Warping)或彎曲(Bowing),因此,全玻璃式的技術整合是一個較有競爭性的技術。

為了色差修正(Chromatic Correction),需要不同材料的鏡片,這些材料包含冠冕玻璃(Crown Glass)或火石玻璃(Flint Glass),更多材料的需求將會出現在高分子上鍍抗反射層(Antireflective Coatings)、開孔(Aperature)層/隔離(Baffle)層、紅外線截止濾光片(IR Cut Filter)等。

|

| ‧ |

|

| |

非球面(Aspherical)的光學測試,以及不固定大小的微透鏡(Microlens)的檢驗都相當困難,若要有高良率與高產量的晶圓級透鏡,測試的方法相當關鍵。

|

| ‧ |

|

| |

一般而言,光學晶圓片無法保證平面,如上所述的彎曲、翹曲,再加上有可能晶圓兩邊都有光學設計,若是要堆疊三至六層的不同晶圓將非常困難。而考量到回火的溫度限制問題,要將晶圓堆疊後作膠合(Gluing)與封合(Sealing)有其難度。此外,要將完成後的晶圓級相機(WLC)作切割,會相當複雜,因為其包含不同的材料,這是良率最大的關鍵部分。

|

| ‧ |

|

| |

目前WLC或TSV的技術都已經被很多個專利所申請保護。一般而言,行動電話所用的相機模組利潤不高,WLC的製造商可能無法從中獲利,以創造更多的技術或對於專利付出更多的專利授權費用。

|

國際大廠競相開發3D IC架構CIS

目前宣稱有TSV技術的CIS設計公司包含東芝(Toshiba)、三星(Samsung)、精材(Xintec)、豪威(OmniVision)、台積電、Zycube、索尼(Sony)、Oki、意法半導體(STMicroelectronics)、CEA Leti、Sarnoff/RCA與Aptina/美光(Micron)。各家公司產品發表的年代都是在2007~2008年(表1),但大都仍是實驗階段的產品。

東芝率先投入3D IC CIS研發

東芝是第一個使用TSV技術量產CIS的公司,而且新的CIS/TSV模組與原有的CIS模組的價格相同,因而使其他CIS製造商更加積極開始投入TSV的技術。雖然CIS/TSV是一個全新的技術,但東芝剛推出時,即使以同樣的價錢銷售,也沒有引起銷售商或原始設備製造商(OEM)的注意,這是因為使用非3D設計的CIS還無法使產品的庫存降低。只有少數的設計因使用3D CIS的優點,也就是外觀尺寸變小,獲得較好的利潤,畢竟,要確認一個製程是否有經濟上的好處,須讓產品試驗約1~1.5年。

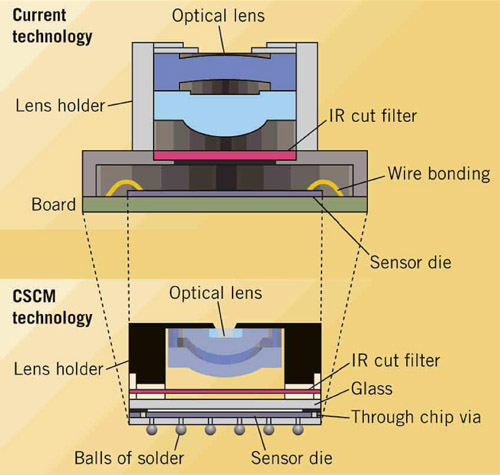

圖1是東芝於2007年10月日本消費性電子大展CEATEC上展出的超小型化影像感測器模組--晶片級晶片模組(Chip Scale Chip Module, CSCM),代號為Dynastron。因為減少打線封裝(Wire Bonding),所以可縮小寬度與基底尺寸,當時便宣稱可以減少64%的封裝體積。2009年東芝在國際固態電路會議(ISSCC)的另一個作品則是體積由原有的5.0毫米×5.0毫米×3.5毫米減小為4.0毫米×4.0毫米×2.5毫米,體積縮小的幅度則為45%。東芝八百萬畫素CIS的量產已在2009年第二季開始。該公司並在2009年4月公布1.75微米畫素(μm pixel)產品,八百萬畫素1/2.5吋的CIS(型號ET8ER4-AS)用在高階的照相手機上,具有自動對焦的功能。此型號應該尚未導入TSV技術,但兩百萬畫素五分之一吋就是使用CSCM/TSV。

|

| 圖1 東芝的3D CIS模組 |

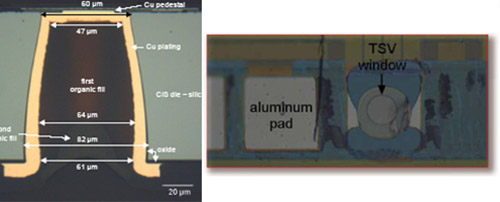

因為東芝是第一個將TSV技術導入CIS產品的公司,所以專門做晶片逆向工程的Chipworks,也已針對東芝的CIS作了一分完整的逆向工程報告(圖2),由圖2可知,該TSV約有60微米大小,深度約為120微米。

|

| 圖2 Chipworks公布東芝Dynastron的逆向工程結果。左為TSV橫切面圖,右為TSV與鋁焊墊關係圖。 |

意法半導體搶攻五百萬畫素CIS市場

以手機用CIS的產品線而言,五百萬畫素的CIS是目前工業界最競爭的CIS產品。歐洲的意法半導體使用65奈米/45奈米製程設計其五百萬畫素CIS,尺寸為四分之一吋,畫素大小為1.4微米,整體晶粒大小為6.5毫米×6.5毫米,整體的模組高度只有5毫米。此CIS可提供擴展景深(Extend Depth Of Field, EDoF)的特性。該公司的CIS都包含兩個介面,一為單線(Single-line)或雙線(Dual-line),可操作在1GHz的照相 機串列介面(Camera Serial Interface-2, CSI-2),這個介面由行動產業處理器介面(Mobile Industry Processor Interface, MIPI)聯盟所制定。另一個介面是可以操作在650Mbit/s的簡潔照相機埠(Compact Camera Port 2, CCP2)介面,此介面由行動影像標準架構(Standard Mobile Imaging Architecture, SMIA)組織制定。

該五百萬畫素CIS就包含TSV技術。但是最後透過板上芯片(COB)封裝,再與一些光學元件形成模組。意法半導體認為,使用TSV技術就可以使CIS技術推展到晶圓級相機。該公司還認為這些前面照度(FSI)的CIS比BSI技術的CIS具有更好的量子效率(Quantum Efficiency, QE)與訊噪比(SNR)。

意法半導體CIS TSV尺寸大小為70微米、AR=1:1,蝕刻是使用博世(Bosch)所開發的非等向性矽深蝕刻製程方法,TSV內的絕緣層則是使用電漿輔助化學氣相沈積(PECVD)製程鍍上二氧化矽(SiO2)。在薄化的製程中,晶圓薄化前須在晶圓上面使用Brewer HT10.10黏劑,以便將晶圓放置到硼矽酸鹽(Borosilicate)載體(Carrier)上,再以180℃真空的條件下去除黏劑內的溶劑。此時進行電鍍(Electroplating),電鍍的時候使用低溫150℃的電鍍法電鍍銅(Cu)TSV。最後,在180℃將晶圓以滑走(Slideoff)的方式解除黏接。意法半導體2009年2月公布四分之一吋三百萬畫素、支援擴展景深的Raw Bayer感測器,代號為VD6853與VD6803的CIS皆使用TSV技術,其中VD6803使用10bit平行介面,VD6853則使用CCP2介面。焦距可從15公分到無窮大,畫素大小為1.75微米,使用的製程是90奈米,封裝完後的尺寸大小是6.5毫米×6.5毫米,據了解,該產品已於2009年第四季量產。

三星推出封裝完全CIS

在亞洲地區,三星也不落人後。該公司用其8吋廠製造CIS,與過去的代工模式不同的是,三星交給客戶的是已經封裝好的CIS,如此一來,客戶可以直接使用在相機的製造。該公司的最大競爭者是豪威,2008年三星就已使用TSV CIS與基板相接,但是,客戶仍須要將其控制IC與三星CIS用另一個封裝相接,這與3D CIS的最大目標,也就是感測器加類比數位轉換器(ADC)加影像訊號處理(ISP)堆疊的終極目標仍有一段距離,據了解,三星的CIS/TSV最大解析度僅有200dpi。

Tessera以既有封裝技術發展TSV

上述的東芝、三星與意法半導體皆為整合元件(IDM)大廠,另一廠商則是以封裝技術為主的Tessera,該公司也頻頻大力宣傳其TSV技術在CIS使用上的好處。這家自我定位為電子產業微型化技術供應商,最有名的事件就是約於兩年前向美國國際貿易委員會(International Trade Commission, ITC)提告,指國內外個人電腦(PC)應用相關廠商共十八家侵犯該公司於美國的DDR2、DDR3的BGA封裝技術三項專利。台灣廠商除了南科、力晶、茂德、金士頓之外,還有個人電腦大廠宏碁等通通被提告,不過,ITC於2009年8月底初判Tessera敗訴,禁止侵權的產品出售到美國也未成立,12月29日終判維持初判的結果,台灣廠商可謂鬆了口氣。

|

| 圖3 Tessera Shellcase MVP解決方案 |

Tessera過去以來即發展很多封裝技術,特別是在多種晶圓級相機尺寸封裝(WLCSP)技術。這個技術使用到一個適應層(Compliant Layer),此適應層是為解決兩個元件相連接時的散熱問題,特別是矽元件要貼到印刷電路板(PCB)時的接觸問題。Tessera的WLCSP還分為幾種技術,包括MVP、RT、CF、OP CSP、OC CSP,其中Shellcase MVP技術(圖3)是一種應用TSV技術的WLCSP,可用來設計影像感測器,用於照相手機、數位相機、個人數位助理(PDA)、數位掃描器與指紋識別,整體封裝後的高度為500微米。

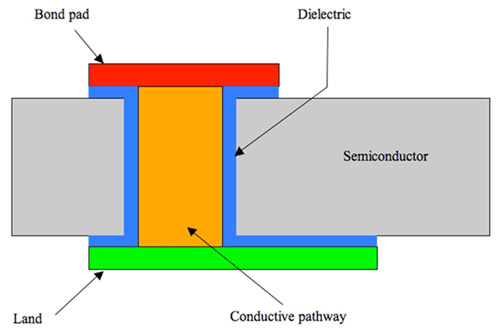

Tessera視TSV為一個水管/煙囪(Pipe),圖3的這些BGA錫球會透過所謂的過孔穿過焊盤(Via-through-pad)TSV與內部的電路相接(圖4)。這個設計的好處,除提供高密度的整合,還提供高速與可靠的訊號品質。Tessera測量一個最差路徑,具有3.2毫米長度的路徑,從黏著板(Bond Pad)到錫球的接觸點,電氣特性為R=270毫歐姆(mΩ)、C=0.99皮法(pF)、H=0.74nH。Tessera為證明其TSV高可靠度,採取了JEDEC的JESD22可靠度相關測試標準,該CIS在溫度、溼度、熱循環各種加壓測試下都證明可達到相當好的可靠度,以溫度與溼度而言,都要超過4,000小時以後才會有問題。

|

| 圖4 Tessera Shellcase MVP中的TSV結構 |

Tessera技術授權的廠商相當多,如Nemotek號稱是第一個獲得Tessera 精材與OptiML技術授權的公司,該公司具有TSV技術的CIS僅0.6毫米。Shellcase也授權給Advanced Wafer Level Packaging(AWLP)。值得一提的是,富士通微電子(Fujitsu Microelectronics)設計的一款影像處理晶片組Milbeaut,就是使用Tessera FotoNation FaceTracker影像強化解決的技術,該方案能在一個影像資料中即時辨識並追蹤超過十張人臉。Milbeaut晶片組為FotoNation FaceTracker解決方案加入硬體加速功能,使其較單純軟體解決方案增加約十倍速度,此晶片組即使用TSV技術。 上述Tessera的技術也授權給卡西歐(Casio)的相機產品。根據資料顯示,FotoNation FaceTracker解決方案能在相機的觀景窗中追蹤臉部,0.1秒內即可於一個影像內偵測到超過十張人臉,並持續動態追蹤臉部影像,如判斷是否有眨眼,即使翻轉或側拍亦能成功鎖定。該相機採用臉部資料調整影像拍攝設定,如曝光與對焦,即使在逆光或偏焦的情形下,也能讓人像具備良好的光線與對焦效果。

台積電TSV CIS技術能力到位

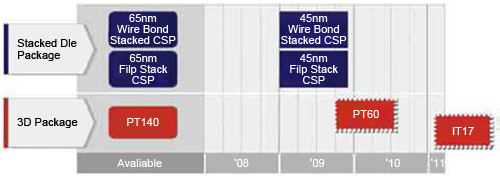

2009年4月台積電於聖荷西的技術專題討論會(Technical Symposium)說明該公司的技術里程碑(圖5),其中PT140是為CIS研發,採取背面TSV,PT140就是140微米的間距,目前已可生產,PT60製程在2009年底提供,而iT30與iT17都是Via Middle製程,會在2011年第二季完成,相信這些技術都是屬於台積電開放創新平台(Open Innovation Platform)的一部分,在2009年的一篇報導中指出,台積電目前可用0.11微米CMOS製程製作兩百萬、五百萬及八百萬畫素的CIS。參考資料的報導中亦提及在2009年6月即準備好。

|

| 圖5 TSMC的TSV技術里程碑 |

Allvia專門代工TSV技術

3D IC不管是由孔先(Via-first)或孔後(Via-last)製程完成,都涵蓋晶圓的薄化(Thinning)、鑽孔(Via Formation)、填孔(Via Filling)與接合的動作。這對於既有的半導體生態會產生巨大的衝擊,因為沒有一家廠商可以全部統合上中下游的製程,所以TSV代工廠應運而生。Allvia是世界上號稱第一家針對TSV代工的代工廠,2009年順利拿到500萬美元資金,該公司的TSV技術可達10微米,此技術適用於微機電系統(MEMS)與感測器。該公司可提供的服務包含Via設計、Via深蝕刻(Deep Etching)、以銅為材質的Via填孔、後面挖孔(Via Backside Opening)、孔洞/晶粒的黏接與凸塊生成(Via Die Attaching/Bumping),其中填孔技術可接受的孔洞大小可由30~500微米。

CIS/TSV價格已具競爭性

在參考資料中,Tessera認為一個200毫米的晶圓約可切割七百五十至一千兩百五十個CIS晶粒,CIS幾乎都是WLP,因為都在晶圓上直接封裝,再分割成每一個裸晶到另一個基座上,通常再以BGA封裝連接到PCB上,因此,可大幅降低封裝的費用,因為所有好的裸晶費用都是由所有合格晶片(KGD)平分。根據International Semiconductor Equipment and Materials Consortium與SEMATECH的估計,可接受的TSV費用,一片晶圓約在150美元以下,因此,分攤到一個CIS模組,應該要少於1美元。從東芝2009年提供的樣本價格中,1/2.5吋格式八百萬畫素(20美元)與五分之一吋格式兩百萬畫素(10美元)可知,其價格相當有競爭力。

善用3D IC趨勢 創造台灣半導體新產業鏈

隨著半導體產業先進製程越來越昂貴的發展,電子產品越來越要求高度整合,單晶片將要付出昂貴的開發成本,也更加不能為產業所接受。而高整合度系統晶片設計的發展趨勢,已逐漸發展至如何利用第三維(Z-dimension)創造3D IC。3D IC是一個獨立的IC,不同於現在的2D IC,其透過垂直與水平整合大量提高集積密度,因3D IC的高度整合,涵蓋半導體材料、IC設計、晶圓製程、電子構裝、測試之整合技術等,進入這個領域的障礙度相對提高,台灣系統單晶片(SoC)設計產業似乎已開始面臨無法與國際大廠競爭的態勢。

就台灣半導體產業過去的發展來看,台灣IC產業鏈完整且具有競爭力,IC設計業產值僅次於美國,居全球第二;晶圓代工產業以近七成的市占率居全球第一;IC封裝與測試產業則分別以近五成與近七成市占率居全球第一。此外,台灣半導體群聚效應十分明顯,大大減低開發成本,增加台灣廠商在價格上的競爭力。

目前台灣是12吋晶圓廠密度最高的國家。在製程技術小於3x奈米技術節點後,3D IC是唯一能持續有效增加產品效能、減低功耗、降低成本、縮小體積及整合異質IC的主流技術,也是系統單晶片發展瓶頸的出路,預期將可創造重大產業效益。由於3D IC橫跨半導體材料、IC設計、晶圓製程、電子構裝、測試之整合技術,因此台灣廠商此時開始進入3D IC的技術開發,可結合台灣位居世界第一的半導體與電子構裝的製程技術,開發出超越國際上其他研發聯盟的3D IC。

(本文作者依序為工研院資通所專案副組長、南台科技大學科技管理研究所助理教授)