高速資料傳輸與快速電源輸送在近幾年的發展,已蔚為電子產品主流規格,尤其是USB Type-C發表之初,即標榜高速傳輸與快速充電兩者兼備為主要優勢,上市至今卻面臨兩者擇一而用,市場上可見產品難以見到兩者兼用,主要關鍵在於高頻訊號雜訊、低頻訊號雜訊、高低頻混波雜訊是目前的問題根源,在目前業界於低頻雜訊所產生的電磁波干擾,基本上已有若干的解決策略可以處理,而高頻雜訊對射頻訊號產生的共振干擾,基本上仍難有顯著緩解成效,而對高低頻混波雜訊處理,則是更遙不可及的目標。

目前雜訊處理在緩解干擾的處理手段而言,常態以模扼流圈(Common Mode Chokes)削弱共模干擾,是在一個閉合磁環上對稱繞製方向相反、匝數相同的線圈,實質上是一個雙向濾波器,一方面要濾除訊號線上共模電磁干擾,另一方面又要抑制本身不向外發出電磁干擾,以避免影響同一電磁環境下其他電子設備的正常工作。

此外也可以雜訊濾波器(Noise Filter)來降低雜訊干擾,其目的是在降低設備和電源之間電源線上傳導的電磁干擾,卻使得原有正常訊號衰減損耗過大。因此需要外加訊號中繼器(ReDriver),通過訊號均衡化和預加強等技術,重新加強再發送出去,可以重新產生訊號,在高速接口上增加訊號能量。或是外加訊號調節器(ReTimer),通過內部時脈重構訊號,再恢復後發送出去,實現數據的恢復之後,然後再按照串行通道,把訊號發送出去,可以減輕訊號的抖動。

但因為高頻波段甚寬,所能改善的程度受到極大限制,不易處理倍頻的訊號傳輸,而且只能緩解局部頻段的干擾。也因此在機板上覆蓋屏蔽罩(Shielding Case)或黏貼吸波材(Absorber Introduction)則成為最後手段,干擾程度輕微者也許只使用上述兩者其中之一,干擾程度嚴重者則是上述兩者同時使用,甚至在使用上述遮蔽材時,會在另加導電泡棉(Conductive Gasket)與產品外殼電線接地端(GND),然而卻是只能解決低頻雜訊的電磁干擾,對於高頻雜訊或是高低頻雜訊混波,對於天線的射頻干擾緩解也是極其有限,因為各種包覆材的大量使用導致靜電放電(ESD)與熱的問題,又成為待解且需要增加成本的難題。

當使用電子元件或機構元件的緩解干擾方式仍是無效時,常見的方式是將產品從高速規格降低為低速規格來使用;或是從系統端的軟韌體控制切換成低速模式,來迴避干擾之形成;或是標榜支持高速資料傳輸的規格,卻是在其所搭配的周邊裝置或線材為低速傳輸規格,藉此避免干擾之發生;或是直接在官網上宣告這種干擾起源原因,藉此卸責於協會規範所導致的原生問題。

雜訊干擾難解 解決方案推陳出新

為了解決雜訊干擾問題,各種解決方案推陳出新,各種理論公式交互應用,其根本乃是電纜線、電連接器、電路板、主控晶片之間的高頻與低頻特性不連續、串音隔離不佳、差模轉共模所導致。尤其是目前常見的高速介面USB 3.1/3.2、DisplayPort/Thunderbolt、HDMI/VitrualLink等,皆是因為主控晶片與連接器接腳排列定義,在電路板走線與疊構及電纜線線芯的排列與理線,四者之間連接無法完全匹配,再加上四者之間對接地的處理方式都不同,使得接地的迴路在這之間未能順暢,且目前業界都是將接地共接,未能將接地隔離處理,導致雜訊透過接地亂竄溢散而出,包含也透過屏蔽殼件與吸波材料接地後而竄出,使低頻干擾、高頻干擾、高低頻互擾現象由然而生。

在此針對接地這項業界常用於解決EMC的方式究論,接地如何接得好?如何接得正確?是共用接地好,還是分隔接地好?不同學術與實務論點各有不同,接地共接很大的關鍵是為了解決ESD問題,而對EMC/EMI/RFI問題則是效果不佳,因此如何使接地能夠達成真正較佳的屏蔽與隔離效果?屏蔽顧名思義就是覆蓋遮罩之意,也就是利用屏蔽的方式讓低頻雜訊、高頻雜訊、高低頻混波雜訊能被覆蓋遮罩不會溢散影響其他訊號品質;而隔離顧名思義就是隔開分離之意,也就是利用隔離的方式將高頻訊號、電源訊號、無線訊號獨立成為完整乾淨的訊號。但只做到屏蔽是不夠的,若能做到隔離才是完美的,倘若一開始就做到完整的隔離,屏蔽就非是必然的選項了。

就目前常見的高速接口與接頭連接器的規格來看USB 3.1/3.2、Thunderbolt 3、VitrualLink 1,都屬於正反可逆插式的USB Type-C外觀接口形式,在公頭與母座接口來看,高頻差動訊號為上下陳列的結構,而USB Type-C接口的舌板接觸結構厚度僅0.7mm左右,而差動訊號對又距離近無法超過0.5mm,再加上高頻差動訊號兩側,分別為電源正極(V+/VBUS)與電源負極(V-/GND),使得電源迴路甚大且環繞差動訊號對而排列,其又向後延伸為前後排列中之SMT或Hybrid(SMT+DIP)之焊接引腳,導致在電路板走線即先天受限無法形成獨立的高頻訊號組,再加上共接地與共電源的觀念架構為主流,在電路板上普遍都是將四根的電源VBUS引腳在電路板上共接,與將四根GND引腳在電路板上共接,使得差動訊號在電路板上的結構,與在連接器上的結構完全不同,也因此導致電源迴路的低頻雜訊,與差動訊號的高頻雜訊混波,形成難解之問題。

另外,為了追求大電流輸送供電,在電纜線的結構上,也是將電源4根合而為1根,將接地4根合而為1根,如此做法也是使得電纜線裸線結構與電路板形成不匹配,甚至是電源與接地分離,導致電源迴路過大,經由上述的結構處理不佳,高低頻混波雜訊現象在電纜線中更是常見,因此接地鋁箔/銅箔,或金屬編織網更是常做為屏蔽包覆雜訊,但卻因此提高了加工與材料成板,也將電纜線上的雜訊導至電路板或連接器上。

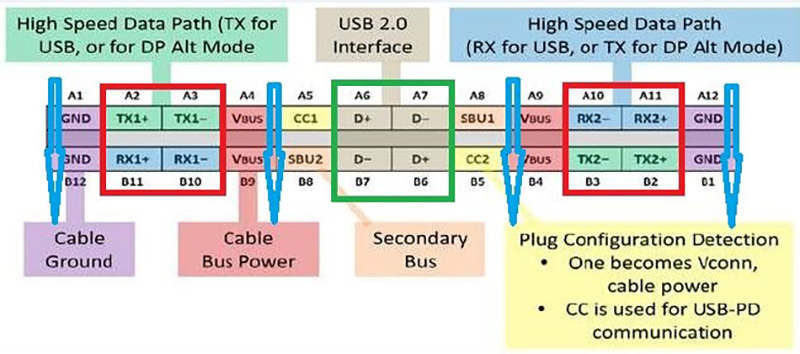

由圖1可得知,USB 3.1/3.2、Thunderbolt 3、VitrualLink 1的高頻差動對接觸區排列為上下對稱,即注定了高頻雜訊的串音干擾在原生結構已形成,而電源VBUS與GND所形成的電源迴路路徑環繞高頻訊號排列,即注定了低頻電源迴路過長而產生雜訊,又對高頻也產生高低頻雜訊混波。

圖1 USB 3.1/3.2、Thunderbolt 3、VitrualLink 1高頻差動對接觸區排列方式。

圖1 USB 3.1/3.2、Thunderbolt 3、VitrualLink 1高頻差動對接觸區排列方式。

而另一類常見的高速介面為高清影音傳輸接口與接頭,HDMI 2.1與DisplayPort 1.4這兩類為主要,其接口形式之舌板上的接觸位置排列,差動訊號對之間的對面為接地訊號,藉此形成高頻訊號組,再將此上下三角排列的高頻訊號組交錯反向排列,也因此原生結構並不能完全符合高頻原理,因此其無法符合下一代之更高速傳輸的要求,主要是在其高頻第一對與第四對的高頻接觸區,此兩對的高頻訊號僅有一邊設有一參考接地,而在另一邊並未設有參考接地,以致於插入與反射損失在此特性有諧波產生,甚至由接觸區向後延伸為焊接腳時,傳統的前後排列DIP式焊接腳本身電容效應嚴重,使得阻抗在此又產生電容效應在此位置向下掉了許多。若是改成目前常見的單排SMT形式,其高頻差動對之間穿插接地腳,而不同對的高頻腳又相鄰,使得高頻訊號特性阻抗向上產生突波,及高頻訊號對之間串音干擾嚴重,也因此這兩種高清影音介面要能單通道速度達成20Gbps,或是不可能在單通道達成高頻20GHz以上要求。

而HDMI與DisplayPort的原生設計中,HDMI的第1/3Pin與第10/12Pin,及DisplayPort的第20/18Pin與第9/11Pin兩者規格面臨高頻差動對兩側之一邊未有GND為參考隔離,使得高頻特性在此面臨窘境。

焊接接腳排列為重點所在

綜合以上淺論的各項問題,其實最大關鍵來自於正視焊接腳的排列,尤其是在連接器與主控晶片兩大重要元器件。而電路板的走線與疊構以及電纜線的裸線與排布,則是遷就配合主控晶片及連接器的腳位排列,就目前業界常見的做法而言,很難將連接器與主控晶片整合出最適當的腳位排列方式,導致電路板與電纜線在實務應用上困難重重。

在主控晶片上四邊來論,普遍都是高頻訊號之間以單接地隔離且共排列於一邊,電源與低頻訊號未以接地隔離共排列於一邊,而其他功能/偵測/時脈訊號則是也未以接地隔離共排列於一邊,最後對上端的相關訊號則是共排列於一邊,如此四邊分別排列,也因此目前從晶片端的訊號打出之後,就不是最佳狀態之訊號。

若從電路板設計而論,目前電路板上的走線方式,基本上都會由主控晶片廠商建議,常見的建議有幾種:高頻訊號對為了追求Skew與Delay優異,主要都是犧牲插入/反射損耗,再外加ReDriver或ReTimer補償訊號衰減;也對於近遠端串音干擾產生,以增加成本用多層板防止訊號之間穿繞現象;更對於共模對其他訊號發生共振,以增加成本用模扼流圈或雜訊濾波器,來消除共模和濾除雜訊;甚至是外加蓋屏蔽罩或黏貼吸波材來屏蔽雜訊,甚少從線路上去做優化與改善。

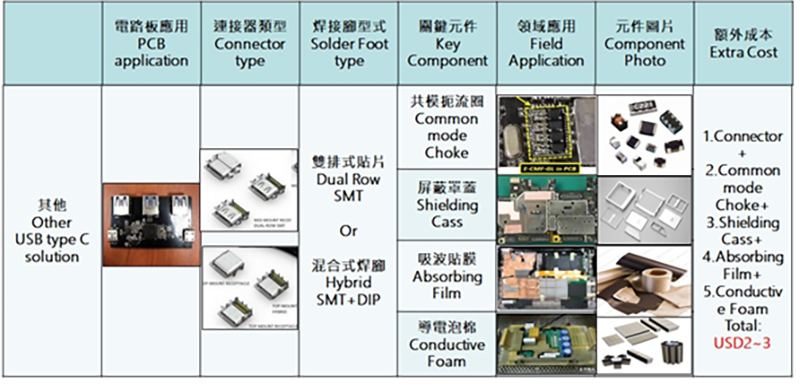

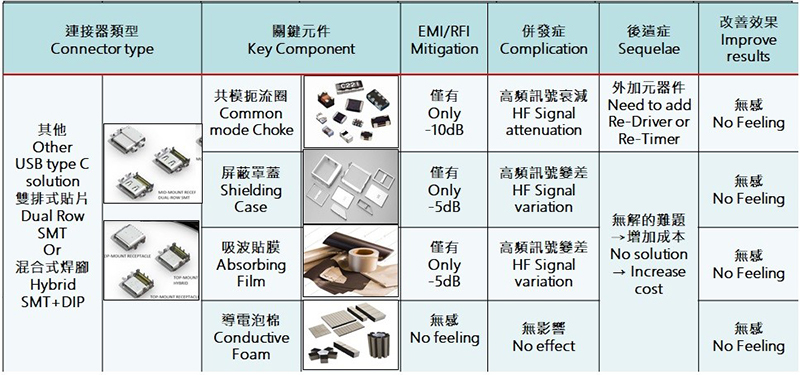

然而,如表1與表2所示,增加其他元件時,含工帶料所須增加的成本高昂,但對於改善高頻或高低頻混波對射頻干擾緩解效果有限。

表1 增加元件含工帶料所需成本高昂。

表1 增加元件含工帶料所需成本高昂。

表2 增加其他元件對於改善高頻或高低頻混波對射頻干擾緩解效果有限。

表2 增加其他元件對於改善高頻或高低頻混波對射頻干擾緩解效果有限。

解決干擾問題 訊號/電源完整性是關鍵

真正的解決之道是將訊號完整性(Signal Integrity, SI)及電源完整性(Power Integrity, PI)做好,待解決好SI與PI後,再將SI與PI之間的隔離做好,使RF不受雜訊、串音、共模影響,關鍵在於差動訊號對的分組處理,電源接地迴路路徑的分組處理,及RF訊號與接地饋線的分組處理,在SI、PI、RF的接地分隔,藉此形成各自獨立的模塊,降低EMC電磁波輻射,避免產生RFI射頻干擾與EMI電磁波干擾。

但要做到上述的電路優化,傳統的靜態SI與PI模擬分析根本無法看出干擾源位置,而須借助更高端的動態SI與PI模擬分析,主要關鍵是在於在SI模擬分析中,普遍將VBUS視同GND做為參考感應位置,但因為VBUS與GND本身的電位差距甚大,所以,將VBUS視為GND的做法並非正確的做法,因為靜態模擬分析為理想狀態,而動態模擬分析較為接近實際狀況。因高速傳輸與大電流快充的興起,在可見的未來高低頻訊號處理必然成為趨勢。

(本文作者為岱煒科技研發中心技術長)

首圖來源:Moshi