RISC-V(念做Risk-Five)是一種起源於加州大學柏克萊分校(UC Berkeley),具有高品質(High Quality)、無授權費(No License Fee)、無權利金(No Royalty)等主要特點的精簡指令集運算(RISC)指令集架構(ISA)。

RISC-V標準是由非營利性組織RISC-V基金會維護。RISC-V ISA適用於從微控制器(MCU)到超級電腦(Supercomputer)的各種運算體系。在現今的RISC-V業界已經有很多商用及開源的中央處理器(CPU) Core,產業界與學術界都在迅速採用該指令集架構,更重要是獲得越來越多高速成長且使用者共用的軟體生態支援。更有趣的是,RISC-V生態是一個不斷演進、開放、靈活共生的社群型「生命體」。

相較私有化ISA RISC-V究竟有何不同

RISC-V究竟有何不同之處,如下:

比起其他商用ISA,RISC-V ISA更小。

明確地分離了使用者(User)及特權(Privileged)ISA,而且具有避免對微架構(Micro-architecture)及技術依賴性的特徵。

小的標準化基本ISA,在此基礎上具有多種標準的擴展。此外,用於大量Opcode Space的Sparse和變數長度指令編碼(Variable-length Instruction Encoding)。

基本及標準擴展ISA是固定不變的,而且透過可選擴展而非更新ISA的方式來增加指令。

由領先的產業或學術專家以及軟體開發者組成的社群進行設計。

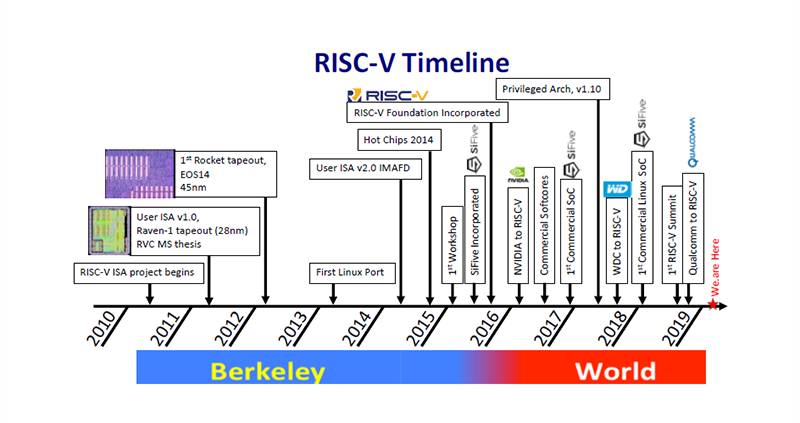

從2015年8月成立RISC-V基金會後,RISC-V ISA正式從加州大學柏克萊分校開始走向全世界,在世界範圍內得到了極大的關注,圖1為RISC-V的演進過程中重要的事件。

圖1 RISC-V重要演進過程

圖1 RISC-V重要演進過程

因為擁抱開放、自由 RISC-V越來越流行

工程技術人員有時候是見樹不見林,RISC-V流行的趨勢不是因為在一些Benchmark方面有10%的提升,或者在某一些應用情況下能節省30%的功耗。這個趨勢的原因是新的商業模式的正在改變一切,新的模式是開發者先選擇ISA,然後選擇一個處理器(Processor)的合作夥伴或者乾脆選擇自行開發,在此基礎上可以自主選擇是否添加自己的指令擴展甚至做功能裁剪。

摩爾定律(Moore's Law)正逐漸在失效,因為晶片的性能、功耗及面積(PPA)的提升,不再僅僅依靠晶片製造工藝的持續演進,從英特爾(Intel)、超微(AMD)等傳統處理器提供商最近新產品的發布就能明顯感覺得到。當前PPA的提升很多都是基於晶片架構的創新,各種人工智慧(AI)處理器就是最好的例子,當前的AI晶片的架構上有很多輔助處理器(Coprocessor),但似乎不需要在一顆晶片上有好多不同的ISA的輔助處理器。據統計,今天的系統單晶片(SoC)平均採用六種不同的ISA。如果採用RISC-V ISA的輔助處理器,工程人員可以自由實現不同特定應用的輔助處理器,添加不同的功能和標準擴展指令,而全棧軟體依然可以在其上相容運行。

在ISA發展的歷史上,也出現過開源的ISA,例如很多年前昇陽(Sun)開源了Sparc ISA,但是沒有像現在RISC-V那麼受到關注和應用,因為在那個時代,摩爾定律依然有效,市場還是沒有對新的計算體系架構有那麼多的需求。

在現實中,圍繞著私有ISA所建立起來的軟體生態,絕大部分都是ISA所有公司之外的開發者或公司完成的,而不是擁有ISA的公司自己實現的。

一個優秀ISA的定義和不斷優化,不是靠一家公司的技術專家和經驗積累能夠完成的,通常需要巨量的工作和知識經驗。對於一個開放、自由的ISA,會有很多公司甚至是個人參與標準的制定、設計和維護提升,而不會像英特爾、超微、安謀國際(Arm)那樣,只有他們公司的人員才能進行其私有ISA的設計和相關工作。

即便是某一家公司設計出ISA,但是ISA的驗證工作量是難以估量的,所面對的現實狀況是,在看來像英特爾這樣的大公司所採用的如此成熟的私有化ISA設計出的處理器,依然會有很多嚴重的ISA層面的漏洞,這是因為單一公司的技術團隊是無法完成所有的驗證工作,而且私有的ISA很難得到開放社群共同、透明的驗證。就像在開源軟體的生態中,公司少數幾個人也能夠利用社群中已經成熟的開源的軟體設計或模組,這樣就能大大縮短設計開發週期與成本投入,真正地推動新應用的實現。

如果一個ISA是私有的話,人們無法保證它的延續性,它將與擁有它的公司所綁定,如果這家公司不再存在,那麼大部分情況下這個私有化ISA也將隨之失去延續性,Alpha以及VAX ISA就是一個非常好的例子,它們隨著迪吉多(DEC)的消亡而失去延續性。

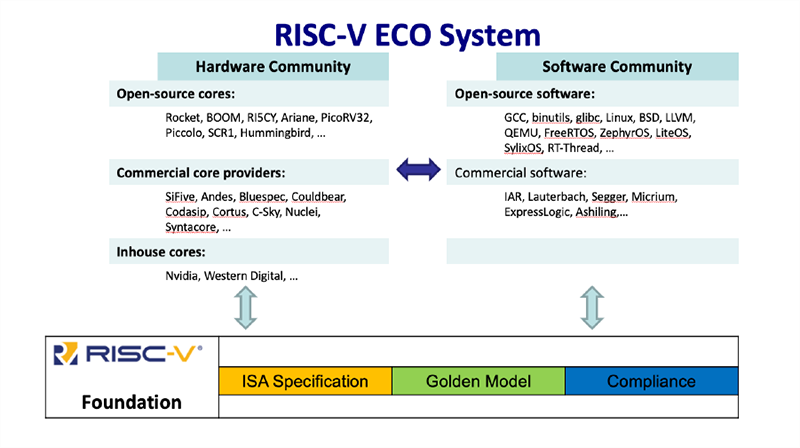

所以綜上所述,看不出除了出於智慧財產權保護的原因之外,從技術的角度來講沒理由需要一個封閉的私有化的ISA。必須要注意的是,ISA和Processor IP是有區別,不能等同來看待。為什麼需要用那麼多不同的ISA,特別是那麼多不同的私有化ISA呢?為什麼不考慮使用同一個自由、開放的ISA用於所有的應用呢?而這就是RISC-V ISA越來越流行的原因。RISC-V的生態現狀就如圖2所示。

圖2 RISC-V的生態現狀

圖2 RISC-V的生態現狀

RISC-V ISA設計認證及擴展

RISC-V的生態是如何透過基金會營運組織和社群討論及共同開發的方式進行演進的,這也決定RISC-V ISA所獲得的參與度必將飛速成長。以下透過RISC-V基金會運作方式進行分別說明。

RISC-V ISA標準的形成,總結來講其實就是「大家一起來,不斷反覆運算反覆實踐,最終一起標準化」,過程步驟如下:1. 定義需求;2. 收集輸入,舉行會議,「白板級」參數設計,完成並公開發布穩定的標準初稿;3. 根據標準初稿進行設計硬體實現;4. 根據實施的硬體進行軟體實現;5. 進行軟硬體的聯合評估,可能須要重新回到以上步驟2進行多次反覆運算;6. RISC-V技術研究小組決定推進該ISA標準的批准工作;7. RISC-V技術委員會將該ISA標準提交RISC-V基金會董事會;8. RISC-V基金會董事會進行投票批准;9. RISC-V社群設計按照批准後的標準進行實現,並進行合規性測試;10. 最終完成ISA標準的替換。

滿足AI邊緣實現各類應用 處理器需求大幅提升

機器學習(ML)在當前的AI應用中快速地發展,系統也會增加更多智慧功能。但是在雲端的系統(例如資料中心)和邊緣系統(例如IoT設備)對運算能力的需求是不同的,在雲端可以採用大型高效的繪圖處理器(GPU)來提供千萬億次的浮點運算能力,Google的張量處理器(Tensor Processing Unit, TPU)3.0的單晶片的浮點運算能力遠遠超過100 Petaflops(一千萬億次浮點運算),用於深度學習(Deep Learning)或者進行推理。但是,在邊緣系統中,就很難採用功耗高的類似GPU或TPU的方案。系統開發人員必須要考慮採用效率更高的解決方案,除了滿足計算精度問題外,必須考慮實際應用場景對設備功耗、安裝尺寸以及綜合成本的問題。

將AI優勢擴展至邊緣設備,取代以雲端為基礎的資源,能夠大幅降低功耗,同時縮短反應時間。此外,本地資料儲存和處理不僅提高安全性,更節省寶貴的頻寬。透過將AI整合至邊緣設備中,即使在網路關閉以節省功耗的情況下,也能實現即時工作的智慧功能。

低功耗解決方案可於網路邊緣實現各類應用。例如,智慧門鈴可透過嵌入式AI功能自動進入待機模式,直到感應到有人出現;智慧電視在沒有觀眾觀看的情況下自動關機;AI安防攝影機,只在出現入侵者時才發出警報,而不是因為自己家裡或是鄰居家裡狗、貓等其他動物經過誤報。

在邊緣設備的晶片中,很多都是以神經網路(NN)硬體進行機器學習,這樣就有需求為神經網路配置硬體加速器,RISC-V CPU中的算數邏輯單元(ALU)就可以達到這樣的需求。在這樣的應用中,RISC-V體現出非常精簡高效的基礎指令的特點,用最少的資源進行運算。在基礎指令之上,開發人員通常採用各種標準的ISA Extension。例如,採用向量擴展ISA(Vector Extension ISA)來增強RISC-V處理器,神經網路之矩陣運算的效率是透過從RISC-V ALU傳輸矩陣資料,再透過Vector Extension ISA減少甚至消除迴圈、記憶體存取(Memory Load Store)以及位址映射(Address Mapping)產生的成本等方法來提升。

邊緣運算安全至關重要 RISC-V提供可靠整體方案

安全(Security)對於邊緣計算而言至關重要。那麼RISC-V能否為邊緣運算(Edge Computing)提供可靠安全的整體方案?一個安全的RISC-V系統究竟有哪些元件?還有哪些新的安全技術?

當前RISC-V的體系中有哪些安全性群組件?首先,RISC-V ISA中有三種模式,分別為用戶(User)、管理員(Supervisor)以及機器(Machine)模式。而其實體記憶體保護(Physical Memory Protection, PMP)採用基礎加邊界的方案,沒有轉換,除非系統重置,否則禁止所有的存取,包括所有模式下程式對鎖定記憶體區域的存取。此外,RISC-V有兩個保護邊界,第一個為在Supervisor和User模式之間具有保護,第二個為PMP機制保護所有的存取。最後,其位址轉換和保護,是基於標準頁面的方案。

那RISC-V有那些新的安全技術呢?傳統計算的安全性不夠,因為幾乎所有的程式都能獲取到程式碼和資料,編譯器和連接器將源碼模組合併成單一的二進位檔案;各個功能模組(如Stack、Heap、Buffers)透過共用存儲單元來通訊;任何位元(Bit)的源碼都能得到任何Bit的資料;而且,任何一個錯誤指令能夠癱瘓整個系統,例如DOS。

而RISC-V的安全技術組(Security Technical Group)中的成員HEX Five,提出了一個更好的方法,也就是多區域信任執行環境(Multi-domain Trusted Execution Environment),該技術也是基於RISC-V標準擴展指令。在2018年,Hex Five先後宣布完成了基於整合SiFive RISC-V CPU以及Andes RISC-V CPU的晶片開發出類似Arm TrustZone的Trusted Execution Environment。

搶占邊緣運算領域 RISC-V應用案例說明

接下來,介紹一些RISC-V在邊緣運算中的實際應用案例。

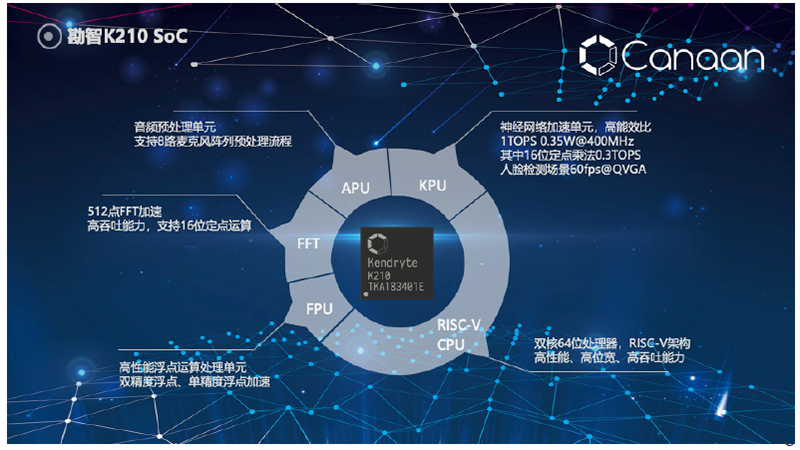

Kendryte K210晶片是一個非常典型的RISC-V應用於邊緣運算的案例。其應用包括目標檢測、目標識別、聲源定位、聲場成像以及語音辨識。該系統單晶片的主要組成模組(圖3)包括:RISC-V CPU、神經網路加速單元(KPU)、音訊處理器(APU)、快速傅利葉轉換加速(FFT)、高性能浮點運算處理單元(FPU)。

圖3 Kendryte K210晶片主要組成模組

圖3 Kendryte K210晶片主要組成模組

圖片來源:Canaan Creative

Kendryte K210借助RISC-V的開源生態,支援多種即時操作系統(RTOS),包括FreeRTOS、RT-Thread、XBoot、Zephyr、SylixOS等。

BM1880是一個輔助處理器,在實際應用時需要與類似攝影機系統單晶片這樣的主控端(Host)進行連接,資料透過通用序列匯流排(USB)或者乙太網路(Ethernet)進行傳輸,Edge推理(Inference)可以在BM1880上完成。應用場景主要是攝影機、機器人(Robot)和無人機(Drone)。

進一步分析,RISC-V的模組化,靈活配置的ISA究竟能夠給BM1880帶來什麼好處?共有以下四個理由,包括:選擇M Extension ISA是因為,M Extension提供了整數乘法及除法運算能力,能提供高性能的乘法及除法運算的硬體加速功能;選擇A Extension則是因為應用的軟體以及作業系統需要CPU支援原子操作(Atomic Operation);選擇同時支援F及D Extension是因為須要用到單精確度和雙精度浮點運算能力;而採用C Extension,是因為能夠透過該壓縮指令擴展,在編譯器編譯代碼時得到更高的代碼密度(Code Density)和更高的運行效率。

向量擴展ISA標準通過在即 RISC-V未來發展可期

RISC-V ISA在當前的行業應用中,主要是嵌入式應用為主,在嵌入式應用中,更以用於邊緣運算設備為主,邊緣設備的AI及Inference深度結合的設計架構,在未來很長一段時間內都將是保持高增長的趨勢,這是RISC-V技術與邊緣運算最好的結合點。可以預期,在2019年RISC-V將Vector Extension ISA標準批准通過後,有更多的Core以及軟體出現,將更有利於邊緣運算晶片PPA和靈活度的提升,一定將助力其更上一層樓。

(本文作者任職於SiFive)

首圖來源:AdobeStock