行動市場在這幾年來的成長十分迅速,使得消費者對儲存媒體的需求也急速增加。由於NAND型快閃記憶體(Flash)具有資料非揮發性、省電、體積小,以及無機械結構等特性,所以非常適合內建於包括手機等各種可攜裝置中。

目前,低密度奇偶校驗碼(Low-Density Parity-Check, LDPC Code)已經成為糾錯碼領域一個新的研究熱點,具有巨大的應用潛力,適合在未來高速數據傳輸的通訊系統中使用,並可以廣泛應用於高空通訊、光纖通訊、行動通訊、無線通訊、衛星數位視訊等各個領域。

香農定理(Shannon's Theorem)為通訊的可靠性傳輸提供了理論基礎,但並無提出一種可實現又能達到最佳性能的編碼方法。後來相繼出現了多種編碼,包括各種代數碼和卷積碼,但是隨著高速資料傳輸的通訊系統越趨複雜,相對的編碼方法也需要有更強的方式去執行。目前,錯誤更正碼(Error Correction Code, ECC)必須被用在NAND Flash存取其間糾正錯誤,以增加存取的可靠度。在眾多ECC選擇中,LDPC具有極佳糾錯能力可以逼近香農的理論值,此技術也隨著記憶體的快速演變與市場成長,應用面逐漸擴大。

強化解碼方式的必要性

資料在傳輸過程中可能因為傳輸媒介的可靠度不佳,或外在環境因素的干擾,而遭到破壞,此時,必須要有處理資料傳輸錯誤的方法,將錯誤的資料更正。ECC的作用即是盡可能還原這些遭受破壞的資料,經常被應用於通訊與儲存系統領域。現今無線通訊技術快速地發展,但是雜訊卻仍無法從環境中驅除,唯有仰賴通道編碼及解碼技術,將原始資料正確地還原,因此,資料傳輸的高正確性一直為通訊傳輸技術的重要課題,而在儲存系統的應用上,也是相同的道理。

一般來說,寫入NAND Flash的資料都會根據一個錯誤更正碼來編碼,從中所讀取的資料也會經過對應的解碼程序。然而,錯誤更正碼的糾正能力有其限制,並且資料發生錯誤的機率會隨著使用壽命一起改變。若NAND中一個實體抹除單元的抹除次數增加了,則發生錯誤的機率也會增加,可能會導致無法更正錯誤位元的情形。因此,如何增加解碼的更正能力,一直是此領域技術人員所關心的議題。

群聯電子控制晶片的LDPC+DSP技術,即是利用數位信號處理(DSP)模組,計算出合適的可靠性訊息和轉譯的訊息轉換成對數似然比(Log-likelihood Ratio)。相較於傳統的LDPC,對於不穩定位元的處理,LDPC+DSP提高了NAND Flash儲存系統的可靠性。簡單來說,DSP模組被用來優化解碼流程,以利改善軟位元(Soft Bit)解碼的校正能力。

最佳讀取電壓與對數似然比

現行NAND Flash的ECC最常使用的為低密度奇偶檢查碼LDPC與BCH兩種,其中LDPC又涵蓋硬解碼(Hard Decoding)與軟解碼(Soft Decoding),後者會對NAND Flash進行額外的讀取,以獲得更多的通道訊息並且以機率統計的方式將LLR Table送回LDPC編碼,進而產生更大的解碼能力。然而在現行的技術下,LLR Table為NAND供應商所提供的統計數據,因此,當通道結果與預期結果不相同時,LDPC的更正能力會大幅下降。

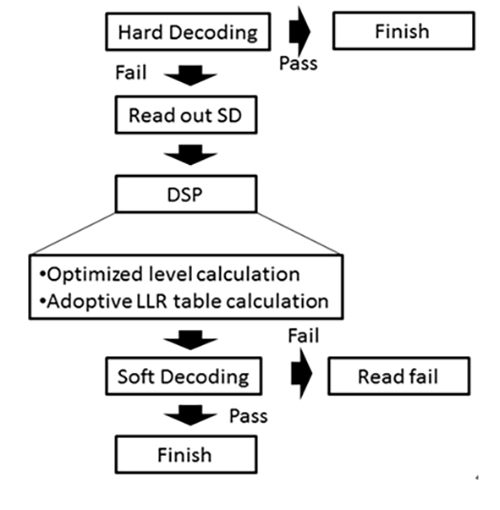

為了解決上述問題,群聯電子的解決方案為開發一種解碼方法及記憶體控制電路單元(圖1),可搜集額外的通道資訊作為錯誤更正的依據,做Soft Decoding前先透過DSP強化後再進行解碼演算,快速的計算出最佳讀取電壓,並且再讀取一次軟信息(Soft Info),配合動態的計算LLR Table以得到最佳的解碼結果。

|

| 圖1 群聯電子LDPC解碼方法及記憶體控制電路流程 |

此解決方案著重於下列兩點:

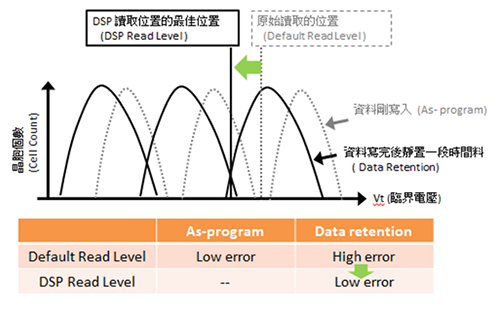

(1)以Soft Info計算出最佳的讀取電壓

在NAND Flash中,資料寫完靜置一段時間後,臨界電壓(Vt)有機率會飄移進而導致後續資料讀取會有錯誤產生,因此,此技術作法可在資料寫入後,將會計算出最佳並優化讀取的電壓,以降低讀取錯誤資料發生的比例,如圖2所示。

|

| 圖2 DSP讀取最佳位置 |

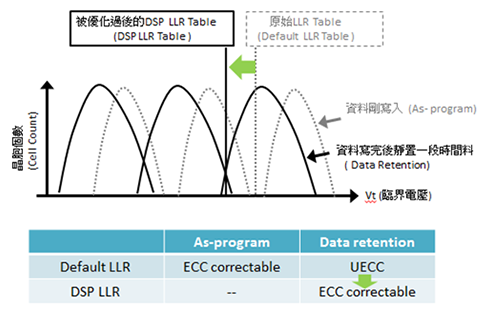

(2)以Soft Info計算出最佳對數似然比LLR Table

若是在資料剛寫入且ECC正常的情況下,在靜置一段時間後會導致ECC難以被糾正,此時,透過本技術被優化過後的值所產生的LLR Table,將會讓此ECC還原至正常狀態,如圖3所示。

|

| 圖3 優化過後的DSP LLR Table |

LDPC+DSP實際應用的優勢

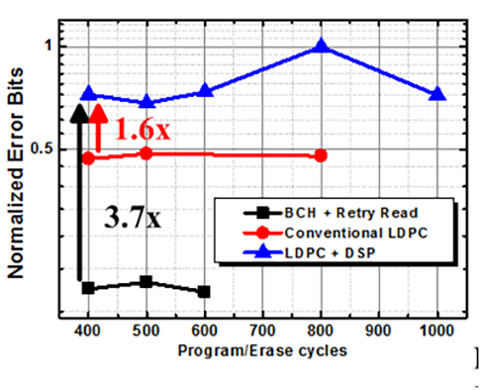

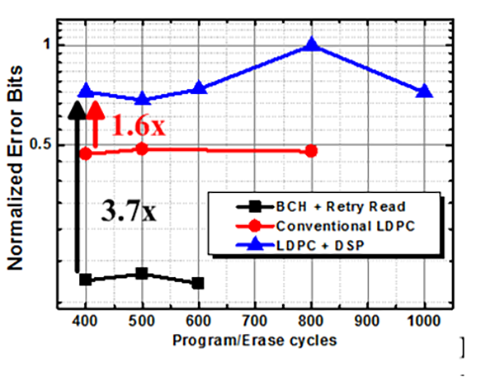

根據實驗結果,以20nm的Triple-Level Cell(TLC)NAND Flash為例,加入DSP技術後,其資料的可靠度相較於傳統LDPC技術成長了二至五倍,甚至比BCH碼技術高20倍,如圖4所示。

|

| 圖4 LDPC+DSP技術資料錯誤率與其他技術相較 |

平均可糾正錯誤位元測試結果顯示,所提出的誤差校正糾錯能力比BCH高3.4到3.9倍,和傳統的LDPC比約高至1.6到2.1倍。如圖5所示。

|

| 圖5 LDPC+DSP平均可糾正錯誤位元測試結果 |

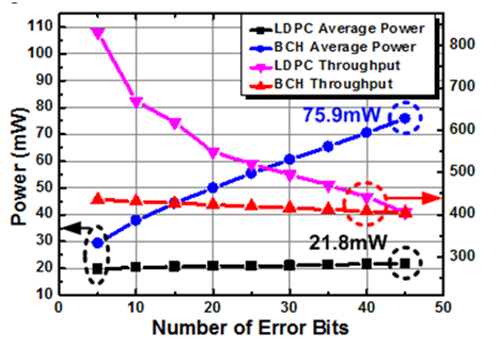

另外,本技術解碼處理能力可達到400MB/秒,而在40nm CMOS技術中若有45個bit errors產生時,電力消耗率僅為21.8mW,相當適合低功耗的行動記憶體應用如eMMC、UFS、SD卡,如圖6所示。

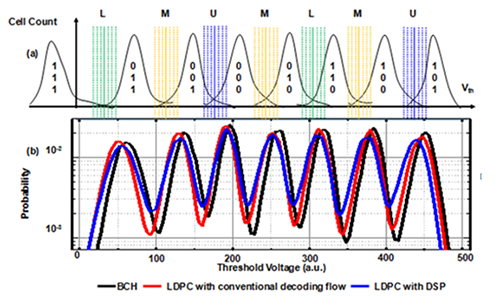

用20nm的TLC NAND Flash來評估此技術對其結構的可靠性改善:如圖7a所示,該晶片的儲存單元包含8個區分,其狀態為閾值電壓(Vth);圖7b則顯示出對應的BCH碼、傳統LDPC碼與LDPC+DSP過程中可校正的Vth分布,結果顯示LDPC+DSP能夠糾正絕大多數Vth重疊機率較高的分佈,比傳統的BCH或LDPC來得更佳。

|

| 圖6 不同技術的錯誤碼數量與耗電量關係 |

|

| 圖7 以20nm的TLC NAND Flash評估LDPC+DSP技術對結構的可靠性改善 |

2017年NAND Flash大廠紛紛轉進3D TLC為主流,應用商機日益龐大,然而記憶體的製程日趨變異,產品複雜度遞增,搭載的控制器技術也需日益精進,需要內建更強大的電路與韌體,提升了設計上的困難度。ECC的優劣決定了NAND Flash的耐用度,關係到成品如eMMC、UFS、SSD等在市場上的競爭力,因此,以DSP強化控制器的解碼能力,搭配最新製程較低成本的TLC甚至未來的Quadruple Level Cell(QLC),提升其效能、可靠度與使用壽命以符合終端需求。

(本文作者為群聯電子產品專案管理部處長)