隨著多媒體內容日益豐富,總資料流量也持續增加,設備製造商正面對著前所未見的工程挑戰與機會。他們必須建造新一代設備,以處理不斷快速增加的網路流量,這些流量與過去引領基礎設施設計典範的語音和資料流量有很大差異。

1970年代電腦革命後出現下列幾個趨勢,共同推動這項轉變。首先,是純語音流量轉變為語音及資料流量,這個趨勢幾十年前就出現,目前還在持續變化中;其次,是在現有語音和資料流量外,又出現以串流媒體為主的多媒體流量,這個趨勢可從電信公司開始提供語音、視訊和資料服務看出;再者,是從固定位置服務演進到家庭服務,再到行動服務,有線基礎設施曾經歷的從語音到資料再到媒體的演進過程,如今又在無線基礎設施重演。這三種趨勢也帶動從線路交換式傳輸轉移到封包交換式傳輸。

語音時代不需要太多的電信訊號處理,通常僅限於回音消除、資料數據機線路調節,以及交換式線路資料的調變與解調訊號處理。現在則有數十種不同的訊號處理演算法,範圍涵蓋音訊、視訊和資料流量的數位編碼/解碼及壓縮/解壓縮。簡單來說,電信基礎設施不僅要處理更多資料,這些資料所需的訊號處理作業也大幅增加。

電信基礎設施顯然需要更強大的效能,才能應付成長快速的處理需求。要達成這項目標的方法之一是提高數位訊號處理器(DSP)速度,但這種解決方案有幾個缺點。首先,晶片時脈速度的提升有其極限;其次,資料流量是以指數成長,而不是線性,這表示效能需求很快就會超過晶片所能達到的最高時脈速度。另一個重要問題是基礎設施設備都採用機架安裝,體積和散熱都會受到嚴格限制。機架空間通常不會變大,只會變得更小,因此高時脈速度所產生的龐大散熱問題終將使晶片速度達到極限。未來,電路板提供更高效能的能力將受到電路板功率預算、建築物屋齡和位置、以及基礎設施設備的安裝機架等因素限制。

利用交換式架構提升DSP效能

電信設計工程師面臨一項艱鉅挑戰:他們必須把更高效能整合至更小空間、提高通道密度和處理種類日益繁多的媒體內容,同時維持流量彈性和成本效益。為了因應這項挑戰,DSP也在不斷進步,使晶片設計人員必須將前述趨勢轉換為具體的元件功能和架構。

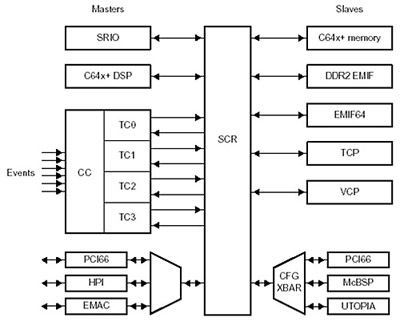

要同時達成效能與功耗目標,最好的方法是盡可能在具有最佳化處理引擎和高效率I/O的低電壓晶片上執行處理作業;該晶片必須包含超高效能和有效率的資料傳輸能力,才能處理不斷增加的原始資料。此類架構若能透過交換式中央資源(Switched Central Resource, SRC)--包括主控端(Master)和受控端(Slave)的交叉架構,把DSP中央處理器、DSP周邊、協同處理加速器和內部記憶體等處理元件相連接,就能以高效率傳送大量資料,德州儀器(TI) TMS320C6455 DSP便是基於這種架構的一個例子(圖1)。

|

資料來源:德州儀器

圖1 TMS320C645x功能方塊圖 |

SRC左方的任何主控端裝置都能直接連到右方的任何被動端裝置。主控端包括DSP中央處理器、一組串列快速(Serial Rapid IO, SRIO)介面、四個傳輸控制器(TC)和一個將PCI、硬體平台介面(HPI)和乙太網路媒體存取控制器(EMAC)等三種主控端周邊連接到交換式中央資源的交叉連接埠(Crossbar Port)。受控端裝置包括DSP記憶體、DDR記憶體介面、Turbo協同處理器(TCP)、Viterbi協同處理器(VCP)和將許多周邊連接到交換式中央資源的交叉切換電路(Crossbar)。

這種架構快速而有效率,因為交換式中央資源能在主控端和受控端間提供真正的並行資料傳輸。舉例來說,PCI和DDR EMIF的連接就與PCI166和DSP中央處理器之間的連接各自獨立,資料傳輸也是完全並行。當多個主控端想存取同一受控端時,就由交換式中央資源進行仲裁,系統設計人員則能設定主控端的優先權。

演算執行架構要求較高

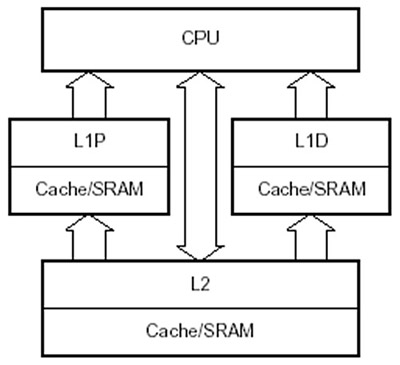

中央處理器和記憶體間的指令及資料移動對演算法執行十分重要。TMS320C6455 DSP記憶體系統如圖2所示,在中央處理器和記憶體之間使用256位元寬的資料匯流,並以直接記憶體存取(DMA)架構為基礎提供兩層快取記憶體,故能大幅提高中央處理器和記憶體之間的資料傳輸效率。

|

資料來源:德州儀器

圖2 TMS320C64x+ CPU內部記憶體 |

這類架構還必須提供高效率的晶片內建處理引擎。一種較有效率的作法是把協同處理器整合至晶片,讓需要高效能的特定功能執行更快。舉例來說,圖1所示的TMS320C6455 DSP就整合了一個Viterbi協同處理器和Turbo協同處理器。

晶片內部處理作業結束後,開發人員仍須從晶片傳送大量資料到電路板,最後再送到電信傳輸媒介。這裡顯然應使用高速I/O,但在前述包含各種不同裝置的基礎設施裡,想要選擇最好的處理方式其實並不容易。

最好的作法是提供數種不同的高效能I/O介面,做為電路板上晶片之間的介面。SRIO是異質多處理器(Heterogeneous Multi-processor)元件之間的最佳通訊介面,因為其高產出訊息傳送機制能達到95%的頻寬使用率(4×序列雙向鏈路的速率高達10Gbit/s)。

外部記憶體傳輸最好使用32位元DDR2記憶體控制器。同樣的,66MHz PCI匯流排介面是連接晶片外部裝置的理想選擇,1Gbit/s乙太網路媒體存取控制器最適合處理電路板內部和對外的IP流量,異步傳輸模式(ATM)連結則可使用專為電信應用所發展的通用測試與作業實體層介面(UTOPIA 2)。

效能評比提升至電路板層級

儘管許多新架構都提供更好的平行性和其他先進功能,使DSP處理能力大幅提升,但電路板設計人員仍能以高效率和高效益的方式將多顆DSP整合至一張電路板,進一步增強系統表現。SRIO高速連結則能讓這項工作更容易,因為從DSP軟體的角度而言,處理多個DSP之間的資料流動與處理一個DSP所產生的資料並沒有太大不同。

傳統系統會將語音和資料流量分開,但事實上這種作法的效率很差,因為時間日期和許多其他參數都會影響流量,如此一來,有時會造成處理能力閒置和頻寬使用率過低。設計人員則能透過新架構讓系統利用單顆元件處理所有流量,同時確保其效率更高。

Surf的SurfRider產品線就是匯集多種功能的解決方案之一,這項產品線提供低成本電路板所需的硬體與軟體,還能針對特定的系統流量需求進行最佳化。SurfRider/AMC最多能將八顆DSP整合至一片電路板,資料吞吐率高達10Gbit/s,並能將多達八張的電路板安裝到先進電信運算架構(Advanced Telecommunications Computing Architecture, ATCA)或MicroTCA機架。

藉由提高DSP內部的並行處理能力,並在DSP、晶片外部記憶體和其他元件之間使用超高速互連機制,晶片設計人員已發展出新一代基礎設施電路板和閘道器系統。這些系統能讓電信公司同時提供語音、資料和媒體服務,並能彈性適應不同類型的流量和負載。

多核DSP具有成本及低功耗優勢

然而科技發展並沒有終點,儘管過去幾年有大幅度的進展,但仍有改善空間。晶片及電路板設計人員當然能採用許多顯而易見的作法,例如將更多協同處理器整合至晶片和增加平行性,但他們也了解在電路板上使用多顆DSP的成本仍然很高。

現在也有人把多個DSP核心整合到一顆晶片。多核DSP的成本不但低於使用多顆DSP晶片,還能提供許多其他優勢;例如共用記憶體的多個核心可以使用較慢的時脈和更低的電壓,進而降低每個通道的耗電量。這在傳送封包化語音流量的多個通道上特別明顯,因為其處理和記憶體需求都少於視訊資料流量。

多核心還為行動電信基礎設施和新興的全球微波存取互通介面(WiMAX)應用帶來許多機會。因為無線傳輸需要複雜的正交多頻多工(OFDM)數據機,這類數據機需要更快的1GHz多核處理器,而非網路語音通訊協定(VoIP)微處理器的500MHz,以及Turbocore和Viterbi等強大的硬體加速與協同處理器。值得注意的是,功耗限制可能會減少每個晶片所能整合的核心數目。隨著電信產業進入語音、資料和視訊的三合一服務時代,業者也要面對幾年前還無法解決的許多問題。這類應用的效能需求當然越來越高,但是具有創意的DSP晶片設計人員也會發展出多核心和以DSP為基礎的系統單晶片(SoC),確保DSP仍能滿足未來系統的效能、功耗、彈性和每通道成本要求。

(本文作者任職於德州儀器)